半導(dǎo)體對各行各業(yè)都有著潛移默化的影響,其重要性不言而喻。現(xiàn)如今半導(dǎo)體已徹底改變了我們的業(yè)務(wù)形態(tài),無論是汽車行業(yè),還是物聯(lián)網(wǎng)、通信和高性能計(jì)算等等。然而隨著對高性能和即時(shí)滿足需求的增加,SoC 的復(fù)雜性也相應(yīng)提高。隨著數(shù)以百計(jì)的 IP 被集成到 SoC 中,漏洞變得越來越常見,修復(fù)也變得愈加困難。SoC 級的驗(yàn)證過程所需的時(shí)間不斷增加,從而造成了流片計(jì)劃的延遲。伴隨著幾何尺寸的減少及門數(shù)的增加,要在有限的預(yù)算和規(guī)定時(shí)間內(nèi)檢測漏洞變得越來越困難。

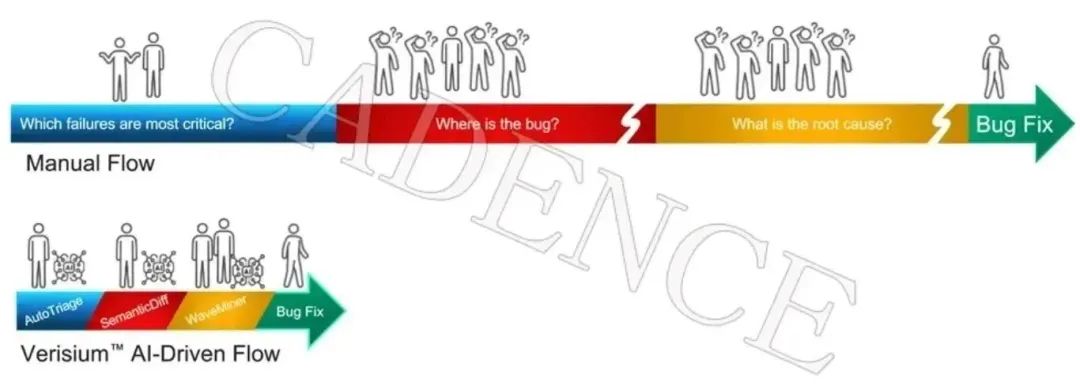

SoC 設(shè)計(jì)工程師往往需要花費(fèi)超過 70% 的時(shí)間用于驗(yàn)證,而檢測單個(gè)漏洞平均需要 16-20 個(gè)工程時(shí)。讓我們試想一下,一個(gè)設(shè)計(jì)中如果有 1000 個(gè)漏洞,那將造成多大的影響!

是時(shí)候采取行動(dòng),簡化 SoC 設(shè)計(jì)流程,節(jié)省寶貴的資源以確保項(xiàng)目及時(shí)完成了。只要通過實(shí)現(xiàn)自動(dòng)化部署、新的工具和基于人工智能的方法就可以顯著提高生產(chǎn)力和驗(yàn)證吞吐量。利用基于人工智能的方法,SoC 設(shè)計(jì)和驗(yàn)證工程師可以更快地檢測錯(cuò)誤,縮短驗(yàn)證時(shí)間,并在多個(gè)引擎和運(yùn)行中優(yōu)化性能。帶有人工智能的 EDA 工具更是可以幫助芯片制造公司更快、更高效地實(shí)現(xiàn)目標(biāo)。SoC 設(shè)計(jì)和驗(yàn)證中的人工智能不再是天方夜譚而是必需品,我們將通過它極大地提高產(chǎn)品質(zhì)量,同時(shí)幫助減少開發(fā)時(shí)間和成本。

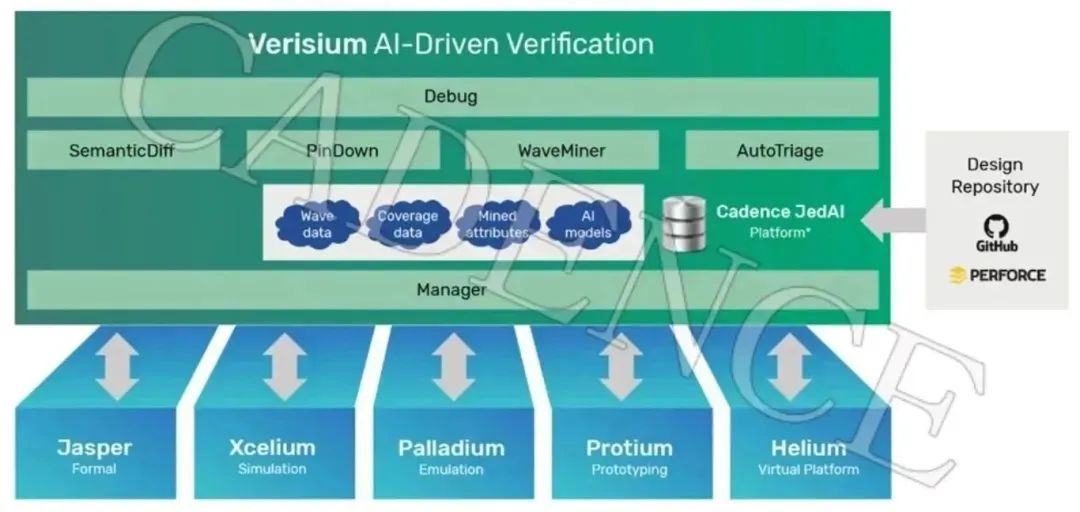

Cadence 正在通過使用 Verisium(人工智能驅(qū)動(dòng)的驗(yàn)證平臺)徹底改變芯片驗(yàn)證。該平臺能利用大數(shù)據(jù)提高整體驗(yàn)證吞吐量,特別是在調(diào)試方面。Verisium 建立在 Cadence Joint Enterprise Data and AI(JedAI)Platform 上,可以匯總包括波形覆蓋、源代碼、日志文件等在內(nèi)的驗(yàn)證數(shù)據(jù)。

Verisium platform 在日志文件、RTL 和測試平臺迭代、版本控制和波形上使用人工智能來加速和輔助調(diào)試,從而將手工工作量減少多達(dá) 32 倍。Verisium Debug platform 還提供了一種名為 VWDB 的新的波形格式,速度較以往的格式有極大幅度的提升。提高整體驗(yàn)證吞吐量的關(guān)鍵是清楚所有數(shù)據(jù)的位置,進(jìn)而對其進(jìn)行利用、控制并管理。Verisium 可加快對設(shè)計(jì)錯(cuò)誤根本原因的分析,提高覆蓋范圍,并優(yōu)化復(fù)雜 SoC 的驗(yàn)證計(jì)算服務(wù)器資源。

Cadence 專注于持續(xù)創(chuàng)新,利用 Verisium AI-Driven Verification Platform(人工智能驅(qū)動(dòng)的驗(yàn)證平臺 Verisium)提供了一系列包括引擎、驗(yàn)證 IP 和 Verisium 在內(nèi)的工具。通過借助 Auto Triage、Semantic Diff、Pin Down 和 Wave Miner 等應(yīng)用程序,Verisium 可以加速并協(xié)助調(diào)試,減少工程師在故障分類和調(diào)試上的時(shí)間。因此使用 Verisium 平臺的 SoC 調(diào)試可將生產(chǎn)力和整體驗(yàn)證吞吐量提高 10 倍。

Verisium 如何提高

調(diào)試效率和驗(yàn)證吞吐量?

Verisium Debug 工具是一款高級的調(diào)試工具,旨在幫助設(shè)計(jì)工程師、集成商和驗(yàn)證工程師探索、分析和調(diào)試復(fù)雜的設(shè)計(jì)和測試平臺,而無需考慮它們的規(guī)模、語言或來源。該工具提供了幾種主要模式,如探索模式(仿真前)、后處理模式(仿真后)和交互模式(仿真中)。在這些模式中,用戶可以執(zhí)行如下各種任務(wù):

●控制仿真器執(zhí)行步驟并執(zhí)行交互性調(diào)試

●記錄仿真結(jié)果后執(zhí)行后處理調(diào)試

●對 Palladium 仿真結(jié)果執(zhí)行調(diào)試并支持按需信號擴(kuò)展

●調(diào)查仿真進(jìn)入特定狀態(tài)的可能原因

●過濾測試環(huán)境的全部報(bào)文

●在 UPF 環(huán)境下調(diào)試功耗內(nèi)容

Verisium Debug 工具的優(yōu)勢

使用 Verisium 對復(fù)雜設(shè)計(jì)和測試平臺調(diào)試比傳統(tǒng)工具更快、更高效。Verisium Debug 工具的部分主要優(yōu)勢包括:

1

可擴(kuò)展性

2

可操縱性

3

SmartLog 有助于定位產(chǎn)生報(bào)文的層次目標(biāo),并向波形發(fā)送信息

4

驅(qū)動(dòng)追蹤——很多 Verisium Debug 窗口中的直接訪問箭頭圖標(biāo)允許您調(diào)用驅(qū)動(dòng)追蹤

5

連接性分析顯示原始被追蹤信號和該信號驅(qū)動(dòng)信號之間線路連接,并允許對追蹤路徑進(jìn)行導(dǎo)航

6

根本原因分析(RCA)有助于診斷故障的根本原因

Verisium Manager 是一個(gè)真正卓越的工具,它為驗(yàn)證規(guī)劃、故障分類、覆蓋收斂和回歸管理提供了一系列可靠的功能。它的特點(diǎn)在于具有能聯(lián)合企業(yè)數(shù)據(jù)和人工智能(JedAI)數(shù)據(jù)以及分析平臺的強(qiáng)大能力。這種集成方式將對驗(yàn)證過程進(jìn)行無以倫比的優(yōu)化,使其成為尋求簡化操作和最大限度提升生產(chǎn)力的芯片制造商的寶貴工具。憑借其集成的回歸管理功能,Verisium Manager 允許跨多個(gè)站點(diǎn)的覆蓋收斂,為不同規(guī)模的企業(yè)提供全面、可靠、有效且高效的解決方案。其強(qiáng)大的 API 集、企業(yè)級的可擴(kuò)展性和性能,使其能夠無縫連接驗(yàn)證流程中的所有引擎,包括模擬、形式化、仿真和原型平臺,為您提供全面的驗(yàn)證解決方案,并可以通過定制和優(yōu)化實(shí)現(xiàn)最大的驗(yàn)證吞吐量。

但真正使 Verisium Manager 如此與眾不同的原因在于它能夠應(yīng)用 AI 和機(jī)器學(xué)習(xí)顯著提高調(diào)試和回歸吞吐量的生產(chǎn)力。通過直接與智能 Verisium Apps 集成,該工具可以幫助您在驗(yàn)證過程中取得突破性成果,讓您在競爭中保持領(lǐng)先地位并實(shí)現(xiàn)業(yè)務(wù)目標(biāo)。簡而言之,如果您希望驗(yàn)證流程提升到一個(gè)新的水平,那么 Verisium Manager 就是您需要的終極驗(yàn)證管理工具。

Verisium 應(yīng)用

Verisium Platform 和相關(guān)應(yīng)用程序在提高調(diào)試效率和提高驗(yàn)證周期上發(fā)揮核心作用。這些應(yīng)用包括:

VerisiumAutoTriage

對存在相同錯(cuò)誤而導(dǎo)致失敗的測試進(jìn)行自動(dòng)分組。

Verisium SemanticDiff

通過識別故障原因來減少調(diào)試時(shí)間,并實(shí)現(xiàn)效率的顯著提高。

Verisium WaveMiner

幫助驗(yàn)證工程師在正確與錯(cuò)誤測試中更方便地比較并找到錯(cuò)誤點(diǎn)。波形格式完美適合現(xiàn)代驗(yàn)證需求,并將仿真波形生成速度提高了 2 倍。

Verisum PinDown

在編輯工具上固定某個(gè)標(biāo)簽,并分析仿真日志和代碼簽入之間的關(guān)系。

審核編輯:劉清

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27063瀏覽量

216488 -

EDA工具

+關(guān)注

關(guān)注

4文章

265瀏覽量

31718 -

soc

+關(guān)注

關(guān)注

38文章

4124瀏覽量

217964 -

人工智能

+關(guān)注

關(guān)注

1791文章

46896瀏覽量

237666 -

UPF

+關(guān)注

關(guān)注

0文章

49瀏覽量

13493

原文標(biāo)題:利用人工智能優(yōu)化調(diào)試效率和驗(yàn)證吞吐量

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何提高CYBT-243053-02吞吐量?

網(wǎng)卡吞吐量測試解決方案

如何利用NI LabVIEW技術(shù)提高測試系統(tǒng)的吞吐量?

如何提高VLD的吞吐量和執(zhí)行效率?

防火墻術(shù)語-吞吐量

如何提高無線傳感器網(wǎng)絡(luò)的吞吐量

如何提高系統(tǒng)設(shè)計(jì)容量和吞吐量

debug 吞吐量的辦法

debug 吞吐量的辦法

Cadence Verisium驗(yàn)證平臺以AI助力瑞薩電子提高糾錯(cuò)效率

如何顯著提高ATE電源吞吐量?

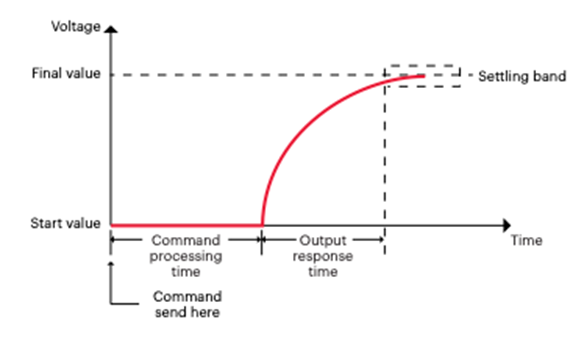

影響ATE電源系統(tǒng)吞吐量的關(guān)鍵因素

Verisium如何提高調(diào)試效率和驗(yàn)證吞吐量呢?

Verisium如何提高調(diào)試效率和驗(yàn)證吞吐量呢?

評論