什么是Chiplet技術(shù)

Chiplet技術(shù)是一種將集成電路設(shè)計(jì)和制造的方法,其中一個(gè)芯片被分割成多個(gè)較小的獨(dú)立單元,這些單元通常被稱(chēng)為“chiplets”。每個(gè)chiplet可以包含特定的功能塊、處理器核心、內(nèi)存單元或其他組件。這種技術(shù)的核心思想是將大型集成電路拆分成更小、更模塊化的部分,以便更靈活地設(shè)計(jì)、制造和組裝芯片。Chiplet技術(shù)可以突破單芯片光刻面積的瓶頸,減少對(duì)先進(jìn)工藝制程的依賴(lài),提高芯片的性能并降低制造成本。

通過(guò)將多個(gè)小芯片集成在一個(gè)封裝內(nèi),Chiplet技術(shù)可以實(shí)現(xiàn)更高的性能和更低的成本。每個(gè)小芯片可以單獨(dú)設(shè)計(jì)和制造,然后通過(guò)先進(jìn)的封裝技術(shù)將它們集成在一起。這種設(shè)計(jì)方法可以使芯片更加靈活,更容易適應(yīng)不同的應(yīng)用需求,同時(shí)也可以提高良率和降低制造成本。

Chiplet技術(shù)已經(jīng)成為當(dāng)前集成電路設(shè)計(jì)和制造領(lǐng)域的研究熱點(diǎn)之一,被廣泛應(yīng)用于各種不同類(lèi)型的芯片設(shè)計(jì)中,包括處理器、存儲(chǔ)器、傳感器等。隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷增長(zhǎng),相信Chiplet技術(shù)將繼續(xù)發(fā)展并發(fā)揮越來(lái)越重要的作用。

Chiplet技術(shù)有哪些優(yōu)點(diǎn)

Chiplet技術(shù)具有以下優(yōu)點(diǎn):

降低設(shè)計(jì)復(fù)雜性和成本:通過(guò)將芯片拆分成多個(gè)小芯片,可以降低設(shè)計(jì)的復(fù)雜性和成本。每個(gè)小芯片可以獨(dú)立設(shè)計(jì)、制造和測(cè)試,簡(jiǎn)化了設(shè)計(jì)流程,降低了設(shè)計(jì)和制造成本。

提高生產(chǎn)效率:每個(gè)小芯片可以獨(dú)立制造,并可以在不同的工藝節(jié)點(diǎn)上使用不同的制造技術(shù),提高了生產(chǎn)效率。

降低芯片功耗:通過(guò)將芯片拆分成多個(gè)小芯片,可以更好地管理功耗,使得整個(gè)系統(tǒng)的功耗降低。

提高芯片可靠性:由于每個(gè)小芯片都是獨(dú)立的,因此某個(gè)小芯片的故障不會(huì)導(dǎo)致整個(gè)系統(tǒng)的故障,提高了芯片的可靠性。

易于升級(jí)和維護(hù):某個(gè)小芯片需要升級(jí)或替換時(shí),只需要對(duì)該小芯片進(jìn)行升級(jí)或替換,而不是整個(gè)芯片,簡(jiǎn)化了升級(jí)和維護(hù)的流程。

促進(jìn)開(kāi)放創(chuàng)新:由于每個(gè)小芯片都是獨(dú)立的,因此可以獨(dú)立地進(jìn)行創(chuàng)新和優(yōu)化,促進(jìn)了開(kāi)放創(chuàng)新。

支持多種不同的半導(dǎo)體工藝技術(shù):Chiplet技術(shù)可以將各種不同的半導(dǎo)體工藝技術(shù)集成在一起,從而使得整個(gè)系統(tǒng)具有更好的性能和更低的成本。

因此,Chiplet技術(shù)在許多領(lǐng)域都有廣泛的應(yīng)用前景,包括通信、醫(yī)療、汽車(chē)電子等。隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷增長(zhǎng),相信Chiplet技術(shù)將繼續(xù)發(fā)展并發(fā)揮越來(lái)越重要的作用。

Chiplet技術(shù)有什么缺點(diǎn)

雖然Chiplet技術(shù)具有許多優(yōu)點(diǎn),但也有一些潛在的缺點(diǎn)和挑戰(zhàn)需要考慮:

接口問(wèn)題:由于Chiplet是獨(dú)立的小芯片,因此需要確保它們之間的通信和接口是高效、可靠和穩(wěn)定的。這涉及到如何選擇和設(shè)計(jì)適當(dāng)?shù)?a target="_blank">連接器和接口協(xié)議,以便在高速、低功耗和低延遲方面達(dá)到性能要求。

管理復(fù)雜度:在設(shè)計(jì)和制造過(guò)程中,管理多個(gè)Chiplet的復(fù)雜性可能會(huì)增加。需要開(kāi)發(fā)新的工具和流程來(lái)確保所有Chiplet都能協(xié)同工作,并滿(mǎn)足性能、可靠性和安全性的要求。

封裝挑戰(zhàn):將多個(gè)Chiplet集成到一個(gè)封裝中需要先進(jìn)的封裝技術(shù),包括先進(jìn)的基板、布線(xiàn)、互連和測(cè)試技術(shù)。這些技術(shù)可能會(huì)帶來(lái)成本、可靠性和性能方面的挑戰(zhàn)。

設(shè)計(jì)工具的不足:雖然有許多用于傳統(tǒng)單芯片設(shè)計(jì)的EDA工具可用,但適用于Chiplet設(shè)計(jì)的工具可能還不成熟或缺乏標(biāo)準(zhǔn)化。這可能導(dǎo)致設(shè)計(jì)復(fù)雜度和成本的增加。

驗(yàn)證和測(cè)試的挑戰(zhàn):驗(yàn)證和測(cè)試多Chiplet設(shè)計(jì)的完整性和可靠性可能會(huì)更加困難和復(fù)雜,需要采用新的驗(yàn)證和測(cè)試方法和技術(shù)。

依賴(lài)先進(jìn)的制程技術(shù):雖然Chiplet技術(shù)可以降低對(duì)先進(jìn)制程技術(shù)的依賴(lài),但在某些情況下,仍然需要依賴(lài)先進(jìn)的制程技術(shù)來(lái)制造某些Chiplet,這可能增加了成本和技術(shù)挑戰(zhàn)。

生態(tài)系統(tǒng)建設(shè):要使Chiplet技術(shù)被廣泛接受并應(yīng)用,需要建立一個(gè)包括芯片供應(yīng)商、封裝合作伙伴和系統(tǒng)集成商在內(nèi)的生態(tài)系統(tǒng)。這可能需要時(shí)間和資源來(lái)建立和維護(hù)。

盡管存在這些潛在的缺點(diǎn)和挑戰(zhàn),但隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷增長(zhǎng),相信這些問(wèn)題將得到解決,使Chiplet技術(shù)成為一種更加成熟和可靠的解決方案。

Chiplet技術(shù)的發(fā)展前景如何

當(dāng)前,Chiplet技術(shù)已經(jīng)成為集成電路設(shè)計(jì)和制造領(lǐng)域的研究熱點(diǎn)之一,并取得了一些重要的進(jìn)展。以下是一些關(guān)于Chiplet技術(shù)的發(fā)展現(xiàn)狀:

標(biāo)準(zhǔn)制定和生態(tài)系統(tǒng)建設(shè):為了加速Chiplet技術(shù)的普及和應(yīng)用,一些組織已經(jīng)開(kāi)始制定標(biāo)準(zhǔn)并建立生態(tài)系統(tǒng)。例如,Intel、AMD、臺(tái)積電、ARM等公司聯(lián)合成立了Chiplet標(biāo)準(zhǔn)聯(lián)盟,并推出了UCIe(Universal Chiplet Interconnect Express)標(biāo)準(zhǔn)。此外,還有一些組織推出了基于Chiplet技術(shù)的開(kāi)放生態(tài)系統(tǒng),例如OpenHPC和ChipletHub等。

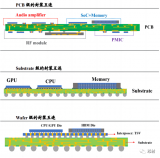

先進(jìn)的封裝技術(shù):隨著封裝技術(shù)的不斷進(jìn)步,Chiplet的集成和互連已經(jīng)取得了一些重要的進(jìn)展。例如,臺(tái)積電已經(jīng)開(kāi)發(fā)出了基于CoWoS(Chip on Wafer on Substrate)技術(shù)的先進(jìn)封裝技術(shù),可以將多個(gè)小芯片集成在一起,并實(shí)現(xiàn)高帶寬、低延遲的互連。此外,還有一些公司推出了基于2.5D和3D集成技術(shù)的封裝解決方案,例如AMD的Infinity Fabric和臺(tái)積電的SoIC技術(shù)。

跨工藝節(jié)點(diǎn)和跨材料體系的應(yīng)用:隨著半導(dǎo)體制造技術(shù)的不斷進(jìn)步,Chiplet技術(shù)已經(jīng)可以靈活地集成不同工藝節(jié)點(diǎn)和不同材料體系的芯片。例如,Intel已經(jīng)將自家的14nm和7nm工藝技術(shù)應(yīng)用于其芯片設(shè)計(jì)中,而AMD則采用了臺(tái)積電的7nm和5nm工藝技術(shù)。此外,還有一些公司正在探索將硅和化合物半導(dǎo)體集成在一起,以實(shí)現(xiàn)更高效和更高性能的芯片。

智能和可重構(gòu)的Chiplet:隨著人工智能和可重構(gòu)計(jì)算技術(shù)的發(fā)展,智能和可重構(gòu)的Chiplet已經(jīng)成為一個(gè)新的發(fā)展方向。例如,AMD在其Ryzen處理器中集成了基于AI的芯片,用于實(shí)現(xiàn)智能電源管理和性能優(yōu)化。此外,還有一些公司正在開(kāi)發(fā)基于可重構(gòu)計(jì)算技術(shù)的芯片,以實(shí)現(xiàn)更高的性能和能效。

大規(guī)模集成和高密度集成:隨著半導(dǎo)體制造技術(shù)的不斷進(jìn)步,大規(guī)模集成和高密度集成已經(jīng)成為可能。例如,AMD在其Ryzen處理器中集成了超過(guò)100個(gè)小芯片,實(shí)現(xiàn)了高性能和高能效。此外,還有一些公司正在探索將多個(gè)芯片集成在一起,以實(shí)現(xiàn)更小、更高效的系統(tǒng)。

總之,隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷增長(zhǎng),Chiplet技術(shù)已經(jīng)成為集成電路設(shè)計(jì)和制造領(lǐng)域的重要發(fā)展方向之一。雖然目前還存在一些挑戰(zhàn)和問(wèn)題需要解決,但隨著研究和發(fā)展的不斷深入,相信這些問(wèn)題將得到解決,并推動(dòng)Chiplet技術(shù)的發(fā)展和應(yīng)用。

還有什么其他技術(shù)正在研究中嗎

除了Chiplet技術(shù),目前正在研究的還有先進(jìn)封裝技術(shù)、異構(gòu)集成技術(shù)、晶圓級(jí)封裝技術(shù)等。這些技術(shù)可以與Chiplet技術(shù)結(jié)合使用,以實(shí)現(xiàn)更高效、更靈活和更低成本的集成電路設(shè)計(jì)和制造。例如,異構(gòu)集成技術(shù)可以將不同材料、不同工藝和不同尺寸的芯片集成在一起,實(shí)現(xiàn)高性能和高能效的系統(tǒng)。晶圓級(jí)封裝技術(shù)可以將多個(gè)芯片在晶圓級(jí)別上進(jìn)行封裝,實(shí)現(xiàn)大規(guī)模集成和高密度集成。總之,隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的不斷增長(zhǎng),這些技術(shù)有望在未來(lái)得到更廣泛的應(yīng)用。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421782 -

集成電路

+關(guān)注

關(guān)注

5381文章

11381瀏覽量

360850 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

545瀏覽量

67961 -

chiplet

+關(guān)注

關(guān)注

6文章

416瀏覽量

12558

原文標(biāo)題:Chiplet技術(shù)講解

文章出處:【微信號(hào):TenOne_TSMC,微信公眾號(hào):芯片半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

紅外與藍(lán)牙技術(shù)有什么不同?有什么優(yōu)缺點(diǎn)?

北極雄芯開(kāi)發(fā)的首款基于Chiplet異構(gòu)集成的智能處理芯片“啟明930”

chiplet是什么意思?chiplet和SoC區(qū)別在哪里?一文讀懂chiplet

芯動(dòng)兼容UCIe標(biāo)準(zhǔn)的最新Chiplet技術(shù)解析

Chiplet技術(shù)給EDA帶來(lái)了哪些挑戰(zhàn)?

先進(jìn)封裝Chiplet的優(yōu)缺點(diǎn)與應(yīng)用場(chǎng)景

半導(dǎo)體Chiplet技術(shù)及與SOC技術(shù)的區(qū)別

半導(dǎo)體Chiplet技術(shù)的優(yōu)點(diǎn)和缺點(diǎn)

Chiplet關(guān)鍵技術(shù)與挑戰(zhàn)

Chiplet究竟是什么?中國(guó)如何利用Chiplet技術(shù)實(shí)現(xiàn)突圍

chiplet和cpo有什么區(qū)別?

chiplet和cowos的關(guān)系

Chiplet主流封裝技術(shù)都有哪些?

Chiplet技術(shù)對(duì)英特爾和臺(tái)積電有哪些影響呢?

什么是Chiplet技術(shù)?

什么是Chiplet技術(shù)?Chiplet技術(shù)有哪些優(yōu)缺點(diǎn)?

什么是Chiplet技術(shù)?Chiplet技術(shù)有哪些優(yōu)缺點(diǎn)?

評(píng)論