標題為“電源門控”的文章演示了電源門控單元的實現以及它如何幫助最大限度地減少 SoC 的泄漏功耗。其基本原理是切斷從電池(VDD)到接地(GND)的直接路徑。雖然有效地節省泄漏功率,實施討論遭受一個主要的缺點!它不挽留的狀態!這意味著,一旦SoC的功率恢復,功率門控單元的輸出將變為“X”。你不能確定它是邏輯1還是邏輯0。在乎嗎是的!因為如果這個X傳播到設計中,整個設備就可能進入亞穩態!為了防止這種災難性的情況:系統軟件可以簡單地重置SoC。這將從頭啟動,并確保所有設備都已初始化。

這意味著,每次我決定給我的SoC的一部分供電時,一旦恢復電源,我就必須重新設置那個電源門控部分。這對上一篇文章中討論的電源門的應用施加了嚴重的限制。設計一個保持狀態的電源門怎么樣?但要說服自己,為了做到這一點,你需要花費,雖然很小,一些泄漏功率。我們把這個結構稱為:狀態保持偽功率門。術語“偽”意味著它將消耗一點泄漏功率,而不是先前的結構。但與此同時,您不再需要重置SoC的電源門控部分,因為標準單元保留了它們以前的數據!!不說了!下面我們來討論一下實現。

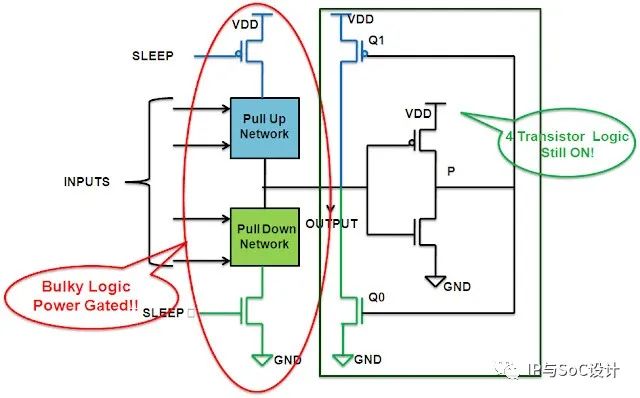

以上電路有兩部分。

·紅色橢圓形內部的結構與普通的功率門控結構相同。

·綠框內的一個(右邊)是使該設備保持其狀態所需的附加電路。

操作:在進入睡眠模式之前,設備的輸出為邏輯1。進入睡眠模式(關閉電源)后,睡眠晶體管開始工作,并切斷設備的電源和接地軌,從而節省泄漏功率。但是右邊的邏輯(在綠色矩形中)仍然是ON!反相器的輸出現在將變成OUTPUT’,即邏輯0。這將反過來使PMOS晶體管Q1和輸出將恢復到邏輯1。

當輸出在電源門控之前為邏輯0時,情況也是如此。在這種情況下,NMOS晶體管Q0將起作用,以幫助輸出節點保留其數據。

請注意:在此期間,當設備處于睡眠模式時,輸出節點將繼續泄漏。通過添加額外的電路,如圖所示,我們基本上是試圖創建一個反饋回路,這再次有助于保持狀態。命中,當然是4個晶體管的泄漏功率。然而,標準單元邏輯(紅色橢圓形)通常是笨重的。即使是一個簡單的雙輸入"與非"門本身也有4個晶體管。而更高階的輸入會有更多!同樣的技術可以應用于任何順序的設備,如觸發器,鎖存器,甚至時鐘門控集成單元。

審核編輯:湯梓紅

-

電源

+關注

關注

184文章

17585瀏覽量

249488 -

soc

+關注

關注

38文章

4122瀏覽量

217935 -

晶體管

+關注

關注

77文章

9634瀏覽量

137848 -

觸發器

+關注

關注

14文章

1996瀏覽量

61051

原文標題:博文速遞:State Retention Power Gating

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電動后尾門控制單元主要功能

電動后尾門控制單元主要功能

如何去實現一種電源門控的設計呢

電源門控概述

什么是時鐘門控?如何去實線時鐘門控的設計呢

基于門控時鐘的低功耗電路設計方案

模塊化氣動閥門控制單元的原理及設計

一種門控循環單元興趣點推薦算法

通常有兩種不同的時鐘門控實現技術

LPMM閱讀筆記——第五章 電源門控設計part1

電源門控單元的實現原理

電源門控單元的實現原理

評論