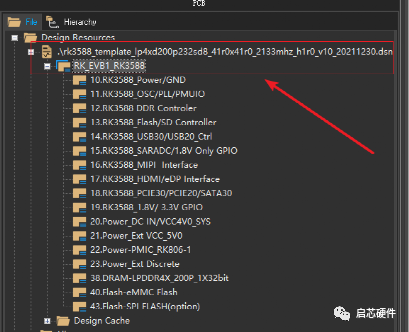

電路工作到了后期需要匯報或者寫文章需要設計原圖 ,這里整理一下Cadence設計原理圖常用導出方案。

前期工具用的好,后期處理沒煩惱,Cadence自帶工具其實很強大,只是你沒嘗試用。

仿真環境:虛擬機Linux下Cadence617 原理圖繪制工具:virtuoso

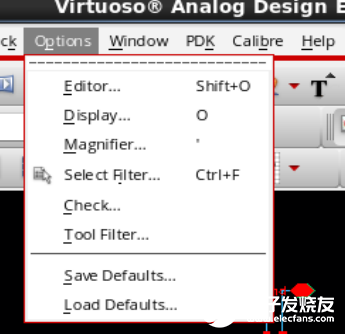

1. 去除原理圖背景的網格:

OPtions → Display //快捷鍵O

(早期版本在菜單View → Grid )

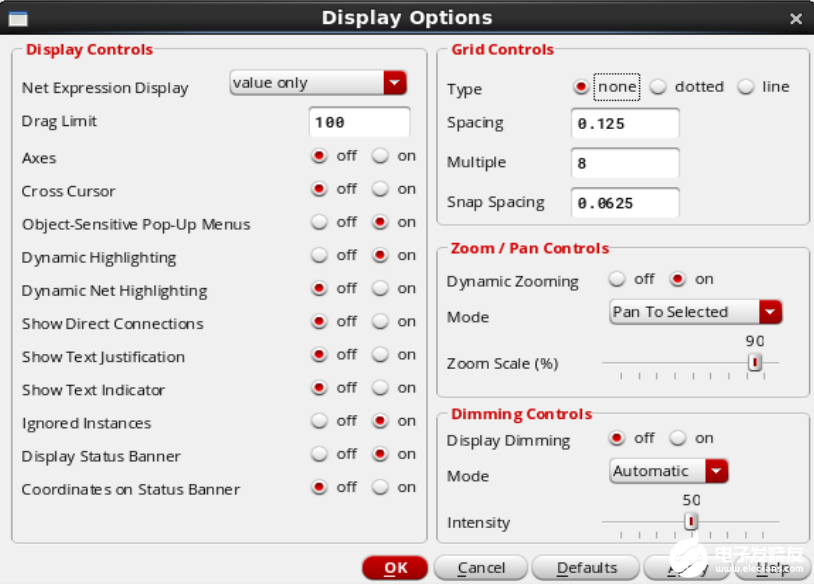

選擇 Grid Controls框中的Type并設置為none,即不設置網格風格

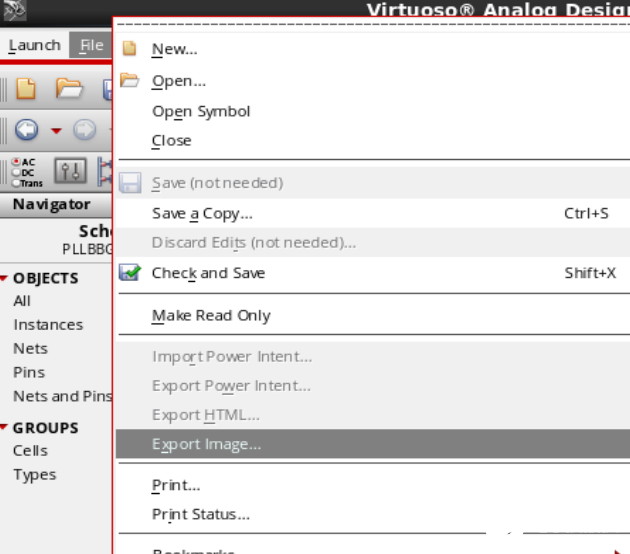

2. 將原理圖導出圖片:

File → Export Image

(這里不選擇Print,打印功能需要安裝Linux環境的PDF虛擬打印機,愛折騰同學的可試試)

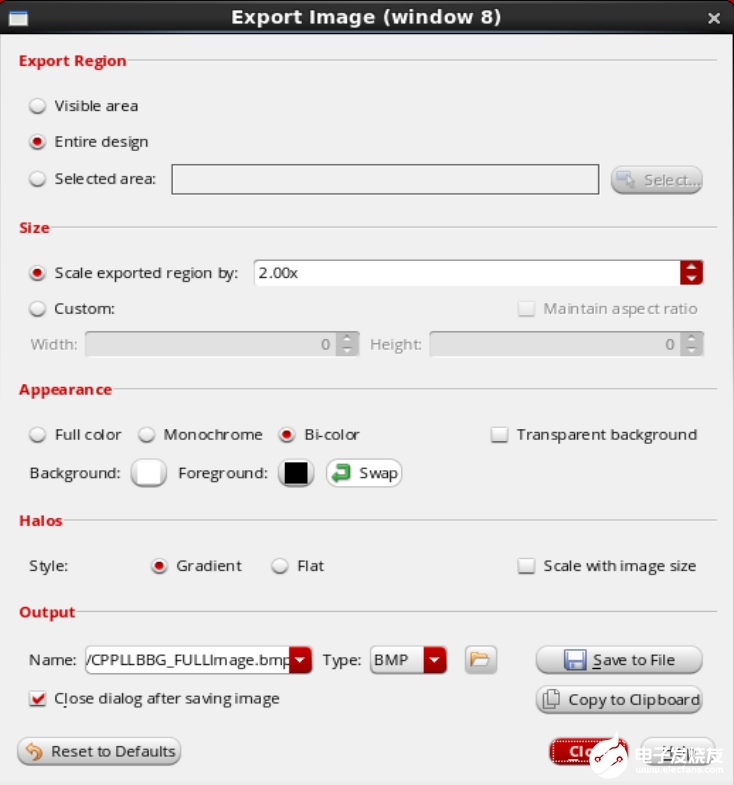

a)Export Region選擇 “設計全景”Entire design

b)Size選擇Scale exported region by:缺省值為1.00x

此數值越大 = 輸出圖像文件越大 = 越清楚

頂層框圖建議2.00x

字模塊圖管子較多建議6.00x(輸出BMP格式文件大約50M)

c)論文用圖:Appearance選擇 “黑白雙色”Bi-color

Background:白色

Foreground:黑色

d)Output中Type選擇 BMP圖片格式(原圖信息保留最好)

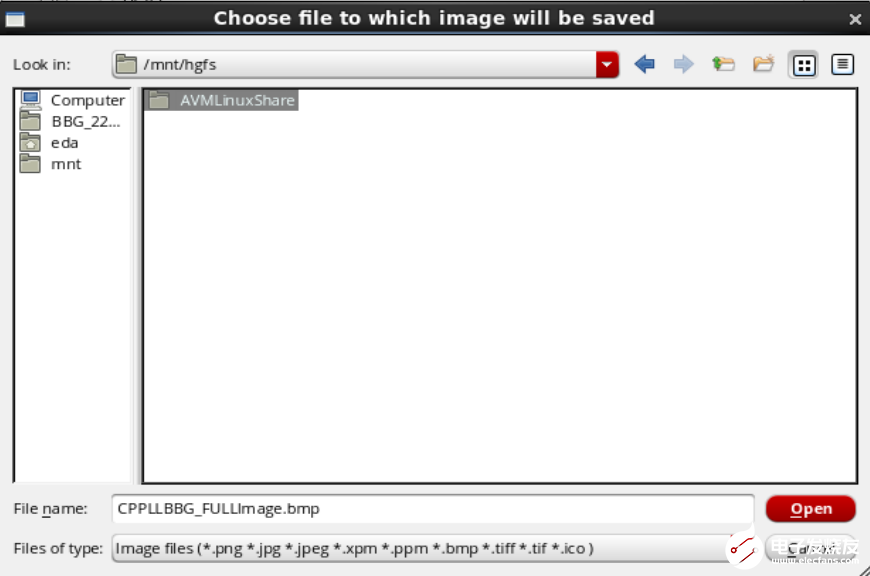

e)文件保存路徑設置在虛擬級的共享文件夾(方便Win查看使用)

路徑一般為:/mnt/hgfs/自定義文件夾

f)Save to File保存完成窗口會自動關閉

審核編輯:黃飛

-

原理圖

+關注

關注

1284文章

6198瀏覽量

230155 -

Linux

+關注

關注

87文章

11090瀏覽量

207611 -

Cadence

+關注

關注

63文章

897瀏覽量

141288 -

虛擬機

+關注

關注

1文章

880瀏覽量

27725

發布評論請先 登錄

相關推薦

cadence原理圖手冊-原理圖分冊

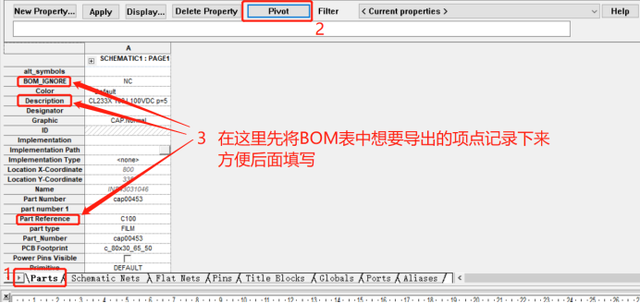

Cadence從原理圖中導出元件庫,發生器件信息丟失問題

cadence原理圖無法打開

cadence 原理圖檢查工具

Cadence設計原理圖常用導出方案分享

Cadence PCB導出stp用SolidWorks打開異常

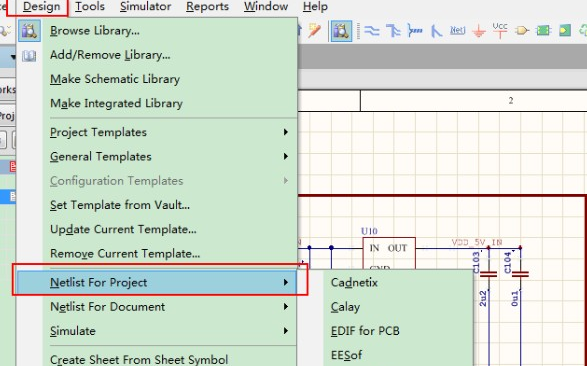

Altium Designer導出Cadence網表的步驟

Altium Designer原理圖PCB轉換到cadence的方法(一)

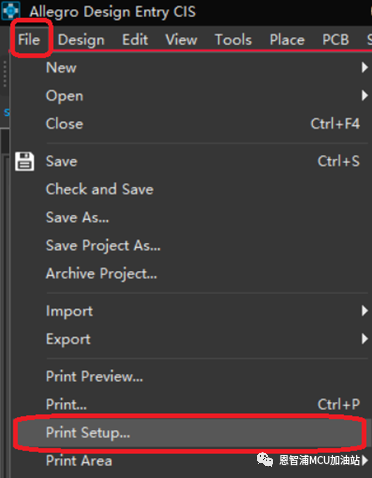

Cadence生成PDF原理圖,這一篇就足夠!

Cadence設計原理圖常用導出方案

Cadence設計原理圖常用導出方案

評論