JK觸發器可以根據觸發方式分為兩種類型:上升沿觸發和下降沿觸發。這兩種觸發方式在數字電路設計中常常被使用,具有重要的作用。下面將詳細介紹JK觸發器的工作原理、上升沿觸發和下降沿觸發的區別以及它們在實際應用中的一些案例。

JK觸發器是最常用的觸發器類型之一。它由兩個互補的輸入引腳J(Set)和K(Reset)以及兩個輸出引腳Q和~Q(Q的反相輸出)組成。JK觸發器的內部構造是由兩個交叉耦合的SR觸發器組成的。J和K的值決定了JK觸發器的輸出狀態。

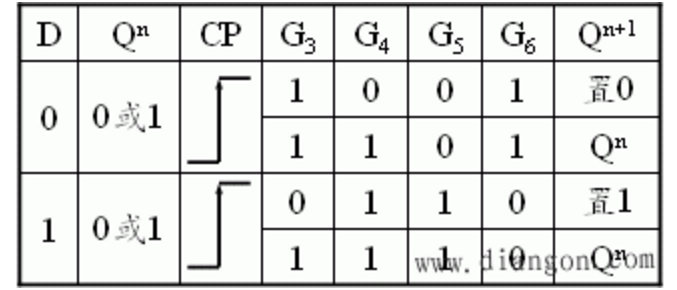

JK觸發器的工作原理是,在觸發器的上一狀態下,如果J和K均為0,則輸出保持不變;如果J和K均為1,則輸出取反,即Q= ~Q;如果J=1且K=0,則輸出為1;如果J=0且K=1,則輸出為0。JK觸發器在給定時鐘脈沖的上升沿或下降沿時,根據輸入信號的不同,可以實現不同的功能,這就是上升沿觸發和下降沿觸發的機制。

在上升沿觸發方式下,觸發器的輸出在給定時鐘信號的上升沿發生變化。即當時鐘信號沿著從低電平到高電平的轉變時,JK觸發器根據當前的輸入狀態來決定輸出的變化。如果J和K均為0,則輸出保持不變;如果J和K均為1,則輸出取反,即Q= ~Q;如果J=1且K=0,則輸出為1;如果J=0且K=1,則輸出為0。上升沿觸發的特點是在時鐘信號上升沿到來時才讀取輸入,因此輸入只有在時鐘信號上升沿時才會對輸出產生影響。

在下降沿觸發方式下,觸發器的輸出在給定時鐘信號的下降沿發生變化。即當時鐘信號沿著從高電平到低電平的轉變時,JK觸發器根據當前的輸入狀態來決定輸出的變化。與上升沿觸發方式相比,下降沿觸發延遲了輸入對輸出的影響,因為在下降沿到來之前,輸入信號已經穩定了一段時間。因此,在下降沿觸發方式下,J和K的輸入是在時鐘信號下降沿到來之前被讀取的。

上升沿觸發和下降沿觸發在實際應用中有各自的優勢和適用場景。上升沿觸發適用于需要在時鐘信號上升沿到來時立即響應輸入變化的場合。這種觸發方式可以提供更高的實時性和響應速度。下降沿觸發則適用于需要在時鐘信號周期的最后一刻才讀取輸入的情況。這種觸發方式可以減少由于輸入變化引起的不穩定性,提高電路的穩定性和可靠性。

在數字電路設計中,JK觸發器的上升沿觸發和下降沿觸發廣泛應用于各種時鐘同步電路中。時鐘同步電路是處理時序問題的重要電路,在數字電路設計中起到了至關重要的作用。例如,在存儲器中,使用JK觸發器可以實現時鐘同步讀取和寫入操作,保證數據的穩定性和正確性。另外,在計數器和定時器等電路中,選擇合適的觸發方式可以簡化電路結構,提高性能和效率。

總結來說,JK觸發器可以根據觸發方式分為上升沿觸發和下降沿觸發。上升沿觸發根據當前輸入在時鐘信號的上升沿到來時更新輸出;下降沿觸發在時鐘信號的下降沿到來時更新輸出。它們在實際應用中具有不同的優勢和適用場景,可以根據具體需求選擇合適的觸發方式。通過合理使用JK觸發器的觸發方式,可以實現各種復雜的數字電路設計,提高電路的性能和穩定性。

-

JK觸發器

+關注

關注

1文章

43瀏覽量

15878 -

引腳

+關注

關注

16文章

1184瀏覽量

50293 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28512 -

數字電路設計

+關注

關注

0文章

20瀏覽量

12658

發布評論請先 登錄

相關推薦

具有置位和復位功能的雙 JK 觸發器;上升沿觸發-74HC_HCT109_Q100

jk觸發器是上升沿還是下降沿觸發

jk觸發器是上升沿還是下降沿觸發

評論