摘 要

半導體元件制造涉及到一系列復雜的制作過程,將原材料轉化為成品元件,以應用于提供各種關鍵控制和傳感功能應用的需求。

Andreas Bier

Sr Principal Product Marketing Specialist

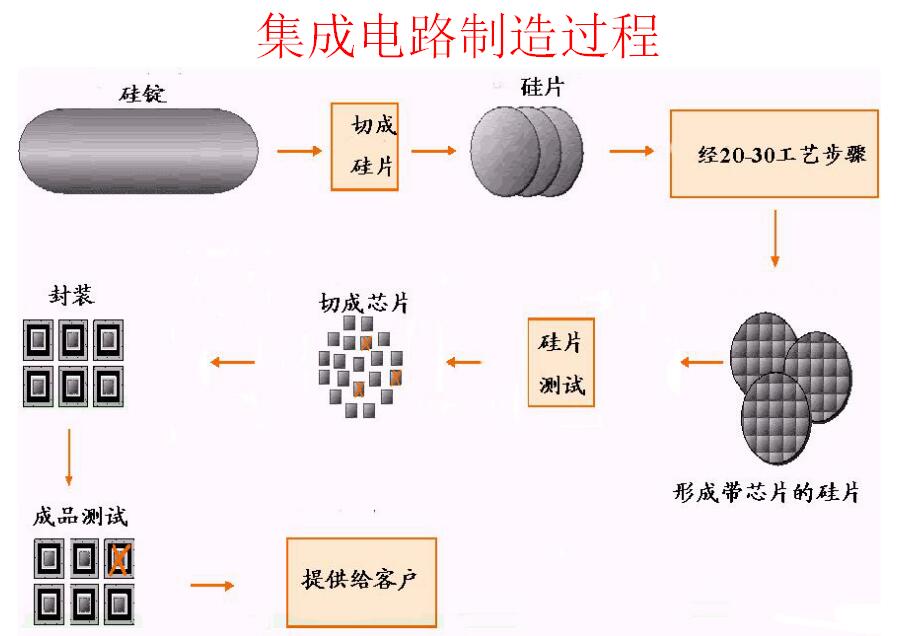

半導體制造涉及一系列復雜的工藝過程,從而將原材料轉化為最終的成品元件。該工藝通常包括四個主要階段:晶片制造、晶片測試組裝或封裝以及最終測試。每個階段都有其獨特的攻堅點和機遇。而其制造工藝也面臨著包括成本、復雜多樣性和產量在內的諸多挑戰,但也為創新和發展帶來了巨大的機遇。通過應對其中的困難并抓住機遇,推進研發新技術來改變我們的生活和工作方式,同時促使行業可以持續發展和壯大。

半導體制造工藝概述

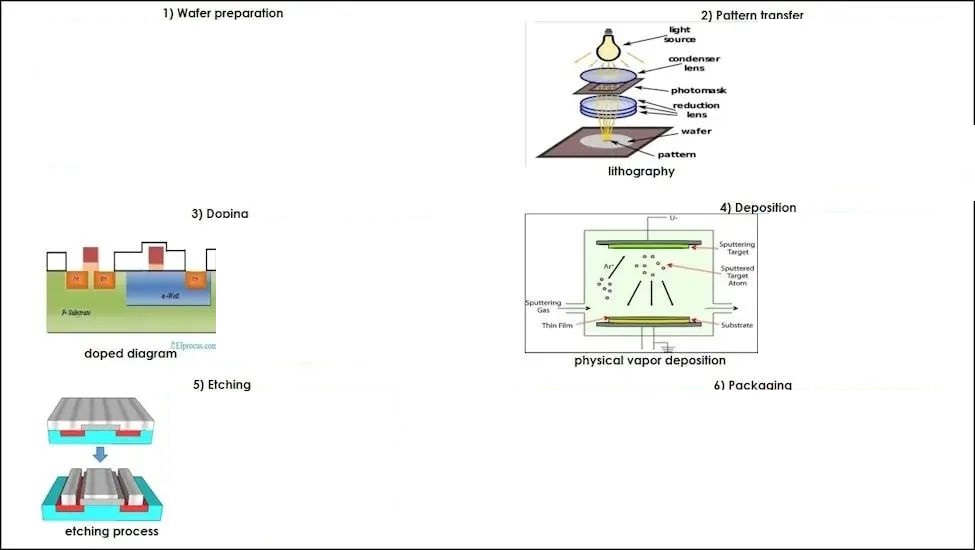

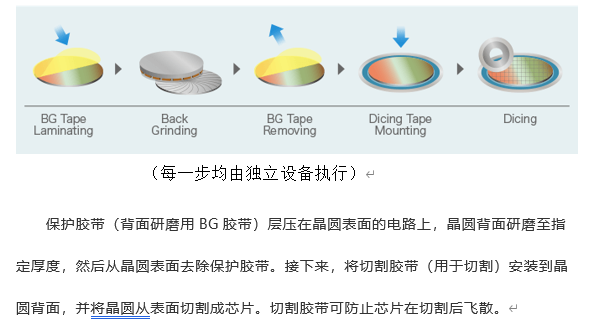

▲ 半導體晶圓制造的主要過程: 1)晶圓制備 2)圖案轉移 3)材質摻雜 4)沉積 5)蝕刻 6)封裝

制造半導體的過程可以分為以下幾個關鍵步驟。

第一步:晶圓制備

選擇硅晶片作為半導體工藝的起始材料。清洗、拋光晶圓,并準備用作制造電子元件的襯底。

第二步:圖案化

在這一過程中,使用稱為光刻的工藝在硅晶片上創建圖案。將一層抗腐蝕的光刻膠施加到晶片表面,然后將掩模放置在晶片頂部。掩模上具有對應的相關預制造的電子元件的圖案。然后使用紫外光將圖案從掩模轉移到光刻膠層上。曝光的光刻膠區域隨后被去除,最終在晶片上留下圖案化的表面。

第三步:材質摻雜

在這個步驟中,材質被添加到硅晶片中以改變其電特性。最常用的材質是硼或磷,少量加入可以分別產生p型或n型的半導體。這些材質是通過一種稱為離子注入的工藝,利用離子加速,將被加速的離子注入到晶片的表面。

第四步:晶片沉積處理

在這個制作過程中,薄膜材料被沉積在晶片上以生成電子元件。這可以通過多種技術來實現,包括化學氣相沉積(CVD)、物理氣相沉積(PVD)和原子層沉積(ALD)。這些工藝可用于沉積金屬、氧化物和氮化物等材料。

第五步:蝕刻

從晶片表面去除部分材質,以產生電子元件所需的形狀和結構。可以使用多種技術來進行蝕刻,包括濕式蝕刻、干式蝕刻和等離子蝕刻。這些工藝使用化學物質或等離子體從晶片上選擇性地去除特定的材質。

最后一步:封裝

電子元件被封裝成可用于電子設備的最終產品。這包括將元件連接到諸如印刷電路板的基板上,然后使用導線或其他方式將它們連接到其他元件上。半導體工藝非常復雜,涉及各種專用設備和材料。這些工藝對于現代電子設備的制造是必不可少的,并且隨著新技術的迭代而不斷發展。

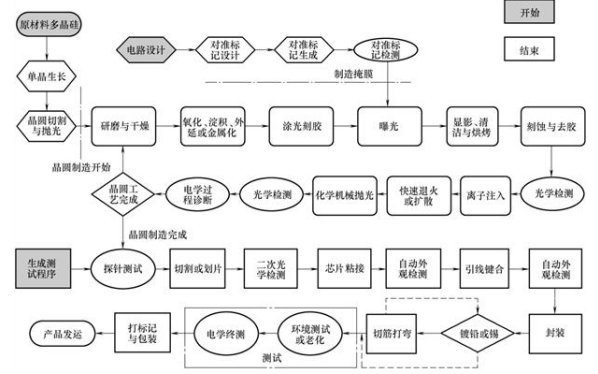

通常,生產半導體芯片的過程需要幾周到幾個月的時間。從第一階段開始,需要制造一個硅片,作為芯片的襯底。此工藝通常包括如下過程,清洗、沉積、光刻、蝕刻和摻質。晶片可能需要經受數百個不同的工藝加工,所以,整個晶片制造過程可能要花費長達16~18周的時間。

當在晶圓上制造出獨立的單一芯片,就需要將它們分離并封裝成獨立的單元。同時包括測試每個芯片以確保其符合規格要求,然后將其從晶圓上分離并安裝到封裝或基板上。芯片封裝后,會經過嚴格的測試過程,以確保它們符合質量標準并達到預期的功能。這包括運行電子測試、功能測試和其他類型的驗證測試,以識別任何缺陷或問題。這也取決于芯片的復雜程度和所需的測試要求,所以這一封裝和測試過程可能需要8-10周的時間。

總而言之,生產半導體芯片的整個過程可能需要幾周或幾個月的時間,其因是它取決于所使用的相關技術和芯片的設計復雜程度。

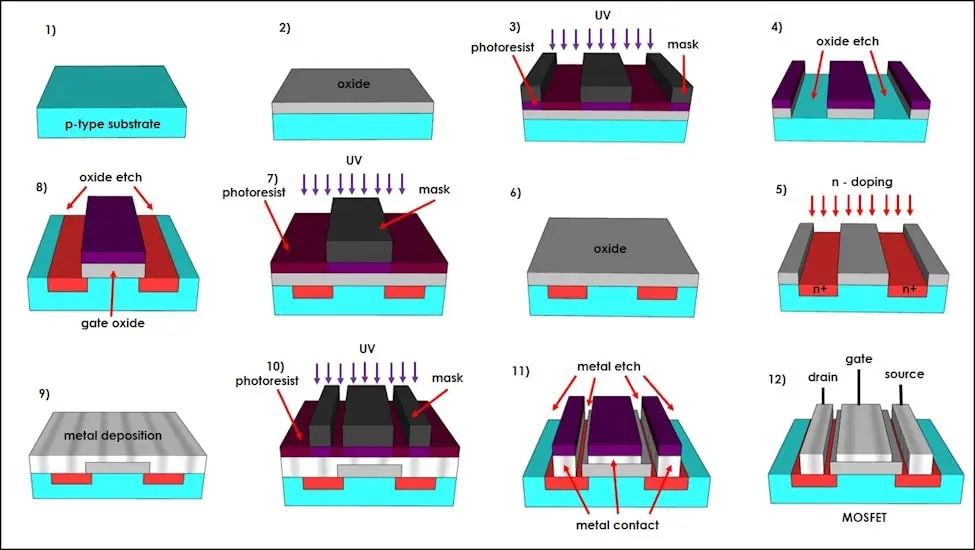

▲半導體器件制造中主要工藝的步驟及概要:1)p型襯底晶片 2)熱氧化 3)光刻 4)氧化物蝕刻 5)n+離子注入 6)熱氧化 7)柵極光刻 8)柵極氧化物蝕刻 9)金屬沉積 10)金屬接觸光刻 11)金屬蝕刻 12)定型元件

半導體制造趨勢和挑戰

圖案轉移

圖案轉移技術的進步已經成為半導體工業快速發展的關鍵驅動力,進而能夠制造更小和更復雜的電子元件。圖案轉移技術的一個主要進步是先進光刻技術的發展。光刻是使用光或其他輻射源將圖案轉移到媒質面上的過程。尤其近幾年開發的光刻技術,例如極紫外(EUV)光刻和多重圖案化技術,用以產生更小和更復雜的圖形。EUV平版印刷術使用極短波長的光束在硅晶片上制作極其精密的圖形。這種技術能夠創造微小到幾納米的尺寸,這對于制造微處理器等先進電子元件至關重要。多重圖案化是另一種光刻技術,它能夠制作更小的圖案。此技術包括將單個圖案分解成多個微量極的圖案,然后轉移到晶片表面。致使創建的圖案可以小于光刻技術中所使用的輻射波長。

摻質

摻質是向硅片中加入特定的介質以改變其電特性。摻質技術的進步一直是半導體行業快速發展的關鍵因素。這一技術的進步是得益于新的介質材料的出現。傳統上,硼和磷是最常用的摻質材料,因為它們可以分別產生p型和n型半導體。然而,近年來,鍺、砷和銻等新材料已被開發出來,可用于制造更復雜的電子元件。摻質技術的另一個進步是更精確的摻質工藝的進步。在過去,離子注入是用于摻質的主要技術,包括高速離子的運用,將介質注入晶片的表面。雖然離子注入仍然被普遍使用,但是諸如分子束外延(MBE)和化學氣相沉積(CVD)等新技術已經被開發出來,使摻質處理過程得到更精確的控制。

沉積

沉積是半導體制造中的又一關鍵工藝,包括將材料薄膜沉積到襯底上。這一過程可以通過各種技術實現,例如物理氣相沉積(PVD)、化學氣相沉積(CVD)、原子層沉積(ALD)等。同時新技術也在不斷的發展,包括金屬有機化學氣相沉積(MOCVD)、等離子體增強沉積、卷對卷沉積等。

蝕刻

蝕刻包括去除半導體材料的特定部分以產生圖案或結構。蝕刻技術的進步是半導體工業快速發展的主因,也是制造更小和更復雜的電子元件的關鍵技術。過去,濕法蝕刻是普遍應用的主要技術,包括將晶片浸入溶解材料的溶液中。然而,濕法蝕刻并不精確,會對相鄰結構造成損傷。而干法蝕刻技術的出現,實現了更精確和高可控的蝕刻制作,諸如反應離子蝕刻(RIE)和等離子體蝕刻。RIE是一種使用反應離子體從晶片上選擇性去除材料的技術,允許對蝕刻過程進行精確控制。而等離子體蝕刻是一種類似的技術,使用氣體等離子體來去除材料,但是它具有選擇性地去除特定材料的額外好處,例如金屬或硅。

封裝

半導體制造中的封裝工藝包括將集成電路封裝在保護外殼中,該保護外殼還提供與外界的電連接。封裝過程會影響最終產品的性能、可靠性和成本。3D封裝包括將多個芯片堆疊在一起,以創建高密度集成電路。這種技術可以減小器件的整體尺寸并提高其性能,同時還能降低功耗。扇出(fan-out)封裝是一種將集成電路嵌入環氧模塑料層的技術,使用從芯片扇出的銅柱進行電連接。這項技術能夠以更小的尺寸實現高密度封裝。系統級封裝(SiP)是另一種將多個芯片、傳感器和其他組件集成到一個封裝的技術。它可以做到減小器件的整體尺寸,同時還能提高其綜合性能。

瑞薩在支持半導體工藝方面的作用和進步

瑞薩電子是公認杰出的先進半導體解決方案供應商,為包括汽車、工業和物聯網在內的廣泛應用提供微控制器、模擬和功率部件以及片上系統(SoC)解決方案。我們致力于創新,并通過開發先進技術,在支持半導體工藝方面發揮了舉足輕重的作用。

瑞薩在先進計算產品的開發方面取得了重大突破,在數字和模擬領域都有極高的擴展和創新。我們的設備和元組件提供了從電源管理到電機控制等各種應用所需的關鍵控制和傳感能力。同時不斷地開發各個創新技術,如碳化硅(SiC)MOSFET,與傳統的硅基元件相比,其效率更高,損耗更低。公司還通過開發先進的制造技術,在半導體制作工藝的進步中發揮了主導作用。例如,瑞薩開發了一種稱為金屬-氧化物-氮化物-氧化物-硅(MONOS)的獨特工藝,能夠制造高密度、高速閃存設備。這種工藝已被用于開發高級內存解決方案,廣泛應用于汽車和工業等領域。

除了技術進步,瑞薩還致力于通過伙伴合作關系支持半導體行業,與其他公司或組織密切合作,共同開發行業標準和最佳應用實踐,以促進半導體行業的不斷創新和進步。更多內容,您可復制下方對應的鏈接或點擊文末閱讀原文訪問查看。

瑞薩電子(TSE: 6723)

科技讓生活更輕松,致力于打造更安全、更智能、可持續發展的未來。作為全球微控制器供應商,瑞薩電子融合了在嵌入式處理、模擬、電源及連接方面的專業知識,提供完整的半導體解決方案。成功產品組合加速汽車、工業、基礎設施及物聯網應用上市,賦能數十億聯網智能設備改善人們的工作和生活方式。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27003瀏覽量

216264 -

晶圓

+關注

關注

52文章

4838瀏覽量

127793 -

制造工藝

+關注

關注

2文章

175瀏覽量

19732

原文標題:半導體科普 | 半導體制造工藝——挑戰與機遇

文章出處:【微信號:瑞薩電子,微信公眾號:瑞薩電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體制程

半導體制造的難點匯總

半導體制造工藝教程的詳細資料免費下載

半導體制造教程之工藝晶體的生長資料概述

兩種標準的半導體制造工藝介紹

半導體制造工藝科普

半導體制造工藝科普

評論