文章來源:芯云知

原文作者:Crane

本文介紹了干法刻蝕用到的設備的原理及結構。

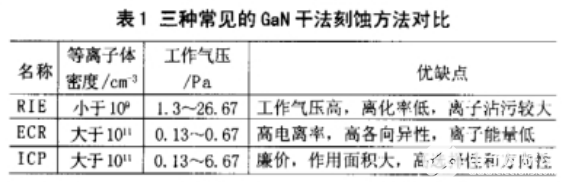

干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構。常見的干法刻蝕設備有反應離子刻蝕機(RIE)、電感耦合等離子體刻蝕機(ICP)、磁性中性線等離子體刻蝕機(NLD)、離子束刻蝕機(IBE),本文目的對各刻蝕設備的結構進行剖析,以及分析技術的優缺點。

RIE

RIE設備的結構通常比較簡單,一般由射頻電源、陽極、陰極、氣源和真空泵組成,其中,晶圓位于陰極上,射頻電源與陰極相連接,在刻蝕開始時,射頻電源施加電場到氣體上,氣體被電離為離子、電子、原子和分子,其中由于電子的運動速度遠大于其他離子,在刻蝕腔中會形成明顯的鞘區,在晶圓上方會形成自偏壓的電場,RIE利用該效應吸引并加速等離子體中的離子與被刻蝕材料產生物理化學作用,最終產生的副產物氣體揮發被排出。然而,這種由自偏壓效應引起的刻蝕過程中各物質的運動速度不同,造成了RIE刻蝕離子與反應自由基的不匹配,在RIE刻蝕過程中,經常產生的“黑硅”現象就是該原理造成的。

圖1 RIE刻蝕結構示意圖

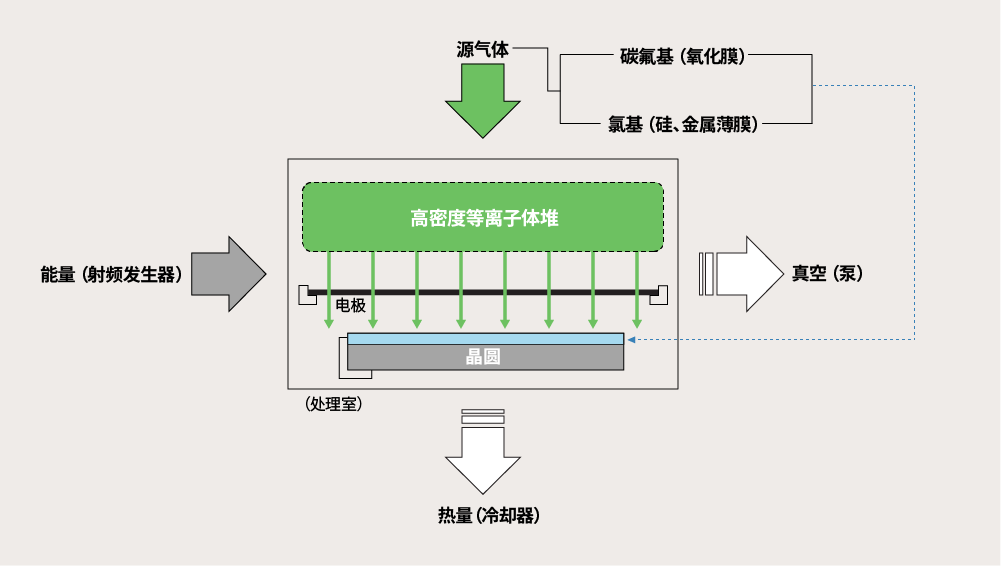

ICP

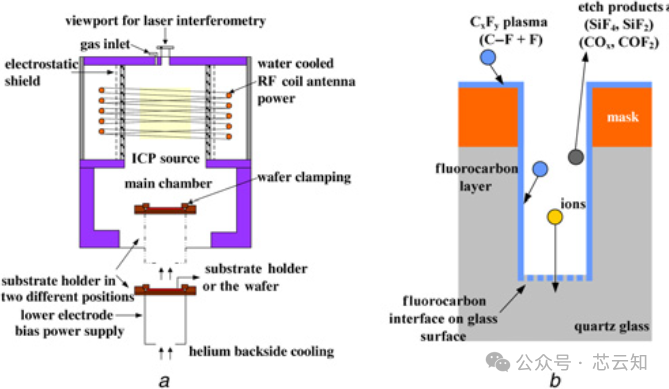

隨著工藝要求的不斷提高,研發人員開發了電感耦合等離子體刻蝕機(ICP),該設備克服了自由基、離子不匹配的問題,常用的ICP刻蝕機結構如圖2所示,一般由頂部通入刻蝕氣體,經過刻蝕腔側壁的RF線圈,被RF線圈施加的電場激發為等離子體,在腔體中形成明顯的輝光層;然后,通過在位于下電極上施加Bias的功率吸收等離子體中的刻蝕離子。相比RIE刻蝕技術,ICP刻蝕腔體一般具有較低的氣壓,更高密度的等離子體,可以通過射頻線圈功率、氣體流量、Bias功率的調控,實現更高速率,更高精度以及更大深寬比的刻蝕。

圖2右給出了ICP用C4F8刻蝕石英的過程,其中射頻放電C4F8產生的氟碳自由基會自發的形成鈍化層沉積在表面,然后在施加在晶圓表面的Bias作用下,正離子具有較高的速率延垂直于晶圓表面轟擊鈍化層以及刻蝕石英,實現石英的高深寬比刻蝕。

圖2 ICP刻蝕機構成和刻蝕示例

NLD

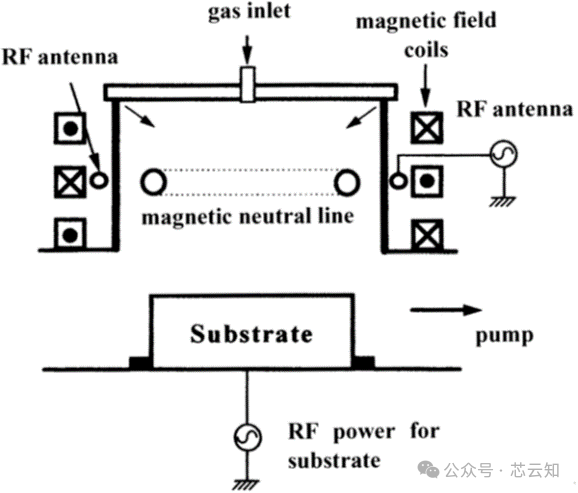

傳統ICP刻蝕射頻線圈會對刻蝕腔中的磁場產生影響,使得徑向的等離子體密度不一致,并干擾刻蝕離子的運動,從而影響刻蝕均勻性。研發人員進一步開發了磁中性環路放電,該設備的結構如圖3所示,其在ICP刻蝕線圈的外圍施加了三個控制磁場的線圈,通過控制三個線圈磁場的大小從而可以在刻蝕腔中形成磁中環強度為0的環境,從而產生更高密度以及分布均勻的等離子體。加以Bias的控制,NLD技術具有更好的刻蝕均勻性,更高的刻蝕速率。除常用的介質層外,也經常用于刻蝕碳化硅等耐刻蝕材料。

圖3 NLD刻蝕機結構

IBE

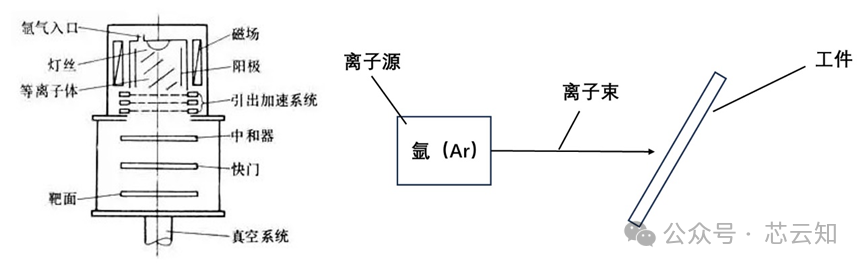

IBE刻蝕為純物理轟擊刻蝕,常用于氟基或者氯基等離子體無法刻蝕的材料,例如,金、銅、鉑等。常規IBE刻蝕機的結構如圖4所示,氬氣通過燈絲提供的電子將其離子化形成等離子體并離子源,然后通過電子引出加速系使離子均勻射向晶圓工件臺,最后通過轟擊固體表面原子,使材料原子發生濺射,達到刻蝕目的。

圖4 IBE刻蝕結構和離子束路徑

IBE的特點主要有:1)高方向性的中性離子束能夠控制側壁輪廓,優化刻蝕過程中的徑向均勻性和結構形貌。2)通過調整工件臺的角度可以通過傾斜晶圓從而改變離子束的撞擊方向實現側壁角度的控制。

審核編輯:湯梓紅

-

等離子體

+關注

關注

0文章

109瀏覽量

14129 -

晶圓

+關注

關注

52文章

4743瀏覽量

127276 -

刻蝕機

+關注

關注

0文章

47瀏覽量

4134

原文標題:MEMS常用干法刻蝕設備結構及原理

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

釋放MEMS機械結構的干法刻蝕技術

【轉帖】干法刻蝕的優點和過程

請教碳化硅刻蝕工藝

釋放MEMS機械結構的干法刻蝕技術

兩種基本的刻蝕工藝:干法刻蝕和濕法腐蝕

GaN材料干法刻蝕工藝在器件工藝中有著廣泛的應用

干法刻蝕之鋁刻蝕的介紹,它的原理是怎樣的

干法刻蝕工藝介紹

干法刻蝕解決RIE中無法得到高深寬比結構或陡直壁問題

干法刻蝕和清洗(Dry Etch and Cleaning)

工信部就干法刻蝕設備測試方法等行業標準公開征集意見

干法刻蝕常用設備的原理及結構

干法刻蝕常用設備的原理及結構

評論