電子發燒友網(文/吳子鵬)根據臺灣媒體的最新消息,臺積電1nm制程將落腳嘉義科學園區,臺積電已向相關管理局提出100公頃用地需求,其中40公頃將先設立先進封裝廠,后續的60公頃將作為1nm建廠用地。

對于這一傳聞,臺積電表示,選擇設廠地點有諸多考量因素,臺積電以中國臺灣地區作為主要基地,不排除任何可能性,也持續與管理局合作評估合適的半導體建廠用地。

產業人士預估,臺積電1nm的投資可能超過萬億新臺幣的級別。

1nm的技術難度極高,可能已經是極限

1nm被很多人定義為芯片制造工藝的極限,主要原因是,1nm確實已經逼近晶體管制造的物理極限,將會衍生出很多技術難題。

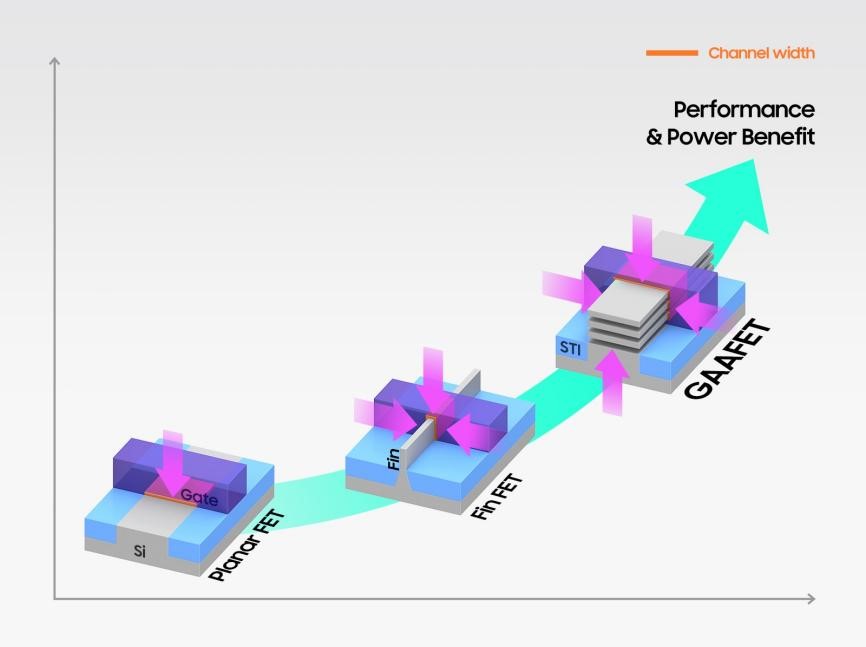

當前,先進制程的主要工藝結構是FinFET (鰭式場效應晶體管) ,又稱3D晶體管。FinFET使用Gate對Fin的包圍實現等效W值的增加,可以更有效地控制溝道區域,進而更好地控制電流流動,減少漏電流,并能夠有效抑制短溝道效應,提高了設備的性能和能效。

FinFET結構由襯底上的硅體薄(垂直)翅片組成,柵級圍繞通道提供了良好的通道三面控制。從22nm芯片一直用到5nm,FinFET都是首選結構。不過,到了3nm工藝后,靜態電流泄漏問題變得越來越嚴重——在3nm工藝里,FinFET對電流的控制能力急劇下降,同時漏電流也在升高。

臺積電計劃在2nm工藝里開始使用第三代工藝結構——GAA-FET(環繞式柵極場效晶體管),三星在3nm工藝里已經開始使用這種結構。GAA-FET通過四面環繞 Channel,實現對Channel 更強的控制,進一步減小短溝效應的影響。

圖源:三星半導體

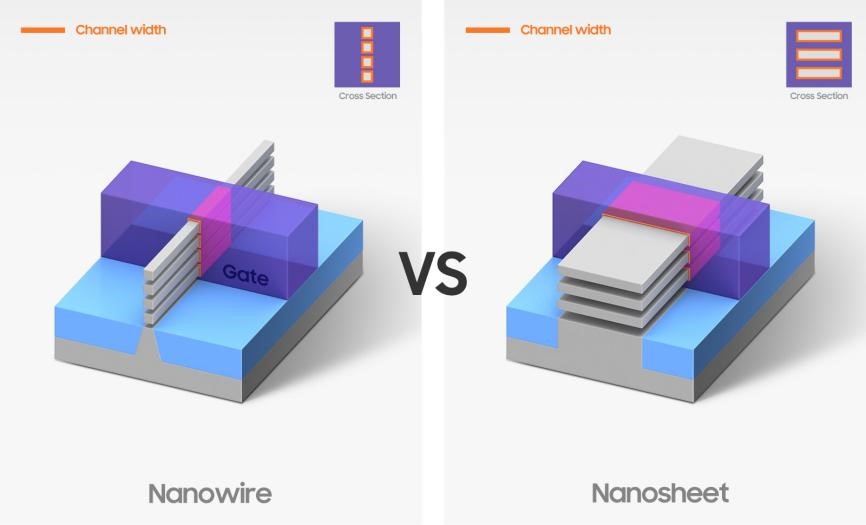

根據三星半導體的介紹,GAA結構有線型(Wire)和片型(Sheet)兩種形態。Nanowire GAA 必須堆疊多層Wire以加寬總溝道寬度,這使得工藝變得更加復雜。為了解決這個問題,三星半導體沒有選擇線型(Wire),而是采取了寬度更寬的片型(Sheet)形態的GAA,也就是MBCFET。

圖源:三星半導體

根據臺媒的報道,臺積電也已經正式順利實現GAA技術2nm制程。從工藝進度來說,2nm之后并不是馬上迎來1nm,而是1.4nm,現在的叫法可能是14A,之后就是1nm。臺積電此前透露,該公司已經于2022年開始組建1.4nm的團隊,因此現在啟動1nm研發也不意外。

在1nm量產中,預計三星和臺積電可能還會使用GAA-FET,不過可能會是GAA-FET的進一步演化版,IEDM會議上曾提到過,其中一個演化架構是Forksheet架構。英特爾則認為,可以使用堆疊式CFET場效應管架構,這也是一種GAA-FET的改進結果,屬于堆疊式的GAA-FET,將n型和p型MOS元件堆疊在一起。

不過即便是有結構改進,1nm還是需要面臨很多挑戰,比如更加突出的量子隧穿現象。該現象指出,當芯片制造工藝來到1nm時,電子會發生量子隧穿現象,這會導致晶體管的性能受到限制。量子隧穿實際上就是不受控制的漏電,造成不可控的發熱。

為了讓漏電可控,材料創新和結構創新一樣重要,為了實現1nm制程,業界很早就開始研發新材料以應對新挑戰。目前產業界已經證明,使用非硅材料可以實現1nm制程。2019年,IMEC就提出,2D材料可實現1nm以下的工藝節點。當時所采用的材料是二硫化鉬(MoS2) 。二硫化鉬一個重要的特性是可以以穩定的形式生長,厚度僅為一個原子,且在該尺度上具有原子精度。

臺積電同樣在進行2D材料的探索,臺積電和麻省理工學院、南洋理工大學曾聯合發表了一篇論文,描述單層材料如何受到金屬導電間隙的影響。論文指出,通過使用金屬鉍和一些半導體單層過渡金屬二硫族化物,可以實現更小的晶體管,這些2D材料包括二硫化鉬(MoS2)、二硫化鎢(WS2)和二硒化鎢(WSe2)。

很多業者認為,1nm量產面臨多方面的問題,很可能已經是芯片制造工藝的極限。

1nm芯片非常昂貴,光刻機就超過4億美元

除了技術和材料方面的挑戰之外,晶圓代工廠想要量產1nm,也需要承擔成本和客戶方面的風險,因為1nm工藝確實是太貴了。

有分析報告指出,想要制造1nm芯片,現有的光刻機都不能滿足需求。全球光刻機龍頭企業ASML預計,將會在2025年,也就是2nm量產之后再更新一代光刻機,基于High NA技術,將NA指標從當前的0.33提升到0.55,進一步提升光刻分辨率。這個下一代光刻機將主要用于1.4nm工藝的量產,售價是非常昂貴的,將達到4億美元,是現有光刻機價格的2.8倍。

然而,這可能還不是極限。ASML表示,這款0.55NA數值孔徑的EUV光刻機應該能夠支撐至少1.4納米芯片的制造,但對于1納米芯片而言,目前尚無確切明確的方案。那么,我們也可以理解為,如果再需要給1nm重新設計光刻機,價格可能會更高。然而,就現在這個1.5億美元的光刻機,以及工藝成本,已經讓臺積電有點吃不消了。回看臺積電從2022年第四季度到2023年第二季度的毛利率,從62.2%下降到了54.1%。就這樣,也就只有蘋果公司用得起。據悉,臺積電3nm工藝每片晶圓的價格大概是2萬美元,5nm時是1.6萬美元。臺媒指出,蘋果作為唯一的3nm用戶,擁有很強的議價能力,將3nm成本壓到一個很低的水平,進而導致臺積電毛利率承壓。而反觀高通,本來可以借助3nm進一步拉近和蘋果A系列的性能差距,不過由于價格太高,最終選擇了三星的工藝。

3nm都是如此了,很難想象,下面要經過2nm、1.4nm之后才能到1nm,屆時1nm的成本會達到一個怎樣的程度。

雖然1nm可能面臨無人用得起的情況,不過產業界對于量產1nm依然是趨之若鶩。先不說已經展開軍備競賽的臺積電和三星,英特爾對量產1nm也是信心滿滿,和臺積電一樣,甚至是比臺積電更早,英特爾也有自己的1萬億個晶體管的芯片封裝路線,在這個路線下,也包含1nm制造工藝。

根據此前的報道,日本芯片制造商Rapidus與東京大學聯手法國半導體研究機構Leti,也在共同開發1nm芯片。另外,IBM和IMEC也在致力于量產1nm。

當然,也有人質疑1nm的存在合理性。根據預期數據,1nm芯片相比于現有的5nm芯片,其性能可能提升20%至30%,而功耗可能降低25%至40%。不到50%的能效提升,卻需要為此支付數倍,甚至是數十倍的成本,終端市場可能很難接受這樣的芯片。

不過,贊同的人認為,1nm可能會通過材料創新等開啟芯片制造的新模式,我們無法用今天的眼光去定義未來的科技創新,就像我們當年從微米時代進入納米時代,以及40nm進入28nm一樣,1nm技術的高成本和復雜性也可能導致半導體行業的進一步集中,但同時也會出現更新的高性能運算應用來啟用1nm工藝。

結語

摩爾定律是一個經濟定律,雖然放緩了,不過還遠遠沒有到消亡的時刻。按照臺積電等廠商的計劃,預計將會在2026年量產1.4nm工藝,然后在2028年1nm將正式量產。不過,從目前的情況來看,延期是大概率事件。

1nm已經突破了硅材料的極限,因此除了需要更先進的光刻機等設備之外,材料創新也是一大重點,在此過程中,產業界可能會摸索到一條嶄新的工藝迭代路徑,將先進工藝水平繼續向下推進。站在現在的節點說,1nm太貴完全沒有必要,還為時過早。

-

臺積電

+關注

關注

44文章

5611瀏覽量

166160 -

FinFET

+關注

關注

12文章

247瀏覽量

90155 -

先進制程

+關注

關注

0文章

81瀏覽量

8412 -

1nm

+關注

關注

0文章

15瀏覽量

3910

發布評論請先 登錄

相關推薦

臺積電8月營收預計同比飆升,再創歷史新高

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

臺積電Q2凈利潤2478.5億元新臺幣

臺積電Q1營收5926.4億元新臺幣,同比增長16.5%

臺積電加大投資先進封裝,將在嘉科新建六座封裝廠

臺積電:最有錢20人,身價破億元新臺幣

蘋果欲優先獲取臺積電2nm產能,預計2024年安裝設備生產

臺積電1nm晶圓廠最新動向,嘉義成首選地

臺積電宣布斥資逾萬億新臺幣,在嘉義科學園區設立1nm制程代工廠

臺積電1nm進展曝光!預計投資超萬億新臺幣,真有必要嗎?

臺積電1nm進展曝光!預計投資超萬億新臺幣,真有必要嗎?

評論