在本系列第三篇文章中,我們介紹了傳統(tǒng)封裝和晶圓級(Wafer-Level)封裝,本篇文章將繼續(xù)介紹將多個(gè)封裝和組件整合到單個(gè)產(chǎn)品中的封裝技術(shù)。其中,我們將重點(diǎn)介紹封裝堆疊技術(shù)和系統(tǒng)級封裝(SiP)技術(shù),這兩項(xiàng)技術(shù)都有助減小封裝體積,提高封裝工藝效率。

01

堆疊封裝 (Stacked Packages)

想象一下,在一個(gè)由多棟低層樓房組成的住宅綜合體內(nèi),若要容納數(shù)千名居民,則需要占據(jù)非常大的面積才能滿足需求。然而,一棟摩天大樓就能容納同樣數(shù)量的居民。這個(gè)例子清楚地說明了堆疊封裝具備的一大優(yōu)勢。相對于將多個(gè)封裝水平分布在較大面積的產(chǎn)品,由堆疊封裝(Stacked Package)組成的產(chǎn)品可以在減小體積的同時(shí)進(jìn)一步提高性能。除了作為一種重要封裝技術(shù),堆疊封裝還是產(chǎn)品開發(fā)過程中采用的一種基本方法。

過去,產(chǎn)品往往在一個(gè)封裝體內(nèi)只封裝一個(gè)芯片,但現(xiàn)在可以開發(fā)涵蓋多種不同功能的多芯片封裝或?qū)⒍鄠€(gè)存儲(chǔ)器芯片集成到容量更大的單個(gè)封裝中。此外,系統(tǒng)級封裝可將多個(gè)系統(tǒng)組件整合在單個(gè)封裝體內(nèi)。這些技術(shù)的問世使半導(dǎo)體公司能夠在打造高附加值產(chǎn)品的同時(shí),滿足多樣化的市場需求。

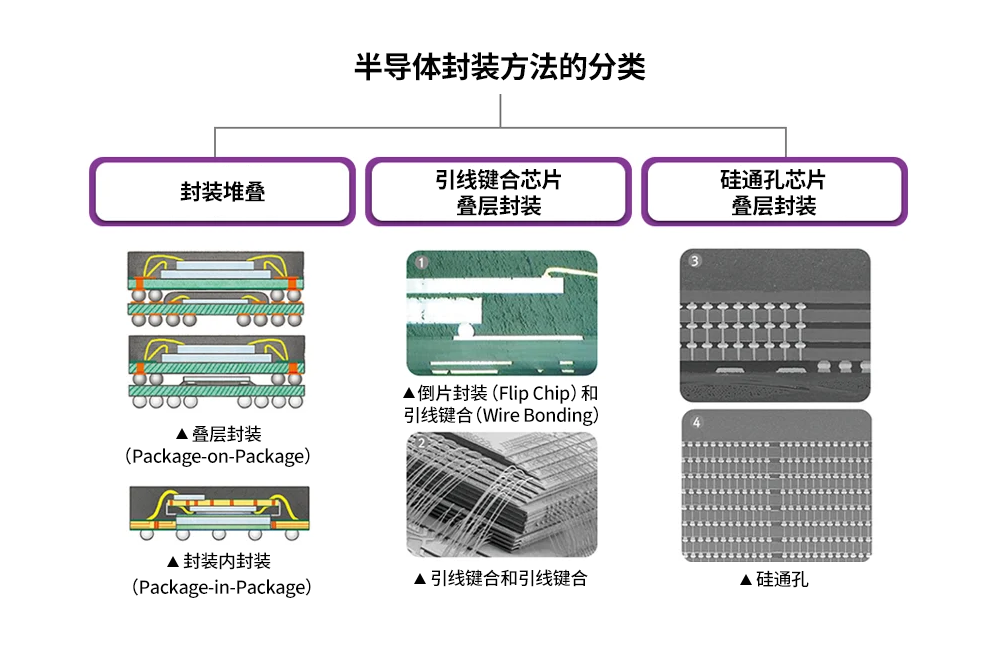

▲圖1:堆疊封裝方法的分類(? HANOL出版社)

如圖1所示,基于不同的開發(fā)技術(shù),堆疊封裝可分為三大類:

1)通過垂直堆疊封裝體而形成的封裝堆疊;2)使用引線鍵合技術(shù)將不同芯片堆疊在單個(gè)封裝體內(nèi)的芯片疊層封裝;及3)使用硅通孔(TSV)1技術(shù)替代傳統(tǒng)引線鍵合技術(shù)實(shí)現(xiàn)內(nèi)部電氣互連的芯片疊層封裝技術(shù)。每種堆疊封裝技術(shù)都具有不同的特點(diǎn)、優(yōu)勢和局限性,這將決定它們在未來的應(yīng)用。

1 硅通孔(TSV,Through Silicon Via):一種可完全穿過硅裸片或晶圓實(shí)現(xiàn)硅片堆疊的垂直互連通道。

封裝堆疊

(Package Stacks))

封裝堆疊通過垂直堆疊封裝體來實(shí)現(xiàn)。因此,其優(yōu)缺點(diǎn)與芯片疊層封裝正好相反。封裝堆疊方法將完成測試的封裝體相堆疊,在某個(gè)封裝體測試不合格時(shí),可輕松地將其替換為功能正常的封裝體。因而,其測試良率相比芯片疊層封裝更高。然而,封裝堆疊尺寸較大且信號(hào)路徑較長,這導(dǎo)致其電氣特性可能要劣于芯片疊層封裝。

最常見的一種封裝堆疊技術(shù)便是疊層封裝(PoP),它被廣泛應(yīng)用于移動(dòng)設(shè)備中。對于針對移動(dòng)設(shè)備的疊層封裝,用于上下層封裝的芯片類型和功能可能不同,同時(shí)可能來自不同芯片制造商。

通常,上層封裝體主要包括由半導(dǎo)體存儲(chǔ)器公司生產(chǎn)的存儲(chǔ)器芯片,而下層封裝體則包含帶有移動(dòng)處理器的芯片,這些芯片由無晶圓廠的設(shè)計(jì)公司設(shè)計(jì),并由晶圓代工廠及外包半導(dǎo)體組裝和測試(OSAT)設(shè)施生產(chǎn)。由于封裝體由不同廠家生產(chǎn),因此在堆疊前需進(jìn)行質(zhì)量檢測。即使在堆疊后出現(xiàn)缺陷,只需將有缺陷的封裝體替換成新的封裝體即可。因此封裝堆疊在商業(yè)層面具有更大益處。

芯片堆疊(Chip Stacks)-

引線鍵合芯片疊層封裝

(Chip Stacks With Wire Bonding)

將多個(gè)芯片封裝在同一個(gè)封裝體內(nèi)時(shí),既可以將芯片垂直堆疊,也可以將芯片水平連接至電路板。考慮到水平布局可能導(dǎo)致封裝尺寸過大,因而垂直堆疊成為了首選方法。相比封裝堆疊,芯片堆疊封裝尺寸更小,且電信號(hào)傳輸路徑相對更短,因而電氣特性更優(yōu)。然而,若在測試中發(fā)現(xiàn)某個(gè)芯片存在缺陷,則整個(gè)封裝體就會(huì)報(bào)廢。鑒于此,芯片堆疊封裝的測試良率較低。

在芯片堆疊封裝中,要想提高存儲(chǔ)器容量,就需要在單一封裝中堆疊更多的芯片。因而,可將多個(gè)芯片集成在同一封裝體內(nèi)的技術(shù)應(yīng)運(yùn)而生。但與此同時(shí),人們不希望封裝厚度隨著堆疊芯片數(shù)量的增加而變厚,因此致力于開發(fā)能夠限制封裝厚度的技術(shù)。要做到這一點(diǎn),就需要減少芯片和基板(Substrate)等可能影響封裝厚度的所有組件的厚度,同時(shí)縮小最上層芯片和封裝上表面之間的間隙。這給封裝工藝帶來了諸多挑戰(zhàn),因?yàn)樾酒奖≡揭子趽p壞。因此,目前的封裝工藝正致力于克服這些挑戰(zhàn)。

硅通孔(TSV)-

硅通孔芯片疊層封裝

(Chip Stacks With TSV)

硅通孔是一種通過在硅片上鉆孔來容納電極的芯片堆疊技術(shù)。相比采用傳統(tǒng)引線方法實(shí)現(xiàn)芯片與芯片(Chip-to-Chip)互連或芯片與基板(Chip-to-Substrate)互連,硅通孔通過在芯片上鉆孔并填充金屬等導(dǎo)電材料來實(shí)現(xiàn)芯片垂直互連。盡管使用硅通孔進(jìn)行堆疊時(shí)使用了芯片級工藝,但卻采用晶圓級工藝在芯片正面和背面形成硅通孔和焊接凸點(diǎn)(Solder Bump)。由此,硅通孔被歸類為晶圓級封裝技術(shù)。

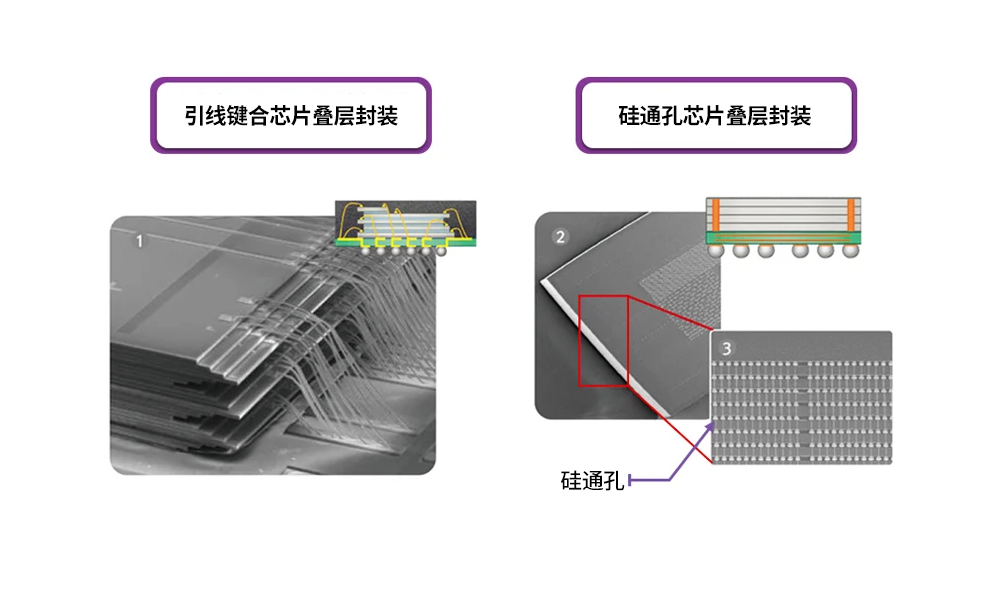

▲圖2:使用硅通孔技術(shù)的芯片剖面圖(? HANOL出版社)

硅通孔封裝的主要優(yōu)勢在于性能優(yōu)越且封裝尺寸較小。如圖2所示,使用引線鍵合的芯片堆疊封裝利用引線連接至各個(gè)堆疊芯片的側(cè)面。由于堆疊芯片以及連接引腳(Pin)的數(shù)量增加,引線變得更加復(fù)雜,而且也需要更多空間來容納這些引線。相比之下,硅通孔芯片堆疊則不需要復(fù)雜的布線,因而封裝尺寸更小。

正如上一篇文章所介紹,倒片封裝(Flip Chip)具有良好的電氣特性,原因有以下幾點(diǎn):其更易在理想位置形成輸入/輸出(I/O)引腳;引腳數(shù)量增加;電信號(hào)傳輸路徑較短。基于同樣的原因,硅通孔封裝也具有良好的電氣特性。當(dāng)從一個(gè)芯片向其下方的芯片發(fā)送電信號(hào)時(shí),硅通孔封裝使得信號(hào)能夠直接向下傳輸。相反,如果使用引線鍵合封裝,則信號(hào)會(huì)先向下傳輸至基板,隨后再向上傳輸至芯片,因而信號(hào)傳輸路徑要長得多。如圖2所示的引線芯片堆疊,芯片中心無法進(jìn)行引線連接。相反,硅通孔封裝可在芯片中心鉆孔,形成電極,并與其他芯片連接。與引線連接不同,硅通孔封裝可大幅增加引腳數(shù)量。

高寬帶存儲(chǔ)器(HBM)采用一種全新的DRAM架構(gòu),這種架構(gòu)借助硅通孔技術(shù)來增加引腳數(shù)量。通常,在DRAM規(guī)范中,“X4”表示有四個(gè)引腳用于發(fā)送信息,或可以同時(shí)從DRAM發(fā)送4位(bit)信息。相應(yīng)地,X8表示8位,X16表示16位,以此類推。增加引腳數(shù)量有利于同時(shí)發(fā)送更多信息。然而,由于自身局限性,引線芯片堆疊最多只能達(dá)到X32,而硅通孔堆疊則沒有這方面的局限性,使HBM可達(dá)到x1024。

目前,將硅通孔封裝用于DRAM的量產(chǎn)存儲(chǔ)器產(chǎn)品,包括HBM和3D堆疊存儲(chǔ)器(3DS)。前者用于圖形、網(wǎng)絡(luò)和高性能計(jì)算(HPC)應(yīng)用,而后者則主要用作DRAM存儲(chǔ)器模塊。

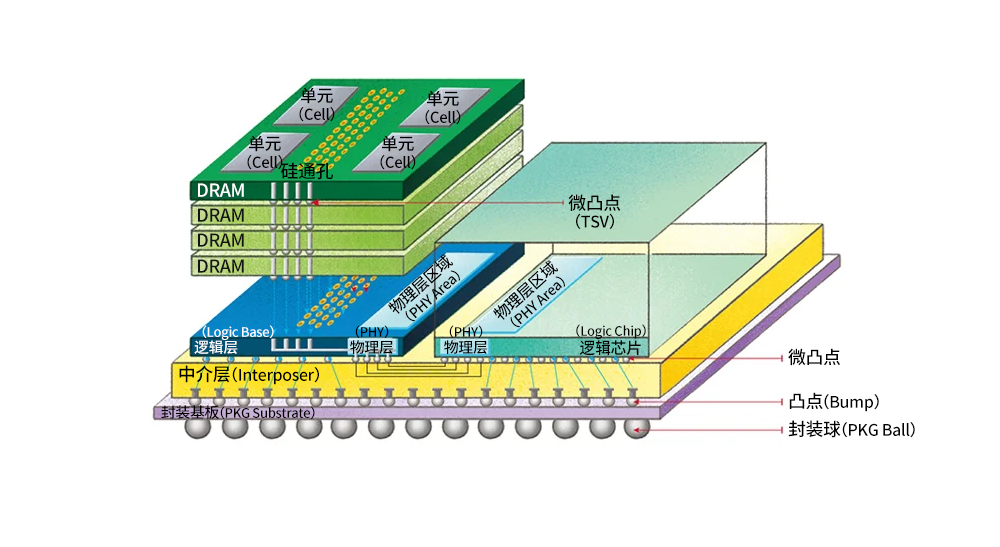

▲圖3:使用HBM的2.5D封裝(? HANOL出版社)

HBM并非一種全封裝產(chǎn)品,而是一種半封裝產(chǎn)品。當(dāng)HBM產(chǎn)品被送到系統(tǒng)半導(dǎo)體制造商那里時(shí),系統(tǒng)半導(dǎo)體制造商會(huì)使用中介層2構(gòu)建一個(gè)2.5D封裝3,將HBM與邏輯芯片并排排列,如圖3所示。由于2.5D封裝中的基板無法提供用于支持HBM和邏輯芯片的所有輸入/輸出引腳的焊盤(Pads),因此需要使用中介層來形成焊盤和金屬布線,從而容納HBM和邏輯芯片。然后,再將這些中介層與基板連接。這些2.5D封裝被認(rèn)為是一種系統(tǒng)級封裝。

同樣采用硅通孔封裝的產(chǎn)品還有3DS DRAM,這是一種在PCB板上安裝球柵陣列封裝(BGA)4的內(nèi)存模塊。盡管服務(wù)器中的DRAM存儲(chǔ)器模塊需要高速傳輸和大容量存儲(chǔ),但使用引線鍵合的芯片堆疊封裝因其速度局限性而無法滿足這些要求。鑒于此,服務(wù)器等高端系統(tǒng)往往使用由硅通孔芯片堆疊封裝構(gòu)成的模塊。

2 中介層(Interposer):用于2.5D配置中的裸片之間又寬又快的電信號(hào)管道。

3 2.5D封裝(2.5D package):2.5D和3D封裝在每個(gè)封裝中包含多個(gè)集成電路。在2.5D結(jié)構(gòu)中,兩個(gè)或多個(gè)有源半導(dǎo)體芯片(Active Semiconductor Chips)并排排列在硅中介層上。在3D結(jié)構(gòu)中,有源芯片通過裸片垂直堆疊的方式集成在一起。

4 球柵陣列封裝(BGA):一種表面貼裝芯片封裝,使用錫球作為其連接器。

02

系統(tǒng)級封裝(SiP)

由HBM和邏輯芯片構(gòu)成的封裝屬于系統(tǒng)級封裝。顧名思義,系統(tǒng)級封裝是指在單個(gè)封裝體中集成一個(gè)系統(tǒng)。然而,完整的系統(tǒng)還需包括傳感器、模擬數(shù)字(A/D)轉(zhuǎn)換器、邏輯芯片、存儲(chǔ)芯片、電池和天線等組件,但就目前的技術(shù)發(fā)展水平而言,還無法將所有這些系統(tǒng)組件集成到單個(gè)封裝體內(nèi)。因此,研究人員正致力于不斷開發(fā)針對這一領(lǐng)域的封裝技術(shù),而當(dāng)前的系統(tǒng)級封裝是指在單個(gè)封裝體內(nèi)集成部分系統(tǒng)組件。例如,使用HBM的封裝將HBM和邏輯芯片集成到單個(gè)封裝體內(nèi),形成一個(gè)系統(tǒng)級封裝。

不同于系統(tǒng)級封裝,系統(tǒng)級芯片(SoC)在芯片級實(shí)現(xiàn)系統(tǒng)功能。換言之,在同一個(gè)芯片上實(shí)現(xiàn)多個(gè)系統(tǒng)功能。例如,目前大多數(shù)處理器都在芯片內(nèi)集成了靜態(tài)RAM(SRAM)存儲(chǔ)器,可同時(shí)在單個(gè)芯片上實(shí)現(xiàn)處理器的邏輯功能和SRAM的存儲(chǔ)功能。因此,這些處理器被歸類為系統(tǒng)級芯片。

系統(tǒng)級芯片需要將多種功能組合到單個(gè)芯片中,因此開發(fā)流程復(fù)雜而漫長。此外,如要對已開發(fā)出來的系統(tǒng)級芯片中單個(gè)元件的功能進(jìn)行升級,則需從頭開始對它們進(jìn)行設(shè)計(jì)和開發(fā)。而系統(tǒng)級封裝開發(fā)起來則更容易也更快,這是由于系統(tǒng)級封裝是通過將已開發(fā)的多個(gè)芯片和器件整合在單個(gè)封裝體內(nèi)來實(shí)現(xiàn)。由于芯片本身是單獨(dú)開發(fā)和制造,即使器件的結(jié)構(gòu)完全不同,也很容易將它們集成到單個(gè)封裝體內(nèi)。同時(shí),如果只需對功能的一個(gè)方面進(jìn)行升級,則無需從頭開發(fā)封裝就可在芯片內(nèi)集成新開發(fā)的器件。然而,如果產(chǎn)品將被長期大量使用,則相比系統(tǒng)級封裝而言,將其開發(fā)為系統(tǒng)級芯片將更高效,因?yàn)橄到y(tǒng)級封裝需要制造的材料更多,這會(huì)增加封裝體積,只有這樣才能將多個(gè)芯片整合到單個(gè)封裝體內(nèi)。

盡管系統(tǒng)級芯片和系統(tǒng)級封裝之間存在各種差異,但兩者并不是非此即彼的關(guān)系。事實(shí)上,可以將兩者結(jié)合起來,以產(chǎn)生協(xié)同效應(yīng)。完成系統(tǒng)級芯片開發(fā)后,可將其與其他功能芯片封裝到單個(gè)封裝體內(nèi),然后作為增強(qiáng)型系統(tǒng)級封裝來實(shí)現(xiàn)。

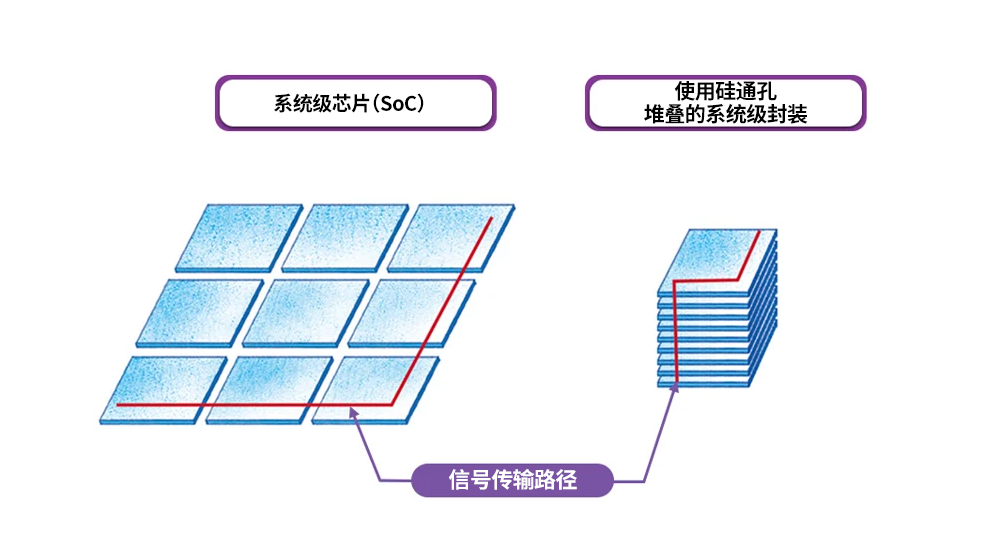

▲圖4:使用硅通孔堆疊的系統(tǒng)級芯片和系統(tǒng)級封裝的信號(hào)傳輸路徑長度比較(? HANOL出版社)

在對系統(tǒng)級封裝和系統(tǒng)級芯片的性能進(jìn)行比較時(shí),人們原本以為系統(tǒng)級芯片在單個(gè)芯片上實(shí)現(xiàn),因而其電氣特性會(huì)更優(yōu)異。然而,隨著芯片堆疊技術(shù)(如硅通孔技術(shù))的發(fā)展,系統(tǒng)級封裝的電氣特性與系統(tǒng)級芯片旗鼓相當(dāng)。圖4對使用硅通孔堆疊的系統(tǒng)級芯片和系統(tǒng)級封裝的信號(hào)傳輸路徑進(jìn)行了比較。當(dāng)信號(hào)從系統(tǒng)級芯片的一端傳輸?shù)綄堑牧硪欢藭r(shí),將系統(tǒng)級芯片分為9個(gè)部分并使用硅通孔技術(shù)進(jìn)行堆疊時(shí),傳輸路徑會(huì)短得多。

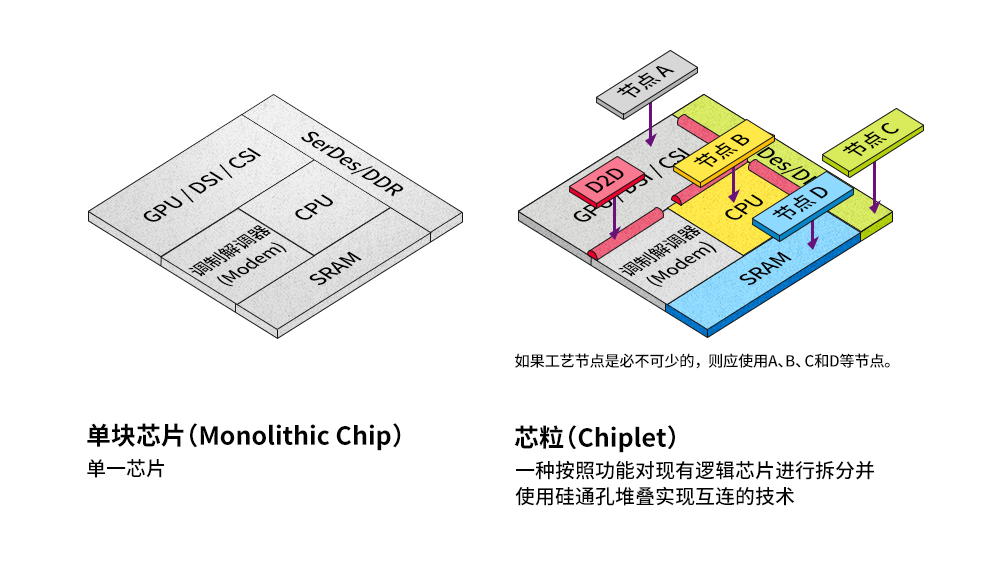

▲圖5:芯粒概念圖

除了使用硅通孔堆疊的系統(tǒng)級封裝因具備各種優(yōu)勢而成為焦點(diǎn)之外,近年來一種稱為芯粒(Chiplets)的技術(shù)也受到了廣泛關(guān)注。如圖5所示,這種技術(shù)按照功能對現(xiàn)有邏輯芯片進(jìn)行拆分,并通過硅通孔技術(shù)對它們進(jìn)行連接。與單塊芯片相比,芯粒擁有三大優(yōu)勢。

首先,芯粒的良率較單塊芯片有所提高。當(dāng)晶圓(Wafer)上芯片的尺寸較大時(shí),則晶圓良率就會(huì)受到限制,而縮小芯片尺寸可提高晶圓良率,從而降低制造成本。例如,將一個(gè)直徑為300毫米的晶圓切割為100或1000個(gè)芯片(裸片)。如果在晶圓加工過程中,由于晶圓正面平均分布著五種雜質(zhì)而導(dǎo)致五個(gè)芯片出現(xiàn)缺陷,則切割為100個(gè)芯片的產(chǎn)品良率為95%,而切割為1000個(gè)芯片的產(chǎn)品良率則為99.5%。因此,包含裸片數(shù)量越多或芯片尺寸越小的產(chǎn)品,其良率越高。鑒于此,按照功能對芯片進(jìn)行拆分,并將其作為系統(tǒng)級封裝而非系統(tǒng)級芯片中的單個(gè)芯片,有助于提高成本效益。

第二個(gè)優(yōu)勢是開發(fā)流程得到簡化。對于單個(gè)芯片而言,如需升級芯片功能或采用最新技術(shù),則需重新開發(fā)整個(gè)芯片。然而,如果對芯片進(jìn)行分割,則只需對具有相關(guān)功能的芯片進(jìn)行升級或使用最新技術(shù)對其進(jìn)行開發(fā)即可,因而可縮短開發(fā)周期,提高工藝效率。例如,可以針對一些分割芯片采用現(xiàn)有的20納米(nm)技術(shù),同時(shí)針對其他芯片采用最新的10納米以下技術(shù),以此提高開發(fā)效率。

第三個(gè)優(yōu)勢是可促進(jìn)技術(shù)開發(fā)集中化。由于芯片按照功能進(jìn)行劃分,因而無需針對每個(gè)功能來開發(fā)相應(yīng)的芯片。只需開發(fā)用于核心技術(shù)的芯片,而其他芯片則可以通過購買或外包獲取,這樣企業(yè)就可以專注于開發(fā)自己的核心技術(shù)。

鑒于這些優(yōu)點(diǎn),主要半導(dǎo)體廠商正在引入基于芯粒技術(shù)的半導(dǎo)體產(chǎn)品或?qū)⑵浼{入自身的發(fā)展路線圖。

在上一篇文章中,我們介紹了各種傳統(tǒng)封裝和晶圓級封裝技術(shù),而本篇文章則對更多封裝技術(shù)及其不同特點(diǎn)進(jìn)行了綜述。目前,堆疊封裝和系統(tǒng)級封裝技術(shù)已取得長足發(fā)展,半導(dǎo)體研究人員將繼續(xù)致力于提高這些高質(zhì)量技術(shù)的能力,在提高其功能的同時(shí),盡量縮小其占用的空間。通過生產(chǎn)兼具尺寸、功能和性能優(yōu)勢的封裝產(chǎn)品,封裝工藝的效率有望得到進(jìn)一步提升。

審核編輯:劉清

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7366瀏覽量

163104 -

晶圓

+關(guān)注

關(guān)注

52文章

4745瀏覽量

127293 -

半導(dǎo)體封裝

+關(guān)注

關(guān)注

4文章

237瀏覽量

13623 -

TSV

+關(guān)注

關(guān)注

4文章

105瀏覽量

81373

原文標(biāo)題:半導(dǎo)體后端工藝|第四篇:了解不同類型的半導(dǎo)體封裝(第二部分)

文章出處:【微信號(hào):SKhynixchina,微信公眾號(hào):SK海力士】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

實(shí)現(xiàn)免調(diào)整VCO1的IC (第二部分)

中國NB-IOT產(chǎn)業(yè)聯(lián)盟-第二部分問題清單-20160824

2012年P(guān)SoC數(shù)模混合設(shè)計(jì)培訓(xùn)_第二部分

如何實(shí)現(xiàn)更高的系統(tǒng)效率——第二部分:高速柵極驅(qū)動(dòng)器

設(shè)計(jì)一臺(tái)物聯(lián)網(wǎng)模塊燈——第二部分

第四篇:了解不同類型的半導(dǎo)體封裝(第二部分)

第四篇:了解不同類型的半導(dǎo)體封裝(第二部分)

評論