EMC:Electro Magnetic Compatibility的簡稱,也稱電磁兼容,各種電氣或電子設備在電磁環境復雜的共同空間中,以規定的安全系數滿足設計要求的正常工作能力。

本章對于 RK3588產品設計中的 ESD/EMI防護設計及EMC的設計檢查給出了建議,幫助大家更好的提高產品的抗靜電、抗電磁干擾水平。

EMC設計檢查建議

按照設計流程,一個產品Layout完成之后,需要進入嚴格的評審環節,所設計的產品是否滿足ESD或者EMI防護設計要求,撇開原理圖設計,PCB設計一般需要我們從PCB布局和PCB布線兩個方面進行審查,本小節就這兩方面的檢查做了建議,讀者可以此作為審核PCB Layout人員的PCB的參考標準。

EMC設計布局檢查建議

1、整體布局檢查建議

2)高速、中速、低速電路要分開;

3)強電流、高電壓、強輻射元器件遠離弱電流、低電壓、敏感元器件;

4)多層板設計,必須要有單獨的電源平面和地平面;

5)對熱敏感的元件(含液態介質電容、晶振)盡量遠離大功率的元器件、散熱器等熱源。

2、接口與保護布局檢查建議

1)一般電源防雷保護器件的順序是:壓敏電阻→保險絲→抑制二極管→EMI濾波器→電感或者共模電感,對于原理圖缺失上面任一器件進行順延布局;

2)一般對接口信號的保護器件的順序是:ESD(TVS管)→隔離變壓器→共模電感→電容→電阻,對于原理圖缺失上面任一器件進行順延布局;

3)電平變換芯片(如RS232)要靠近連接器的位置(如串口)放置;

4)易受ESD干擾的器件,如NMOS、CMOS器件等,要盡量遠離易受ESD干擾的區域(如單板的邊緣區域)。

3、時鐘電路布局檢查建議

1)時鐘電路的濾波器(盡量采用“∏”型濾波)要靠近時鐘電路的電源輸入管腳;

2)晶體、晶振和時鐘分配器的布局要注意遠離大功率的元器件、散熱器等發熱的器件;

3)晶體、晶振和時鐘分配器與相關的IC器件要盡量靠近;

4)晶振距離板邊和接口器件要大于1inch的距離。

4、開關電源布局檢查建議

1)開關電源要遠離ADDA轉換器、模擬器件、敏感器件、時鐘器件;

2)嚴格按照原理圖的要求進行布局,不要將開關電源的電容隨意放置;

3)開關電源布局要緊湊,輸入輸出要分開。

5、電容與濾波器件布局檢查建議

1)原則上每個電源管腳放置一個0.1uf的小電容、一個集成電路放置一個或多個10uf大電容,可以根據具體情況進行增減;

2)電容務必要靠近電源管腳放置,而且容值越小的電容要越靠近電源管腳;

3)EMI濾波器要靠近芯片電源的輸入口。

6、疊層檢查建議

1)多層板(四層以上)至少有一個連續完整的地平面用來控制PCB的阻抗和信號質量;

2)電源平面和地平面靠近放置;

3)疊層盡量避免兩個信號層相鄰,如果相鄰加大兩個信號層的間距,并且布線時應該錯位布線,不能重疊布線,否側后期布線可能會引起串擾的產生;

4)避免兩個電源平面相鄰,特別是由于信號層鋪電源而導致的電源平面相鄰;

5)外層鋪地。

7、其他設計檢查建議

1)整機設計為浮地設備時,建議各接口不要分地設計;

2)機器外殼為金屬時,電源是三孔,要求金屬外殼必須良好連接大地。

EMC設計布線檢查建議

1、整體布線檢查建議

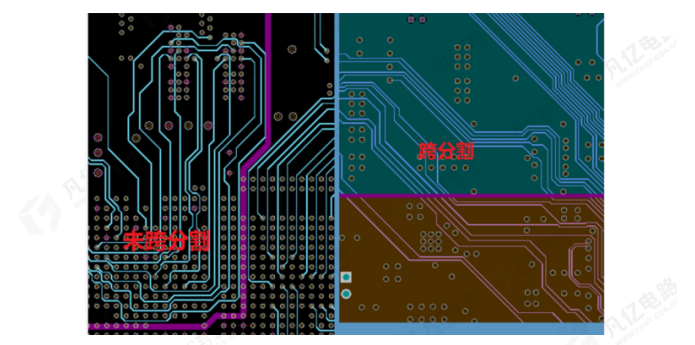

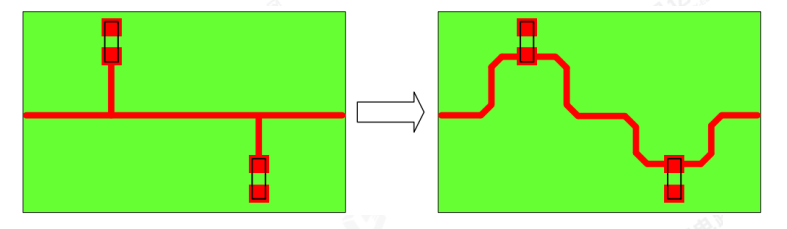

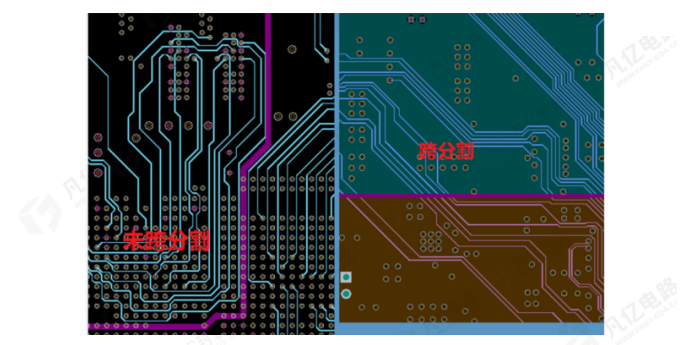

1)關鍵信號線走線避免跨分割

我們PCB中的信號都是阻抗線,是有參考的平面層,對于設計的關鍵信號避免跨分割的現象出現,否則會導致信號阻抗的突變,導致信號完整性問題的出現。如圖10,描述了信號跨分割的現象。

圖10 信號跨分割

2)相同功能的總線要并行走、中間不要夾叉其它信號,如果空間允許可以進行包地處理;

3)關鍵信號線走線避免“U”型或“O”型;

4)關鍵信號線走線不要人為的繞長(以最短路徑進行走線);

5)關鍵信號線需要距離邊沿和接口400mil以上;

6)晶振下面所有層都不能走線;

7)開關電源下面不能走線,特別是電感或轉換芯片下方;

8)接收和發送信號要分開走,不能互相交叉布線。

2、隔離與保護

1)浪涌抑制器件(TVS管、壓敏電阻)對應的信號走線盡量表層,短且粗(一般10mil以上);

2)不同接口之間的走線要清晰,不要互相交叉布線;

3)接口線到所連接的保護和濾波器件布線要盡量短;

4)接口線必需要先經過保護或濾波器件再到信號接收芯片;

5)接口器件的固定孔要接到保護地上,連接到機殼的定位孔、扳手要直接接到信號地;

6)變壓器、光耦等器件的輸入輸出地要分開處理(兩端使用不同的GND);

3、時鐘布線

1)超過1inch的時鐘線盡量走在內層,時鐘線采用立體包地處理;

2)時鐘線換層為不同的地參考平面需要增加回流地過孔;

3)時鐘線不允許跨分割;

4)時鐘線與其它信號線的間距達到5W,空間允許的情況下可以進行包地處理。

5)時鐘電路的電源走線需要加寬或鋪銅處理;

4、其他

1)保護地和信號地之間的間距大于80mil;

2)DC48V的爬電間距是否為80mil以上;

3)電源平面要比地平面內縮“20H”(H為電源和地平面的距離),一般情況地內縮20mil,電源需要內縮60mil,并間隔150mil打地過孔;

4)布線要避免出線Stub線,Stub線就是俗稱的線頭或歪線, 或者說信號沒打算經過的路徑;

5)AC220V的爬電間距最少為300mil,具體可以查爬電間距規格表;

6)差分走線可以抑制共模干擾;

7)敏感的信號線必須采用包地處理,包地線每隔200mil增加一個GND孔。

來源: 本文轉載自凡億電路公眾號

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23010瀏覽量

396337 -

Layout

+關注

關注

14文章

402瀏覽量

61658 -

emc

+關注

關注

169文章

3877瀏覽量

182876 -

電磁干擾

+關注

關注

36文章

2287瀏覽量

105313

原文標題:EMC設計檢查建議,讓PCB layout達到最佳性能!

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EMC設計布局布線檢查建議

EMC設計布局布線檢查建議

評論