近年來,隨著中國新基建、中國制造 2025 規(guī)劃的持續(xù)推進(jìn),單 ARM 處理器越來越難勝任工業(yè)現(xiàn)場的功能要求,特別是如今能源電力、工業(yè)控制、智慧醫(yī)療等行業(yè),往往更需要 ARM + FPGA 架構(gòu)的處理器平臺來實(shí)現(xiàn)例如多路 / 高速 AD 采集、多路網(wǎng)口、多路串口、多路 / 高速并行 DI/DO、高速數(shù)據(jù)并行處理等特定功能,因此 ARM + FPGA 架構(gòu)處理器平臺愈發(fā)受市場歡迎。

ARM + FPGA 架構(gòu)能帶來性能、成本、功耗等綜合比較優(yōu)勢,ARM 與 FPGA 既可各司其職,各自發(fā)揮原本架構(gòu)的獨(dú)特優(yōu)勢,亦可相互協(xié)作處理更復(fù)雜的問題。

ARM + FPGA 常見的通信方式有 PCIe、FSPI、I2C、SDIO、CSI 等,今天主要介紹基于 FSPI 的 ARM + FPGA 通信方式。

FSPI 總線特點(diǎn)介紹

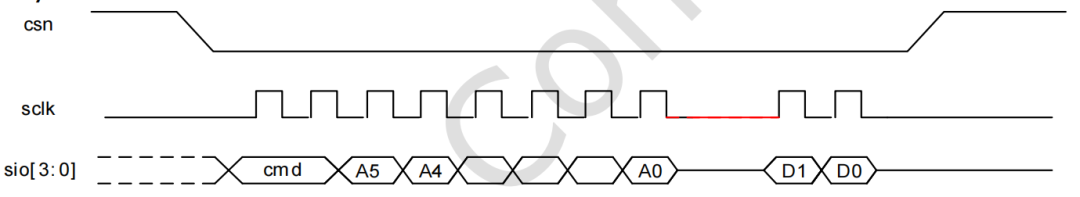

FSPI(Flexible Serial Peripheral Interface) 是一種高速、全雙工、同步的串行通信總線,在 RK3568 處理器中就有 ESPI 控制器,可用來連接 FSPI 設(shè)備。它具備如下特點(diǎn):

-支持串行 NOR FLASH、串行 NAND FLASH

-支持 SDR 模式

-支持一線、二線以及四線模式

相比 PCIe 而言,F(xiàn)SPI 可較好實(shí)現(xiàn) “小數(shù)據(jù) - 低時(shí)延”、“大數(shù)據(jù) - 高帶寬” 要求。另外,在與 FPGA 通信的時(shí)候,用戶往往更喜歡選用 FSPI 接口還有如下原因:

-使用低成本 FPGA即可實(shí)現(xiàn)高速通信,而具備 PCIe 接口的 FPGA 成本則成倍增長。

-具備 PCIe 接口的 FPGA 功耗往往較大,而低成本 FPGA功耗較小。一般而言,低功耗器件的使用壽命也將更長。

基于 FSPI 的 ARM + FPGA 通信實(shí)測數(shù)據(jù)分享

硬件方案一:創(chuàng)龍科技 TL3568F-EVM 評估板 (RK3568J + Logos-2)。

實(shí)測數(shù)據(jù):寫速率 20MB/s+,最高 24MB/s,誤碼率 0%;讀速率 26MB/s+,最高 30MB/s,誤碼率 0%。

TL3568F-EVM 評估板簡介:

創(chuàng)龍科技 TL3568F-EVM 是一款基于瑞芯微 RK3568J/RK3568B2 四核 ARM Cortex-A55 處理器 + 紫光同創(chuàng) Logos-2 PG2L50H/PG2L100H FPGA 設(shè)計(jì)的異構(gòu)多核國產(chǎn)工業(yè)評估板,由核心板和評估底板組成,ARM Cortex-A55 處理單元主頻高達(dá) 1.8GHz/2.0GHz。核心板 ARM、FPGA、ROM、RAM、電源、晶振、連接器等所有元器件均采用國產(chǎn)工業(yè)級方案,國產(chǎn)化率 100%。同時(shí),評估底板大部分元器件亦采用國產(chǎn)工業(yè)級方案。

硬件方案二:創(chuàng)龍科技 TL3568-EVM 評估板 (RK3568) + TLA7-EVM 評估板 (Artix-7)

實(shí)測數(shù)據(jù):寫速率 52.563MB/s,讀速率 67.387MB/s,誤碼率高。

備注:由于該測試受限于飛線連接方式,因此在 150MHz 通信時(shí)鐘頻率下測得誤碼率過高,測試結(jié)果僅供參考。

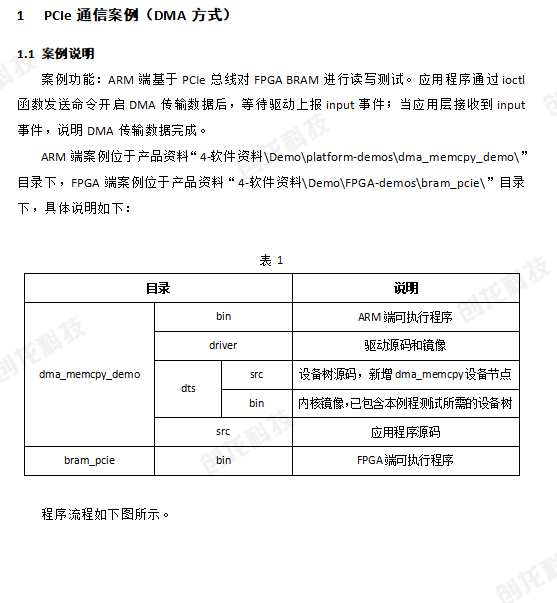

基于 FSPI 的 ARM + FPGA 通信案例詳解

下文主要介紹基于瑞芯微 RK3568J(硬件平臺:創(chuàng)龍科技 TL3568-EVM 評估板)與 Xilinx Artix-7(硬件平臺:創(chuàng)龍科技 TLA7-EVM 評估板)的 FSPI 通信案例,按照創(chuàng)龍科技提供的案例用戶手冊進(jìn)行操作得出測試結(jié)果。

同時(shí)基于Linux和Linux-RT系統(tǒng)進(jìn)行測試,得到 “小數(shù)據(jù) - 低時(shí)延”、“大數(shù)據(jù) - 高帶寬” 的測試數(shù)據(jù)。

spi_rw 案例

(1)案例說明

案例功能:ARM 端運(yùn)行Linux 系統(tǒng),基于 FSPI 總線對 FPGA BRAM 進(jìn)行讀寫測試。

ARM 端實(shí)現(xiàn) SPI Master 功能,原理說明如下:

a) 打開 SPI 設(shè)備節(jié)點(diǎn),如:/dev/spidev4.0。

b) 使用 ioctl 配置 FSPI 總線,如 FSPI 總線極性和相位、通信速率、數(shù)據(jù)長度等。

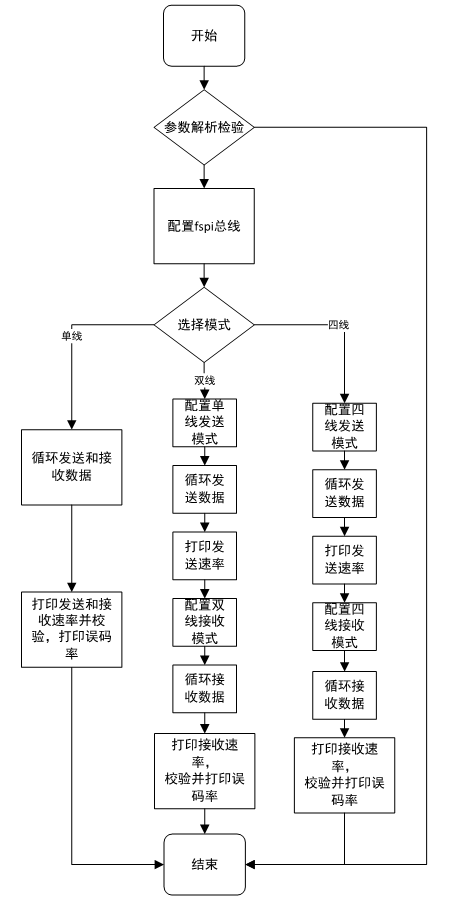

c) 選擇模式為單線模式、雙線模式或四線模式。當(dāng)設(shè)置 FSPI 總線為雙線模式時(shí),發(fā)送數(shù)據(jù)為單線模式,接收數(shù)據(jù)為雙線模式;當(dāng)設(shè)置 FSPI 為四線模式時(shí),發(fā)送數(shù)據(jù)為四線模式,接收數(shù)據(jù)為四線模式。

d) 發(fā)送數(shù)據(jù)至 FSPI 總線,以及從 FSPI 總線讀取數(shù)據(jù)。

e) 校驗(yàn)數(shù)據(jù),然后打印讀寫速率、誤碼率。

FPGA 端實(shí)現(xiàn) SPI Slave 功能,原理說明如下:

a) FPGA 將 SPI Master 發(fā)送的數(shù)據(jù)保存至 BRAM。

b) SPI Master 發(fā)起讀數(shù)據(jù)時(shí),F(xiàn)PGA 從 BRAM 讀取數(shù)據(jù)通過 FSPI 總線傳輸至 SPI Master。

圖 2ARM 端程序流程圖

(2)測試結(jié)果

ARM 通過 FSPI 總線(四線模式)寫入 4Byte 隨機(jī)數(shù)據(jù)至 FPGA BRAM,然后讀出數(shù)據(jù)、進(jìn)行數(shù)據(jù)校驗(yàn),同時(shí)打印 FSPI 總線讀寫速率和誤碼率。

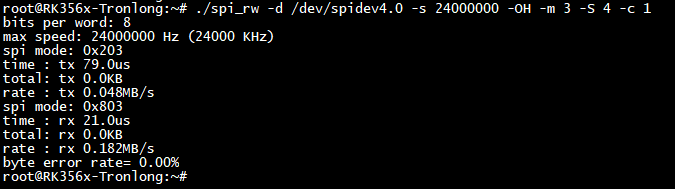

最終,本次測試設(shè)置 FSPI 總線通信時(shí)鐘頻率為 24MHz,則四線模式的理論通信速率為:(24000000 / 1024 / 1024 / 8 x 4)MB/s ≈ 11.44MB/s,從下圖可知,本次實(shí)測寫速率為 0.048MB/s,讀速率為 0.182MB/s,誤碼率為 0%。

圖 3

備注:以上案例硬件采用飛線方式進(jìn)行連接,需將 FSPI 總線通信時(shí)鐘頻率設(shè)置為較低的 24MHz,并且需設(shè)置較小的測試數(shù)據(jù)量(會導(dǎo)致實(shí)測速率偏低),否則會產(chǎn)生誤碼現(xiàn)象。如使用創(chuàng)龍科技 TL3568F-EVM 評估板 (RK3568J + Logos-2) 硬件平臺進(jìn)行測試,則無誤碼的通信速率將大幅提升。

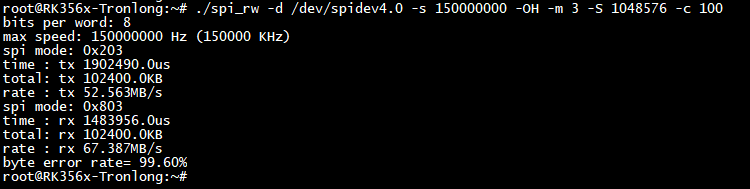

若設(shè)置 FSPI 總線通信時(shí)鐘頻率為 150MHz,ARM 通過 FSPI 總線寫入 1MByte 隨機(jī)數(shù)據(jù)至 FPGA BRAM,然后讀出數(shù)據(jù),循環(huán) 100 次,不做數(shù)據(jù)檢驗(yàn),最后打印 FSPI 總線讀寫速率和誤碼率。

最終,本次測試設(shè)置 FSPI 總線通信時(shí)鐘頻率為 150MHz,則 FSPI 四線模式理論通信速率為:(150000000 / 1024 / 1024 / 8 x 4) MB/s ≈ 71.53MB/s。從下圖可知,本次實(shí)測寫速率為 52.563MB/s,讀速率為 67.387MB/s,比較接近理論通信速率。

圖 4

備注:由于本次測試受限于飛線連接方式,因此在 150MHz 通信時(shí)鐘頻率下測得誤碼率過高,測試結(jié)果僅供參考。

rt_spi_rw 案例

(1)案例說明

案例功能:ARM 端運(yùn)行Linux-RT 系統(tǒng),基于 FSPI 總線對 FPGA BRAM 進(jìn)行讀寫測試。

ARM 端實(shí)現(xiàn) SPI Master 功能,原理說明如下:

a) 打開 SPI 設(shè)備節(jié)點(diǎn),如:/dev/spidev4.0。

b) 使用 ioctl 配置 FSPI 總線,如 FSPI 總線極性和相位、通信速率、數(shù)據(jù)長度等。

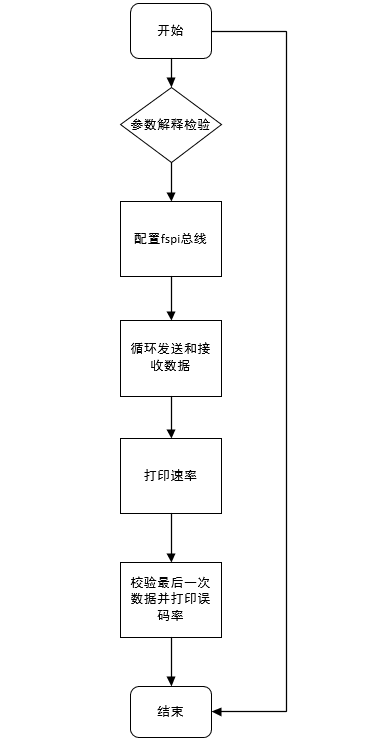

c) 選擇模式為單線模式、雙線模式或四線模式。當(dāng)設(shè)置 FSPI 總線為雙線模式時(shí),發(fā)送數(shù)據(jù)為單線模式,接收數(shù)據(jù)為雙線模式;當(dāng)設(shè)置 FSPI 為四線模式時(shí),發(fā)送數(shù)據(jù)為四線模式,接收數(shù)據(jù)為四線模式。

d) 發(fā)送數(shù)據(jù)至 FSPI 總線,以及從 FSPI 總線讀取數(shù)據(jù)。

e) 校驗(yàn)數(shù)據(jù),然后打印讀寫速率、誤碼率。

FPGA 端實(shí)現(xiàn) SPI Slave 功能,原理說明如下:

a) 將 SPI Master 發(fā)送的數(shù)據(jù)保存至 BRAM。

SPI Master 發(fā)起讀數(shù)據(jù)時(shí),F(xiàn)PGA 從 BRAM 讀取數(shù)據(jù)通過 FSPI 總線傳輸至 SPI Master。

圖 5ARM 端程序流程圖

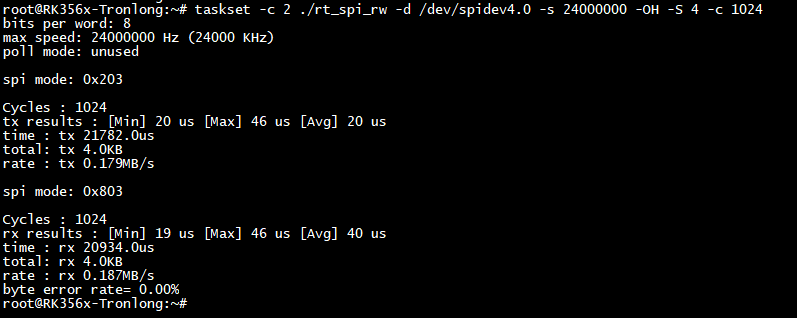

(2)測試結(jié)果

ARM 通過 FSPI 總線寫入 4Byte 隨機(jī)數(shù)據(jù)至 FPGA BRAM,然后讀出數(shù)據(jù)、進(jìn)行數(shù)據(jù)校驗(yàn),同時(shí)打印 FSPI 總線讀寫速率和誤碼率。最終,本次測試設(shè)置 FSPI 總線通信時(shí)鐘頻率為 24MHz,則 SPI 四線模式理論通信速率為:(24000000 / 1024 / 1024 / 8 x 4)MB/s ≈ 11.44MB/s。

從下圖可知,本次實(shí)測寫速率為 0.179MB/s,發(fā)送最大耗時(shí)為 46us,最小耗時(shí)為 20us,平均耗時(shí)為 20us,誤碼率為 0%;讀速率為 0.187MB/s,發(fā)送最大耗時(shí)為 46us,最小耗時(shí)為 19us,平均耗時(shí)為 40s,誤碼率為 0%。

圖 6

備注:以上案例硬件采用飛線方式進(jìn)行連接,需將 FSPI 總線通信時(shí)鐘頻率設(shè)置為較低的 24MHz,并且需設(shè)置較小的測試數(shù)據(jù)量(會導(dǎo)致實(shí)測速率偏低),否則會產(chǎn)生誤碼現(xiàn)象。如使用創(chuàng)龍科技 TL3568F-EVM 評估板 (RK3568J + Logos-2) 硬件平臺進(jìn)行測試,則無誤碼的通信速率將大幅提升。

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601808 -

ARM

+關(guān)注

關(guān)注

134文章

9045瀏覽量

366808 -

通信

+關(guān)注

關(guān)注

18文章

5969瀏覽量

135850 -

總線

+關(guān)注

關(guān)注

10文章

2866瀏覽量

87981 -

創(chuàng)龍科技

+關(guān)注

關(guān)注

2文章

131瀏覽量

7708 -

RK3568

+關(guān)注

關(guān)注

4文章

498瀏覽量

4931

發(fā)布評論請先 登錄

相關(guān)推薦

瑞芯微RK3568J如何“調(diào)節(jié)主頻”,實(shí)現(xiàn)功耗降低?一文教會您!

RK3568J“麒麟”+“翼輝”國產(chǎn)系統(tǒng)正式發(fā)布,“鴻蒙”也正在路上!

國產(chǎn)RK3568J基于FSPI的ARM+FPGA通信方案分享

3568F-評估板測試手冊(ARM端)

3568F-ARM+FPGA通信案例開發(fā)手冊

3568F--基于Pango Design Suite的FPGA程序加載與固化

3568F-FPGA案例開發(fā)手冊

請查收“國產(chǎn)化率認(rèn)證報(bào)告”(100%)——RK3568J工業(yè)核心板

RK3568J“麒麟”+“翼輝”國產(chǎn)系統(tǒng)正式發(fā)布,“鴻蒙”也正在路上!

創(chuàng)龍科技的RK3568J工業(yè)核心板技術(shù)參數(shù)解析

RK3568J“麒麟”+“翼輝”國產(chǎn)系統(tǒng)正式發(fā)布,“鴻蒙”也正在路上!

全國產(chǎn)RK3568J + FPGA的PCIe、FSPI通信實(shí)測數(shù)據(jù)分享!

深度對比!瑞芯微RK3562J比RK3568J好在哪里?

國產(chǎn)RK3568J基于FSPI的ARM+FPGA通信方案分享

國產(chǎn)RK3568J基于FSPI的ARM+FPGA通信方案分享

評論