導語:英特爾公司正式宣布,將推出一系列AI增強的汽車芯片,首家量產搭載車企將是來自中國的極氪。

異構集成、高速互聯、算力靈活可擴展正在成為新一輪汽車芯片競爭的焦點。尤其是隨著以ChatGPT為代表的大數據、大模型產品在車端的落地,對于芯片的要求還在持續提升。

本周,12家日本汽車制造商(包括豐田、日產、本田等)、零部件制造商和半導體公司組成了先進汽車芯片研發聯盟,重點是利用Chiplet(小芯片)技術開發下一代汽車SoC。

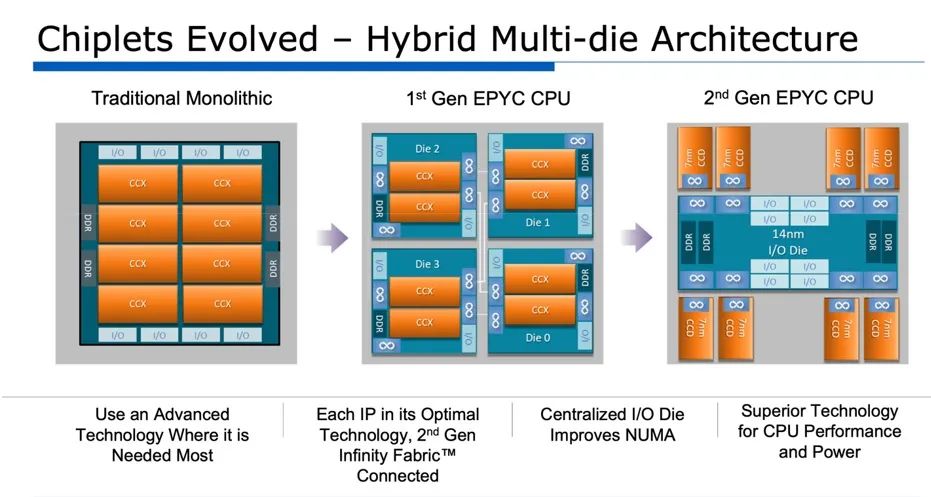

根據該聯盟的介紹,Chiplet技術的優勢包括效率高、適應多種功能、提高生產過程中的良率、能夠及時滿足汽車制造商的性能和功能要求。

而在上周結束的2024CES展上,英特爾公司正式宣布,將推出一系列AI增強的汽車芯片,首家量產搭載車企將是來自中國的極氪。

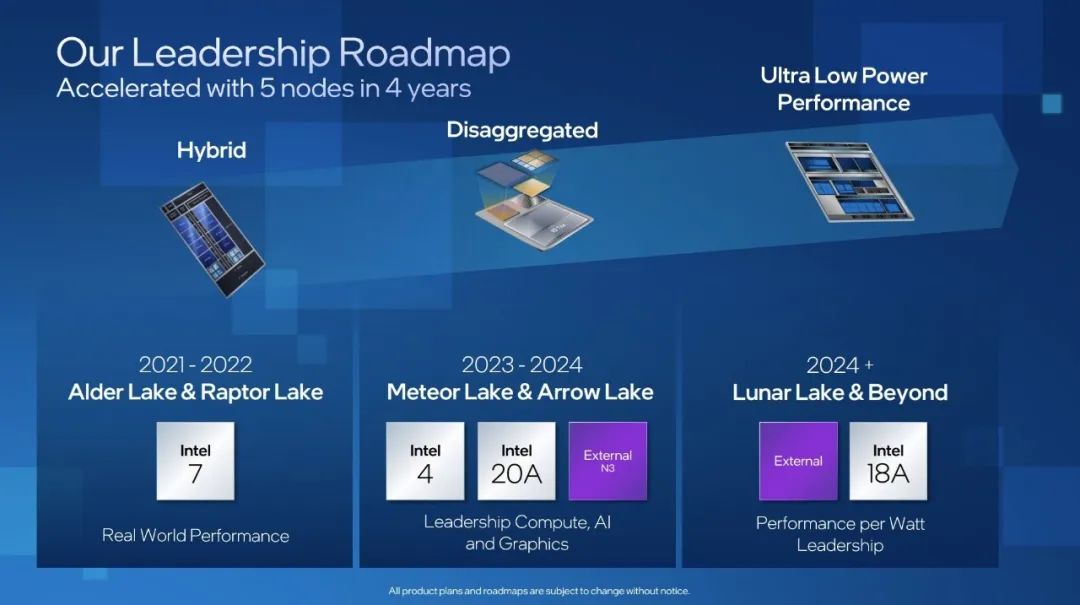

這款芯片的特點就是CPU+NPU+GPU的異構架構作為算力基座,并支持將第三方小芯片集成到SoC。為此,英特爾還宣布將于imec合作,以確保Chiplet封裝技術滿足車規級的嚴格質量和可靠性要求。

眾所周知,芯片不同的制程工藝在一定程度上決定了硬件性能的上限。比如,與10nm工藝相比,7nm工藝性能提升20%,能效提升40%,晶體管密度提升到1.6倍,實現性能與能效的雙重提升。

然而,隨著先進制程逐步迭代到5nm、3nm甚至是2nm,摩爾定律(單位平方英寸上晶體管的數量,每隔18~24個月就將翻一番)逐漸趨緩,先進制程的開發成本及難度提升。

半導體行業的共識是,先進制程的流片費用越來越高昂,流片成功率也變得越來越低;同時,芯片良品率也開始大幅下降。

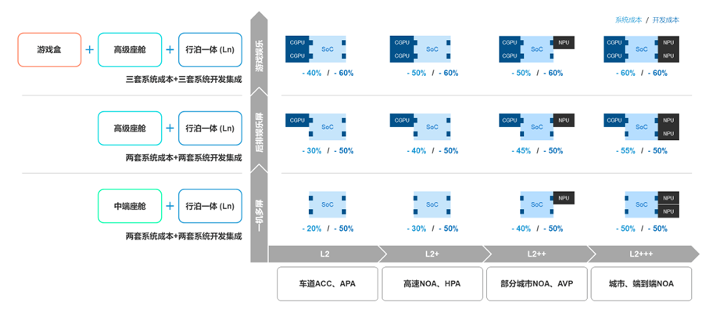

與此同時,頭部車企對于芯片的要求,正在出現差異化。由于各家車型的定位不同,導致目前市面上的通用芯片難以滿足個性化的需求。

此前,地平線宣布開放BPU IP授權,支持車企實現SoC自研,也是在這一趨勢下的產物。“地平線不可能做出一款芯片能夠適配任何場景,也不可能設計一堆的芯片去覆蓋所有場景。”

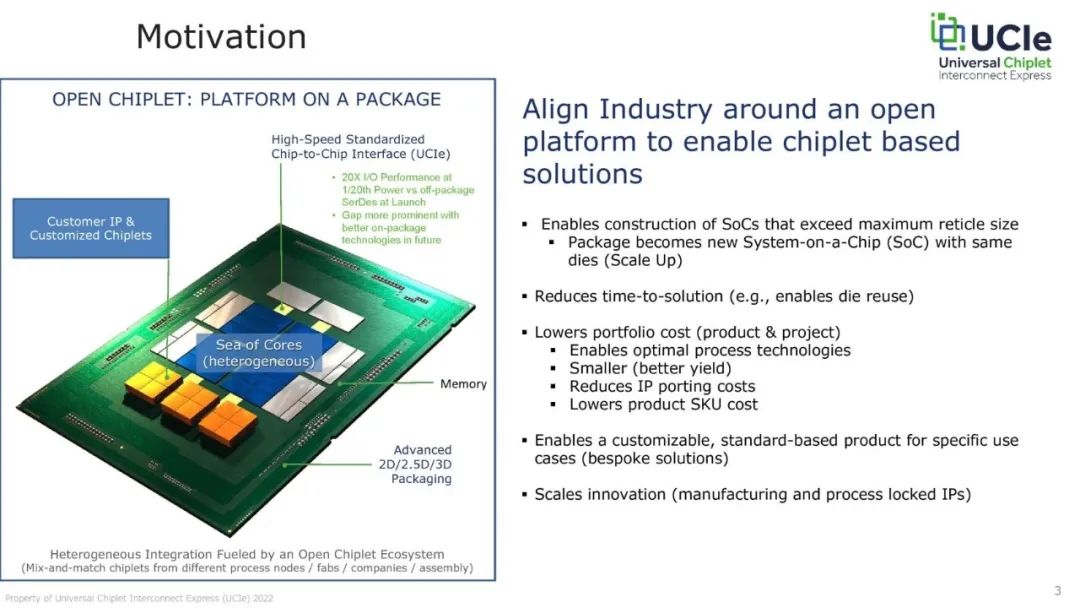

“基于Chiplet技術,客戶可以靈活配置第三方IP(基于不同工藝)。”尤其是汽車智能化的需求不斷釋放,未來異構集成(比如,X86、Arm和RISC-V同時并存)的模式,或許會成為市場主流。

而一組數據顯示,在Chiplet的系統級架構設計下,通過2.5D/3D堆疊等先進封裝技術,使用10nm工藝制造出來的芯片可以達到7nm芯片的集成度,同時研發投入和一次性生產投入則比7nm芯片的投入要少的多。

此外,模塊化的芯粒可以減少重復設計和驗證環節,降低芯片的設計復雜度和研發成本,加快產品的迭代速度。同時,降低對先進工藝制程的依賴,對于車載應用市場來說,本身也是一種降本策略。

有意思的是,戈登·摩爾(Gordon Moore)在1965年發表的白皮書《集成電路塞滿更多組件》中預言了這一天的到來,“隨著芯片密度和復雜性的提高,最終用較小的功能構建大型系統可能會更經濟,這些功能被單獨封裝并相互連接。”

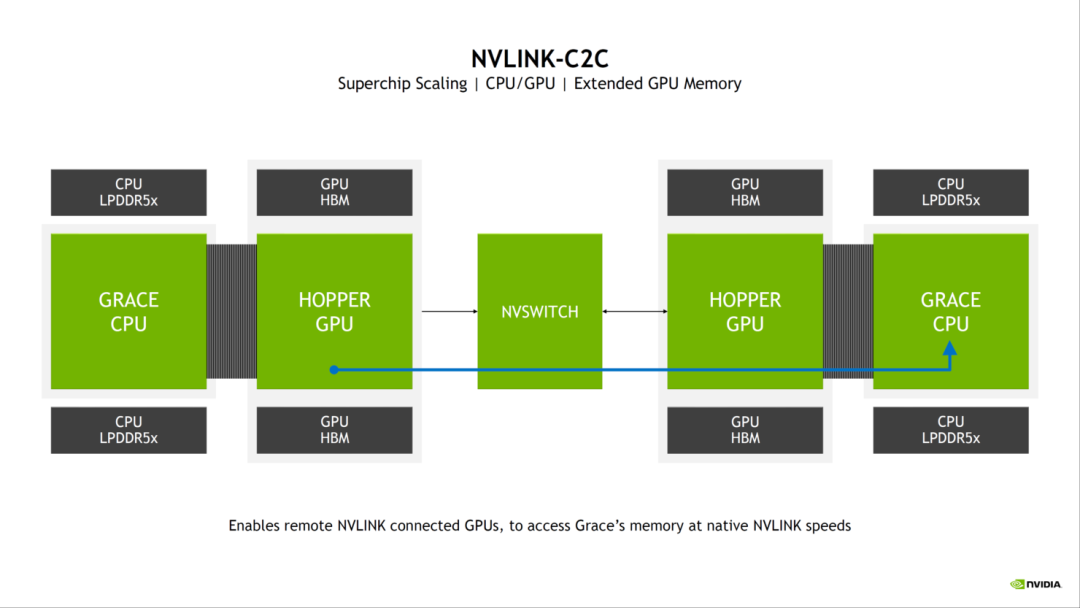

“為應對摩爾定律發展趨緩的局面,必須開發小芯片和異構計算。“站在英偉達的角度,這家已經在自動駕駛賽道占據先發優勢的芯片巨頭,同樣覬覦市場規模巨大的跨域市場。

目前,英偉達的NVIDIA NVLink-C2C,也是一種超高速的芯片到芯片、裸片到裸片的互連技術,支持定制裸片與NVIDIA GPU、CPU、DPU、NIC和SOC之間實現一致的互連。

此前,該公司推出的DRIVE Thor(單顆芯片算力達到2000TFLOPS),就可以通過多顆芯片的NVLink-C2C互連來支持多域計算,以分離自動駕駛等關鍵安全功能和信息娛樂等功能的處理。

此外,去年,英偉達與聯發科宣布,雙方將共同為新一代智能汽車提供解決方案,合作的首款芯片鎖定智能座艙,預計2025年問世,并在2026年至2027年投入量產。

在這款芯片設計上,聯發科將開發集成英偉達GPU芯粒的SoC,搭載NVIDIA AI和圖形計算IP,同樣基于chiplet實現主芯片與GPU芯粒間高速互連。

引用行業人士的話來說,就是,“基于Chiplet技術的芯片架構,能最大化滿足客戶的定制化SoC需求,并為系統架構師提供了更高的設計自由度,為系列產品提供多種平臺變體。”

而作為全球首家利用Chiplet技術研發車載算力芯片的企業,芯礪智能于2021年正式成立。針對車載芯片的特殊應用需求,芯礪智能開創了獨家車規級Chiplet Die-to-Die互連技術。

本周,該公司對外宣布,全自研Chiplet Die-to-Die互連IP(以下稱CL-Link)芯片一次性流片成功并順利點亮;此前,該技術已經獲得全球首個車規級ISO 26262 ASIL-D Ready認證。

CL-Link通過一種用于片間互連的總線流水線結構,做到了以較小位寬來實現片間高帶寬及低延遲的互連,每條信號速率高達16Gbps,其總線到總線的延時小于5ns,和片內總線延遲在同一量級。

同時,與目前市面上主流的Chiplet技術主要依靠先進封裝(對成本、可靠性、功能安全及供應鏈安全等挑戰較大)不同,基于傳統封裝的CL-Link技術可以實現更高良率及更低成本。

這意味著,中國企業首次在車規級賽道實現Chiplet技術的創新突圍,也在一定程度上可以幫助更多的中國芯片企業實現“合縱連橫”。更關鍵的是,這項技術可利用相對成熟的半導體制造和封裝技術,突破對先進工藝的依賴。

比如,Chiplet允許使用不同的制程制造異構SoC,例如,高性能模塊采用7nm,其他模塊只需要14nm或28nm就可以做到性能最大化,使系統整體的功能密度非常接近于7nm的集成。

在芯礪智能看來,在后摩爾時代,Chiplet技術是大算力平臺芯片目前最具前景和可實現性的突破性技術路徑,并且可以應對未來智能汽車E/E架構走向跨域融合、中央計算平臺的趨勢。

“單一域控制器內部的標準計算能力,將無法處理未來ADAS、通信和娛樂功能帶來的工作負載,尤其是不斷的OTA帶來的挑戰。”在imec公司看來,Chiplet帶來的最大效應就是降本增效。

比如,小芯片的開發成本,大概是大芯片的60%;尤其是軟件定義汽車概念的逐步落地,不同的算法對于SoC的不同IP核,有著不同的要求。這意味著,為特定任務部署高性能計算,有了更靈活的方式。

同時,隨著汽車行業的競爭日益白熱化,新車上市周期的大幅度縮短,這意味著,車企需要更加靈活的算力平臺,甚至是硬件可插拔的升級方案。

“Chiplet概念帶來的另一大革新,就是硬件升級可以做到類似搭樂高積木一樣的簡單。”在行業人士看來,這是對汽車芯片未來格局的洗牌和整合信號。

而就在兩年前,Intel、AMD、ARM、臺積電等行業巨頭一起發布了新的芯片級別互聯標準UCIe,希望解決chiplet行業標準問題。這些企業的大部分,掌控者汽車芯片產業鏈的核心環節。

這些傳統巨頭的目標是,創建一個開放的生態系統,使不同廠商在不同工藝技術上設計和制造的芯片與先進的封裝技術集成在一起可以實現有效協同。但背后的實質,是繼續壟斷市場。

而按照芯礪智能的說法,未來車規級高算力可擴展(200-2000Tops)SoC定制化設計將不再是成本難題。“后摩爾時代異構集成,對于行業來說,將是一種普惠方案。”

-

半導體

+關注

關注

334文章

27003瀏覽量

216265 -

cpu

+關注

關注

68文章

10824瀏覽量

211136 -

汽車芯片

+關注

關注

10文章

833瀏覽量

43352 -

chiplet

+關注

關注

6文章

416瀏覽量

12558

原文標題:Chiplet,汽車“芯”風向

文章出處:【微信號:alpworks,微信公眾號:阿爾法工場研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Imec牽頭啟動汽車芯粒計劃

imec主導汽車Chiplet計劃,多家巨頭企業加入

北極雄芯獲云暉資本投資,加速Chiplet研發與產品化

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術?

荷蘭AI芯片設計公司Axelera計劃推出新型汽車芯粒AI架構

芯礪智能Chiplet Die-to-Die互連IP芯片成功回片

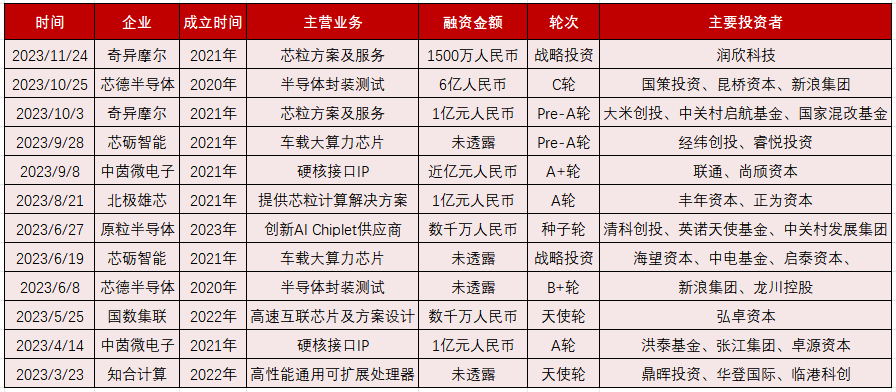

2023年Chiplet發展進入新階段,半導體封測、IP企業多次融資

Chiplet成大芯片設計主流方式,開啟IP復用新模式

什么是Chiplet技術?Chiplet技術有哪些優缺點?

芯原股份募資18億,投向AIGC及智慧出行Chiplet領域

劃片機,國內權威品牌博捷芯引領行業風向標

Chiplet,汽車“芯”風向

Chiplet,汽車“芯”風向

評論