鎖相環由哪三部分組成

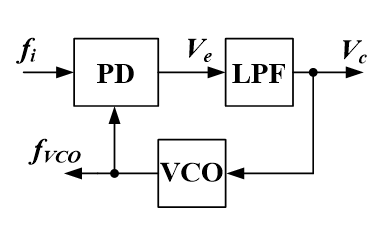

鎖相環(Phase Locked Loop,PLL)通常由以下三部分組成:

1. 相位比較器(Phase Comparator/Phase Detector): 相位比較器用于比較輸入信號與反饋信號的相位差,輸出一個表示相位差的控制電壓或數字值。

2. 電壓控制振蕩器(Voltage Controlled Oscillator,VCO): 電壓控制振蕩器接收來自相位比較器的控制信號,根據控制信號的電壓或數字值來調節自身的振蕩頻率。

3. 反饋電路(Feedback Circuit): 反饋電路將VCO輸出的信號反饋給相位比較器,用于與輸入信號進行相位比較,進而生成用于控制VCO的控制信號。

這三部分相互作用,構成了一個閉環控制系統,使得輸出信號的相位與輸入信號的相位相互鎖定或跟蹤。鎖相環廣泛應用于時鐘同步、頻率合成、數模轉換等領域。

鎖相環的工作原理

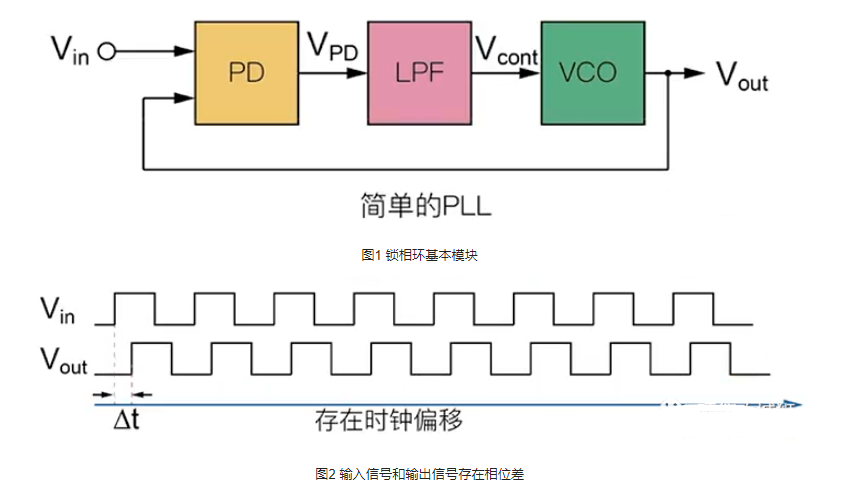

最基礎的鎖相環系統主要包含三個基本模塊:鑒相器(Phase Detector:PD)、環路濾波器(L00P Filter:LF)其實也就是低通濾波器,和壓控振蕩器(Voltage Controlled Oscillator:VCO)。有了這三個模塊的話,最基本的鎖相環就可以運行了。但我們實際使用過程中,鎖相環系統還會加一些分頻器、倍頻器、混頻器等模塊。(這一點可以類比STM32的最小系統和我們實際使用STM32的開發板)

從鎖相系統開始運行的那一刻進行分析,這個時候鑒相器有兩個輸入信號,一個是輸入的參考信號Vin,另一個是壓控振蕩器的固有振蕩信號Vout。

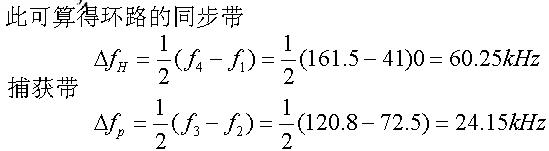

這個時候由于兩個信號的頻率不相同,會因為頻差而產生相位差,如果不對壓控振蕩器進行任何操作,那么相位差會不斷累積,從而跨越2Π角度,從零重新開始測相位,這便是測量死區,明明相位在不斷變大,但鑒相器只能測出0~2Π的范圍,測出的相位差最大便是2Π,這樣就導致了鑒相器的輸出電壓只能在一定的范圍內波動。

理想狀態是讓這兩個信號的相位差一直保持在2Π的范圍內,不進入測量死區。那么在系統剛開始的時候,鑒相器測出兩個信號的相位差,將相位差時間信號轉化為誤差電壓信號輸出(具體轉化過程見鑒相器講解)。

通過環路濾波器轉化為壓控電壓加到壓控振蕩器上,使壓控振蕩器的輸出頻率Vout逐步同步于輸入信號Vin,直到兩個信號的頻率逐漸同步,相位差也在測量誤差范圍內,那么整個系統就穩定下來了。

兩個信號的相位差不會累積變大,而是保持相對固定的相位差。(不是常規意義上的固定不變,而是在誤差允許范圍內的微小波動)。

鎖相環失鎖的原因有哪些

鎖相環(Phase Locked Loop,PLL)失鎖可能由以下幾個原因引起:

1. 輸入信號干擾:當輸入信號受到噪聲、失真、衰減等干擾時,可能導致相位比較器無法正確地比較輸入信號與VCO反饋信號之間的相位差,從而造成失鎖。

2. 頻率偏差過大:如果輸入信號的頻率與VCO輸出的振蕩頻率之間存在較大的偏差,超出PLL的跟蹤范圍,那么PLL可能會失鎖。

3. 環路帶寬設置不當:PLL的環路帶寬決定了其對輸入信號的跟蹤速度,如果環路帶寬設置得過窄或過寬,都可能導致PLL失鎖。

4. 相位比較器失效:相位比較器是PLL的關鍵組件之一,如果相位比較器出現故障或不正常工作,可能導致PLL失鎖。

5. 電源噪聲和供電問題:如果PLL的供電電源存在噪聲或不穩定,可能會對PLL的各個組件產生負面影響,導致失鎖。

6. 溫度變化和環境變化:溫度變化可能導致PLL內部的電子元件參數發生變化,進而影響PLL的性能和穩定性,導致失鎖。

7. 其他外部干擾:如電磁干擾、輻射干擾、振蕩器質量不良等外部因素也可能引起PLL失鎖。

審核編輯:黃飛

-

鎖相環

+關注

關注

35文章

583瀏覽量

87694 -

振蕩器

+關注

關注

28文章

3813瀏覽量

138883 -

低通濾波器

+關注

關注

14文章

472瀏覽量

47331 -

鑒相器

+關注

關注

1文章

60瀏覽量

23251 -

環路濾波器

+關注

關注

3文章

26瀏覽量

13149

發布評論請先 登錄

相關推薦

高頻鎖相環路LMX2430電子資料

鎖相環路是什么?有何特點

用鎖相環路實現任意頻率變換技術

基于FPGA的全數字鎖相環路的設計

鎖相環路跟蹤特性的測量方法

采用Spartan2系列FPGA器件實現全數字鎖相環路的設計和仿真驗證

鎖相環路的典型應用實例詳細說明

鎖相環路構成與工作機制

鎖相環路構成與工作機制

評論