鎖相環(huán)路鎖定狀態(tài)應(yīng)滿足什么條件

鎖相環(huán)(PLL)在鎖定狀態(tài)時應(yīng)滿足以下條件:

1. 相位同步:鎖定狀態(tài)下,輸出信號的相位應(yīng)與參考信號的相位保持固定的相對關(guān)系。這意味著輸出信號的相位與輸入信號的相位之間存在穩(wěn)定的相移。

2. 頻率同步:鎖定狀態(tài)下,輸出信號的頻率應(yīng)與參考信號的頻率相等或非常接近。這意味著輸出信號的頻率應(yīng)與參考信號的頻率保持穩(wěn)定的比例關(guān)系。

3. 穩(wěn)定性:鎖定狀態(tài)下,PLL應(yīng)能夠保持較高的頻率和相位穩(wěn)定性。即使在存在噪聲、干擾或其他外部變化的情況下,輸出信號的頻率和相位也應(yīng)保持相對穩(wěn)定。

4. 誤差最小化:鎖定狀態(tài)下,PLL應(yīng)盡量最小化輸出信號與參考信號之間的相位差或頻率偏差。通過精確調(diào)整PLL參數(shù)和輸入信號,可以盡可能地減小誤差。

通常需要合適的PLL設(shè)計和參數(shù)設(shè)置。例如,選擇合適的參考信號頻率、合理設(shè)置環(huán)路濾波器帶寬和參數(shù)、調(diào)整環(huán)路穩(wěn)定器的增益和阻尼系數(shù)等。

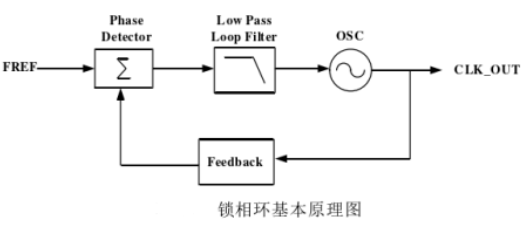

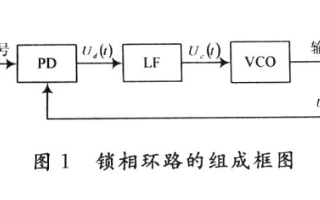

鎖相環(huán)是一個典型的負反饋系統(tǒng)。振蕩器Q負責(zé)產(chǎn)生振蕩時鐘信號,振蕩器的輸出時鐘信號被反饋環(huán)路采樣后與輸入?yún)⒖紩r鐘信號經(jīng)由相位檢測器進行比較,生成相位誤差信號,經(jīng)過濾波器濾波后,反饋給振蕩器對輸出時鐘信號的頻率進行調(diào)節(jié)。

低通濾波器主要是對相位誤差信號的高頻噪聲分量進行濾波,除去雜散信號。相位檢測器對輸出時鐘信號與輸入?yún)⒖紩r鐘信號的頻率和相位進行比較生成相位誤差信號。

鎖相環(huán)的類型有哪些

鎖相環(huán)(PLL)有多種類型,適用于不同的應(yīng)用場景。以下是一些常見的鎖相環(huán)類型:

1. 基本鎖相環(huán)(Basic PLL):基本鎖相環(huán)通常由鎖相檢測器(Phase Detector)、低通濾波器(Loop Filter)和令牌圈振蕩器(VCO)組成。它是最簡單的鎖相環(huán)形式,用于頻率和相位同步。

2. 延遲鎖相環(huán)(Delay-Locked Loop,DLL):延遲鎖相環(huán)主要用于對齊信號之間的時間延遲。它通過控制延遲線的長度來調(diào)整信號的相對延遲。常用于高速通信和數(shù)據(jù)存儲系統(tǒng)。

3. 頻率鎖定環(huán)(Frequency-Locked Loop,F(xiàn)LL):頻率鎖定環(huán)用于頻率同步,其相位追蹤能力較弱。它可以通過調(diào)整VCO的頻率來跟蹤輸入信號的頻率變化。

4. 相頻鎖定環(huán)(Phase-Frequency Locked Loop,PFL):相頻鎖定環(huán)是頻率鎖定環(huán)和相位鎖定環(huán)的組合形式,可以同時實現(xiàn)頻率和相位同步。它在通信系統(tǒng)和時鐘同步中廣泛應(yīng)用。

5. 多路復(fù)用鎖定環(huán)(Multiphase Locked Loop,MPLL):多路復(fù)用鎖定環(huán)是一種特殊的PLL,用于信號的多路復(fù)用和解復(fù)用。它將多個輸入信號分配到不同的相位狀態(tài),實現(xiàn)信號的并行處理。

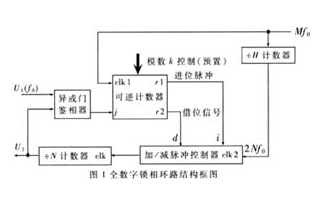

6. 數(shù)字鎖相環(huán)(Digital PLL,DPLL):數(shù)字鎖相環(huán)使用數(shù)字化的信號處理技術(shù),可以實現(xiàn)高精度的頻率和相位同步,并具有較強的抗干擾能力。它在通信、數(shù)字信號處理和時鐘恢復(fù)等領(lǐng)域得到廣泛應(yīng)用。

審核編輯:黃飛

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

583瀏覽量

87695 -

低通濾波器

+關(guān)注

關(guān)注

14文章

473瀏覽量

47331 -

pll

+關(guān)注

關(guān)注

6文章

774瀏覽量

135050 -

穩(wěn)定器

+關(guān)注

關(guān)注

0文章

54瀏覽量

13580

發(fā)布評論請先 登錄

相關(guān)推薦

高頻鎖相環(huán)路LMX2430電子資料

鎖相環(huán)路的基本特性是什么?應(yīng)用于哪些領(lǐng)域?

鎖相環(huán)路是什么?有何特點

鎖相環(huán)的工作原理

用鎖相環(huán)路實現(xiàn)任意頻率變換技術(shù)

基于FPGA的全數(shù)字鎖相環(huán)路的設(shè)計

集成鎖相環(huán)路原理特性及應(yīng)用

基于FPGA的全數(shù)字鎖相環(huán)路的設(shè)計

鎖相環(huán)路跟蹤特性的測量方法

采用Spartan2系列FPGA器件實現(xiàn)全數(shù)字鎖相環(huán)路的設(shè)計和仿真驗證

鎖相環(huán)路的組成、的基本特性和應(yīng)用分析

AD805:數(shù)據(jù)重定時鎖相環(huán)路過時數(shù)據(jù)表

鎖相環(huán)路的工作原理

鎖相環(huán)路鎖定狀態(tài)的條件及類型

鎖相環(huán)路鎖定狀態(tài)的條件及類型

評論