作者:Bill Schweber

投稿人:DigiKey 北美編輯

對于汽車試驗臺和硬件在環 (HIL) 子系統等測試和計量解決方案的設計人員來說,他們面臨著日益嚴峻的挑戰,必須在高性能、低延遲和寬帶寬之間找到最佳平衡。同時,他們需要靈活性和可重新配置性來支持快速變化的系統要求,并為廣泛的用例提供服務。

若要按照傳統方法來滿足這些要求,同時在采樣率增加時保持精確的交流和直流性能,就需要耗費大量的設計/調試時間和精力。而當改變元器件以適應試驗臺和儀器目標的變化時,就需要重新設計,更增加了這種精力耗費。

現在有了更好的替代方案,即一個基于可編程、可重新配置和可重復使用的設備的平臺。這些“錨”部件建立了一個性能基準,可以在單一類型的應用甚至是多個不同的應用中使用和重復使用。

本文以 [Analog Devices] 的 [AD3552R] 數模轉換器 (DAC) 為例,說明可編程元器件如何實現設計人員的目標,創建一個可擴展、易優化和可重新配置的信號鏈平臺。文中探討了評估板和 [LTspice]支持,以幫助設計人員入門。此外,還介紹了高度集成的 [ADAQ23878] 模數轉換器 (ADC)。在基于平臺的方法中,該轉換器可與 AD3552R 一起構成兩個關鍵且互補的錨部件。

集成和可編程性簡化了設計

隨著測試系統要求的變化,一些通常成功的傳統技術一直被用來最大限度地提高精度和減少誤差,盡管它們會增加設計和元器件成本,它們包括:

- 選擇“更好的”元器件,如公差更精密或溫度系數更低的電阻器,以盡量減少初始性能的不足,以及隨時間和溫度變化帶來的問題。

- 使用在很大程度上支持自消除不可避免誤差的拓撲結構,如匹配的電阻器和差分電路或經典惠斯通電橋。

- 通過使用“黃金”元器件提供初始和持續校準,例如可以與所有其他關鍵電壓進行比較的精密基準電壓源。

當應用需要頻繁更新 ADC 和 DAC 時,成功使用這些技術對測試系統設計人員來說變得更具挑戰性。

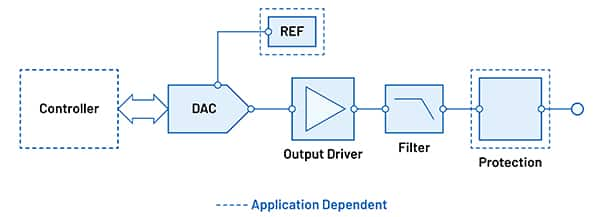

要避開眾多此類挑戰,基于平臺的可編程方法是個更好的選擇。它可以最大限度地減少甚至消除對初始項目“從頭開始”設計的需求,以及隨著要求變化而重新設計的需求。該方法還確保采用一致的方式對設計進行評估和仿真。這種可編程方法的一個關鍵元件是 DAC(圖 1)。

圖 1:DAC 是測試和儀器應用中的一個關鍵功能;隨著測試系統要求變得更具挑戰性,其能力受到密切關注。(圖片來源:Analog Devices)

圖 1:DAC 是測試和儀器應用中的一個關鍵功能;隨著測試系統要求變得更具挑戰性,其能力受到密切關注。(圖片來源:Analog Devices)

在測試和控制應用中,DAC 的性能和能力面臨的“壓力”越來越大,這些應用在較大范圍內既要求精度又要求高速度。此外,它們還要求具備靈活性,需要易于重新配置而省去全面或復雜的重新設計和重新認證周期。

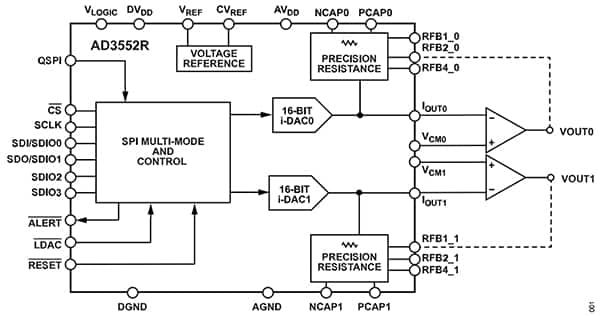

ADI 的 AD3552R 是一款 16 位、每秒 3300 萬次更新 (MUPS)、多跨度、雙輸出 SPI DAC(圖 2),因此能夠滿足性能目標。除了基本的性能屬性外,AD3552R 還有另一個優勢:很容易重新配置,以滿足新的或不斷變化的項目目標。這種可重新配置性可以高度保障這些目標的實現,不會帶來新的和不需要的“意外”。

圖 2:AD3552R 是一款 16 位、33 MUPS、多跨度、雙輸出的 SPI DAC,可以輕松地針對不同的性能屬性進行重新配置。(圖片來源:Analog Devices)

圖 2:AD3552R 是一款 16 位、33 MUPS、多跨度、雙輸出的 SPI DAC,可以輕松地針對不同的性能屬性進行重新配置。(圖片來源:Analog Devices)

AD3552R 采用 5 mm × 5 mm LFCSP 封裝,以固定的 2.5 V 參考電壓工作,但可通過軟件針對多個電壓跨度輸出范圍進行配置。它還可以實現性能、精度、速度和靈活性的最佳平衡。

該器件集成了三個漂移補償反饋電阻器,用于支持調節輸出電壓的外部跨阻放大器 (TIA)。偏移和增益調節寄存器允許生成多個輸出跨度范圍,例如 0 至 2.5 V、0 至 5 V、0 至 10 V、-5 至 +5 V 和 -10 至 +10 V,以及具有全 16 位分辨率的自定義中間范圍。

此外,為了解決眾所周知的“速度與精度”難題,AD3552R DAC 可以在快速模式下工作,以獲得最大的速度和最快的建立時間,或者在精密模式下工作,以獲得最高的精度和最大的準確性。在快速**模式下,DAC 數據以 16 位字的形式加載,使得單通道更新率為 33 MUPS。相比之下,在精密模式下,數據以 24 位寫入,使得單通道更新率為 22 MUPS。

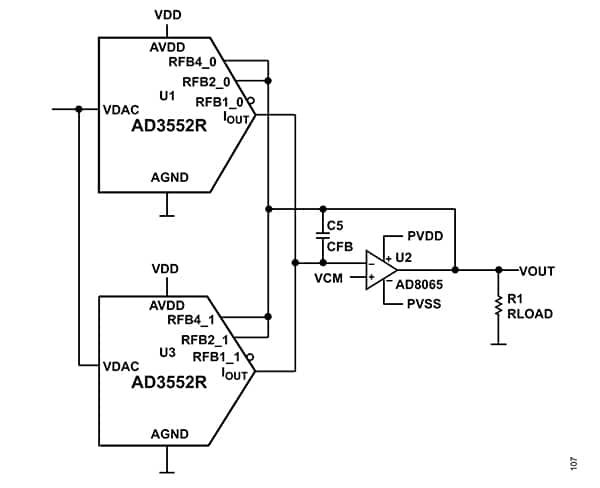

對于那些需要更低噪聲強度和更快建立時間并且可以接受更高功耗的應用,AD3552R 支持將兩個 DAC 通道合并,從而形成單一輸出(圖 3)。兩個 DAC 必須使用相同的代碼同時進行更新,以獲得使用單個 DAC 產生的相同電壓輸出;AD3552R 提供了幾種有效的方法來實現這一點。

圖 3:AD3552R 的兩個輸出可以合并在一起,以降低噪聲強度,同時加快建立時間。(圖片來源:Analog Devices)

圖 3:AD3552R 的兩個輸出可以合并在一起,以降低噪聲強度,同時加快建立時間。(圖片來源:Analog Devices)

該器件的 SPI 接口也很靈活,因為它可以配置為單 SPI(經典 SPI)、雙 SPI、同步雙 SPI 和四 SPI 模式,按單倍數據速率 (SDR) 或雙倍數據速率 (DDR) 工作,邏輯電平為 1.2 至 1.8 V。此外,由于數據完整性也是一個持續且日益受到關注的問題,因此可以使該器件內置循環冗余校驗 (CRC)。該器件還集成了多個錯誤校驗器來檢測 VREF 故障或存儲器映射損壞。

仿真模型加快配置速度,增強信心

盡管 AD3552R 是一個寬帶精密器件,但其眾多用戶可編程參數之間總會存在權衡問題。為了加速了解這些設計方案的影響并幫助設計人員入門,該器件采用評估板以及 LTspice 支持,用于評估噪聲、瞬態分析、交流仿真和其他參數。這簡化了延時/性能優化,因此設計人員不必在沒有可靠數據的情況下設置參數值或做出妥協。

在信號鏈中使用 LTspice 的能力讓所有元件配合在一起,因此用戶可以清楚地了解整個信號鏈的性能。這一點特別重要,因為 AD3552R 提供:

- 10 個電流范圍;由數字配置的增益調節值組合而成。

- 3 個跨阻增益值;因連接其中一個反饋電阻器產生。

- 總計 511 個數字配置的直流偏移值。

總共有 15,330 種組合,顯然超出了任何“動手”試驗板方法甚至選擇性人工評估的范圍。

AD3552R 的 LTspice 模型更新了注重模擬輸出的傳統 DAC 模型,提供了更加注重數字化的仿真。該模型中有些寄存器(特別是那些與數字增益調節和直流偏移有關的寄存器)的功能可以進行仿真,而且該模型還能夠高保真地再現動態和噪聲性能。LTspice 軟件所仿真的 AD3552R 性能特點包括:

- 輸出范圍仿真:直流掃描仿真可用于確認給定參數配置的輸出電壓范圍。其中還考慮了運算放大器的上裕量(范圍上限)和下裕量(范圍下限)所帶來的限制,進而可以輕松預測輸出信號的任何飽和度。

- 階躍響應調校:用階梯波形進行瞬態仿真有助于調整 TIA 反饋電容和輸出濾波器的值,以達到所需的上升時間、建立時間和過沖,并且還可以與參數掃描相結合來找到部件的最佳值。仿真還考慮了放大器和 DAC 的驅動能力,以估計信號的壓擺率和上升時間。(請注意,該值是個起點,因為仿真電路不包括評估板和器件封裝的寄生效應)。

- 交流帶寬仿真:交流掃描仿真可用于在輸出信號為諧波的應用中調整 TIA 反饋電容和輸出濾波器的值。

- 噪聲強度仿真:該特點可以預測 DAC 和 TIA 輸出端的噪聲強度,包括 1/f 區域和熱噪聲區域。AD3552R 的 LTspice 模型可以捕獲噪聲強度隨代碼的變化,并且考慮 TIA 的增益,而該增益會放大當前 DAC 輸出端的噪聲。

有關 LTspice 的更多信息,請參閱“[ 在靈敏儀器設計過程中如何使用 LTspice 確定光電感應噪聲性能 ]。”

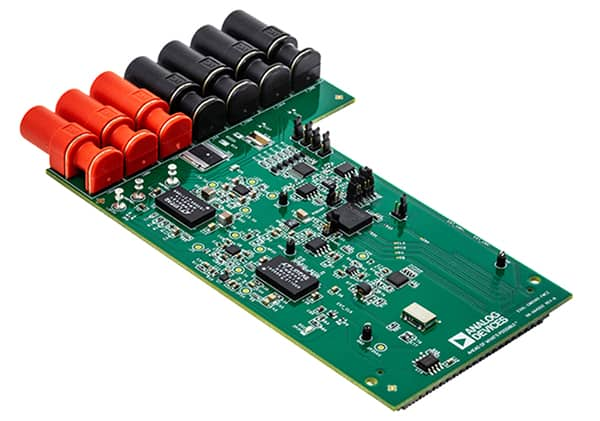

用真實的硬件進行實踐和測試

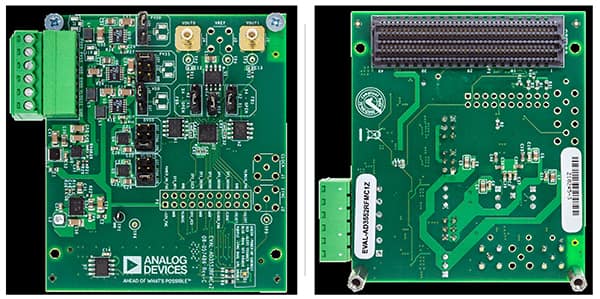

仿真非常有用且很有必要,但正如任何有經驗的工程師所知,它們不能完全取代實際評估,尤其是當器件外部的寄生效應等因素可能會影響性能時。對于 AD3552R,EVAL-AD3552RFMCxZ 可用于滿足這一需求,它有兩種型號:[EVAL-AD3552RFMC1Z] 適用于更高的速度,而 [EVAL-AD3552RFMC2Z]適用于更高的精度(圖 4)。

圖 4:EVAL-AD3552RFMCxZ(左:頂層;右:底層)有兩個類似的版本,其中一個針對速度進行了優化,另一個針對精度進行了優化。(圖片來源:Analog Devices)

圖 4:EVAL-AD3552RFMCxZ(左:頂層;右:底層)有兩個類似的版本,其中一個針對速度進行了優化,另一個針對精度進行了優化。(圖片來源:Analog Devices)

該評估板的軟件使用了 ADI 的“[分析、控制、評估]”(ACE) 軟件包。這個軟件包是一款桌面應用程序,可用于評估和控制 ADI 產品組合中的多個評估系統。該應用程序由一個通用框架和各個元器件特定的插件組成。

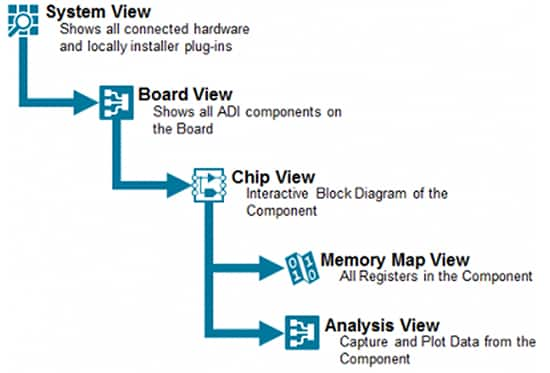

對于 AD3552R,ACE 有幾個視圖來控制 DAC 的不同方面。當首次打開某個視圖時,程序會在主窗口頂部創建一個新選項卡。AD3552R 插件可生成一個視圖層次結構:評估板視圖、芯片視圖、存儲器映射視圖和分析視圖,其中分析視圖結合了波形發生器視圖和矢量發生器視圖(圖 5)。

圖 5:AD3552R 的 ACE 插件可生成一個從高級系統視圖到基本分析視圖的視圖層次結構。(圖片來源:Analog Devices)

圖 5:AD3552R 的 ACE 插件可生成一個從高級系統視圖到基本分析視圖的視圖層次結構。(圖片來源:Analog Devices)

- 評估板視圖顯示一個評估板簡化示意圖,包括一些相關的連接器和芯片間的互連器件。

- 芯片視圖是一個簡化的芯片內部圖,顯示了接口邏輯、DAC 內核、精密反饋電阻器以及這些模塊的相關引腳。

- 存儲器映射視圖顯示 AD3552R 的整個配置空間;該空間可以顯示為寄存器列表或位字段列表。

- 波形發生器視圖允許為通道分配矢量,以及開始或停止波形生成。

- 矢量發生器視圖允許定義或加載波形,隨后這些波形可以分配給 DAC 通道。

借助評估板和 ACE 軟件,AD3552R 的用戶可以確認他們通過 LTspice 仿真器做出的決定,并根據需要進行調整。用戶還可以利用該器件的眾多寄存器和可編程功能及特性來操作該器件。

探索其他數據采集選項

對于可用來創建可擴展、易優化、可重新配置信號鏈平臺的高度可編程元器件,其選擇并不限于 AD3552R 等器件。

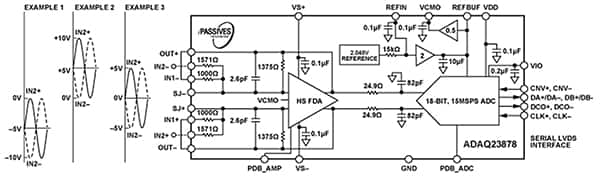

例如,Analog Devices 的 ADAQ23878 是一款 18 位、15-MSPS 的 μModule 引腳可綁定解決方案 ADC。這種高速數據采集解決方案通過使用現成的器件,消除了大量元件選擇、優化和布局的設計負擔,從而簡化并加快了精密測量系統的開發周期。

ADAQ23878 采用系統級封裝 (SIP) 技術,通過在單個器件中組合多個通用信號處理和調節模塊來減少終端系統元器件數量。該器件包括一個低噪聲全差分 ADC 驅動器放大器、一個穩定基準緩沖器以及一個高速 18 位 15 MSPS 逐次逼近寄存器 (SAR) ADC(圖 6)。

圖 6:ADAQ23878 將信號處理和調節模塊結合在單個器件中,最大限度地減少了對外部元器件的需求。(圖片來源:Analog Devices)

圖 6:ADAQ23878 將信號處理和調節模塊結合在單個器件中,最大限度地減少了對外部元器件的需求。(圖片來源:Analog Devices)

ADAQ23878 還集成了關鍵的無源元器件,這些元器件借助 ADI 的 iPassive 技術實現了卓越的匹配和漂移特性,最大限度地減少了與溫度有關的誤差源,從而實現了最佳性能。小基底面只有 9 mm × 9 mm,間距為 0.8 mm,并采用 100 焊球 CSP BGA 封裝,因此可以在不犧牲性能的情況下實現更小的儀器外形尺寸(圖 7)。

圖 7:ADAQ23878 的 SIP 技術將有源和無源元器件集成在單個易于應用的器件中,同時最大限度減少漂移相關的誤差源。(圖片來源:Analog Devices)

圖 7:ADAQ23878 的 SIP 技術將有源和無源元器件集成在單個易于應用的器件中,同時最大限度減少漂移相關的誤差源。(圖片來源:Analog Devices)

系統集成解決了許多設計挑戰,同時該器件仍然提供了可配置 ADC 驅動反饋環路的靈活性,以支持增益或衰減調整以及全差分或單端到差分輸入。

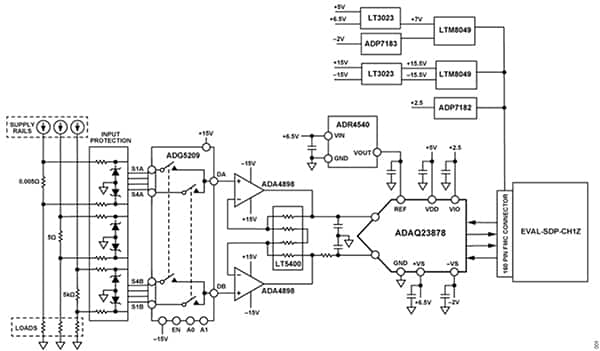

例如,它可以是一個完整的流式細胞儀的核心(請參閱“[ 使用高精度數據采集模塊快速實現流式細胞儀設計 ]”),或者是一個寬范圍的電流測量系統,其精度、帶寬和漂移性能與生產測試環境的臺式和機架式測試設備相當(圖 8)。同時,該解決方案足夠小,可以集成至需要持續監測的應用中。

圖 8:借助適當的特定應用有源和無源支持元器件,ADAQ23878 可用作數據采集系統的核心,在寬動態范圍內實現精確的電流測量。(圖片來源:Analog Devices)

圖 8:借助適當的特定應用有源和無源支持元器件,ADAQ23878 可用作數據采集系統的核心,在寬動態范圍內實現精確的電流測量。(圖片來源:Analog Devices)

該設計結合了分流電阻器、板載放大器和 ADAQ23878 μModule,可對三個電流范圍進行高精度測量。盡管尺寸有限,但該解決方案仍然增加了每塊板的通道數量,同時也緩解了散熱挑戰,減輕了因自熱造成的系統漂移校準負擔,并優化了綜合精度性能。板布局采用四端子分流電阻器,內置開爾文連接,減少了電阻溫度系數 (TCR) 的影響,從而與雙端子分流電阻器相比,提供了更好的溫度穩定性(圖 9)。

圖 9:基于 ADAQ23878 μModule 的完整電流測量系統要比必需的連接器小。(圖片來源:Analog Devices)

圖 9:基于 ADAQ23878 μModule 的完整電流測量系統要比必需的連接器小。(圖片來源:Analog Devices)

總結

測試與計量設備的設計人員需要精度、性能和靈活性,同時還需要能夠隨時重新配置基本設計以服務于廣泛的用例。如上所述,諸如 AD3552R DAC 等元器件具有許多可編程參數,從而能夠根據需要快速、方便地進行定制。AD35525 搭載 ADAQ23878 ADC,另有 LTspice 和評估板及軟件等工具的支持,可在基于平臺的測試系統設計方法中發揮關鍵作用,提供了所需的靈活性和性能,同時最大限度地縮短了重新配置的時間。

-

測試

+關注

關注

8文章

5160瀏覽量

126468 -

adc

+關注

關注

98文章

6431瀏覽量

544086 -

dac

+關注

關注

43文章

2269瀏覽量

190835 -

仿真

+關注

關注

50文章

4041瀏覽量

133413 -

SPI

+關注

關注

17文章

1700瀏覽量

91321

發布評論請先 登錄

相關推薦

如何有效地平衡測試與計量解決方案的延時、帶寬和性能

如何有效地平衡測試與計量解決方案的延時、帶寬和性能

評論