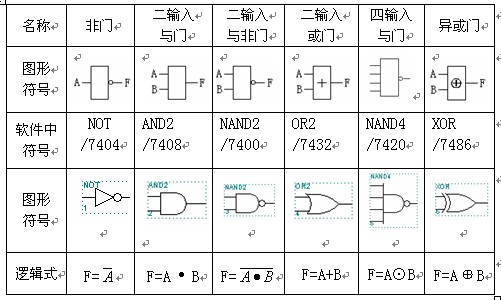

同或門

同或門(XNOR gate或equivalence gate)也稱為異或非門,是一種邏輯門電路。同或門的特點是當兩個輸入信號相同時,輸出為低電平;當兩個輸入信號不同時,輸出為高電平。在實際應用中,同或門常常用于實現兩個信號的相同性檢測,例如比較兩個數字是否相等。在數字邏輯電路中,同或門可以由異或門和與門組合而成。

同或門的符號為“⊕”,表示兩個輸入的異或運算。同或門在邏輯學里又稱為“雙條件”,或稱為“當且僅當”(if and only if)。所有輸入信號都相同時才輸出真,只要有一個以上不相同時就輸出假,也就是異或門的反面。

同或門在電路設計中常常用于實現兩個信號的相同性檢測,例如比較兩個數字是否相等。在實際應用中,同或門可以用于實現數據校驗和差錯檢測。在通信領域中,同或門可以用于實現數據校驗和差錯檢測;在計算機領域中,異或門可以用于實現數據的位操作和加密解密等算法。

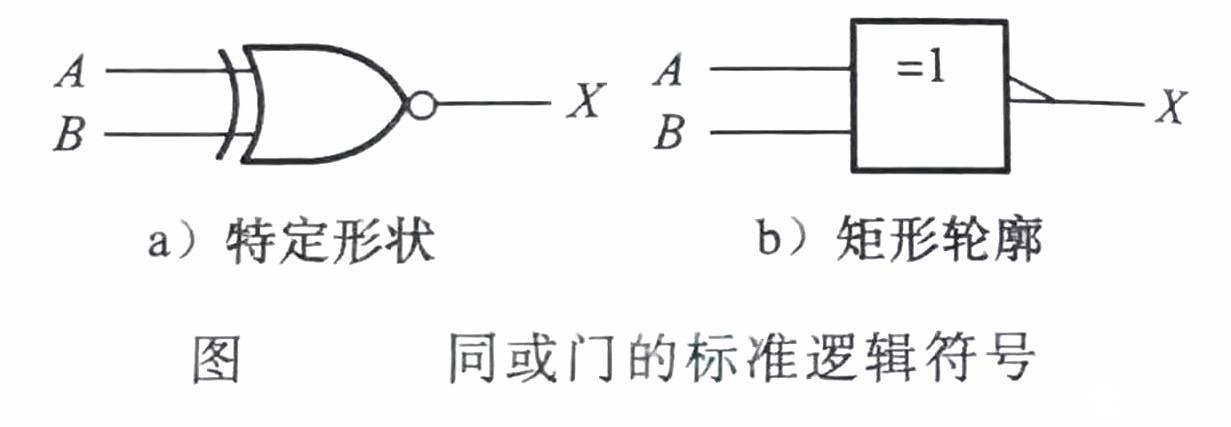

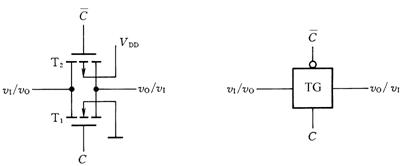

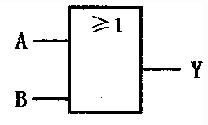

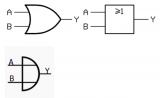

圖中給出了同或門(XNOR)的標準邏輯符號。

與異或門一樣,也只有兩個輸入端,同或門輸出端的小圓圈說明輸出結果跟異或門輸出相反,當輸入的兩個電平為相反電平時,同或門輸出低電平。A, B是輸入變量,x是輸出變量,同或運算可以描述如下:

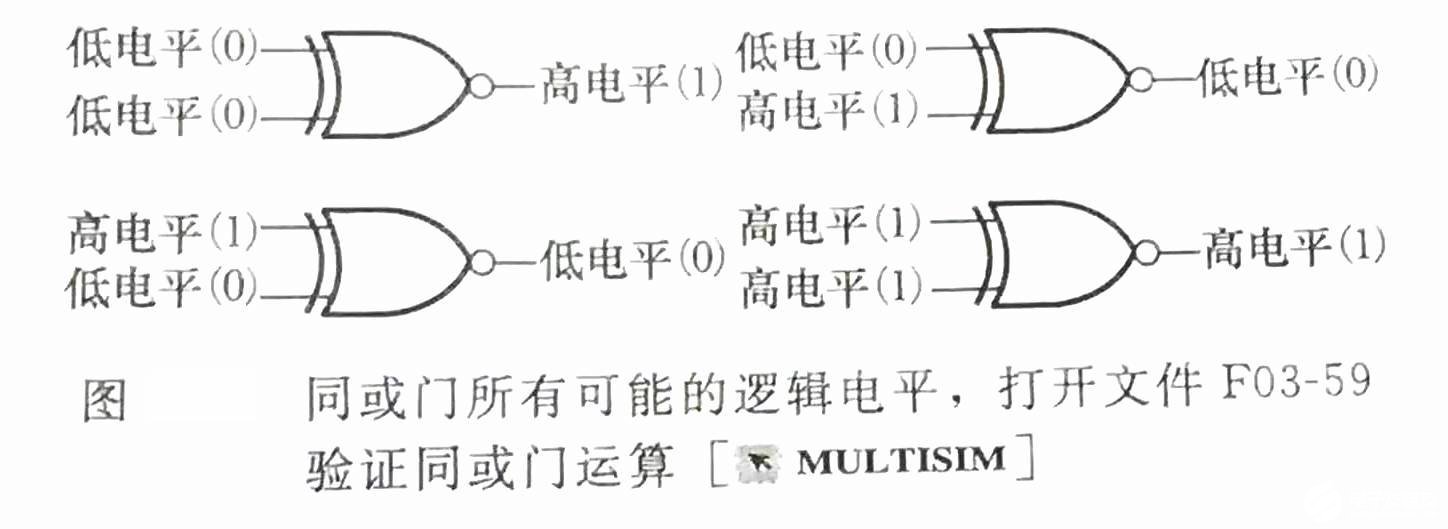

對于同或門而言,當輸入A為低電平,輸入B為高電平,或者輸入A為高電平,輸入B為低電平時,輸出為低電平;當輸入A和B同為低電平或者同為高電平時,輸出為高電平。

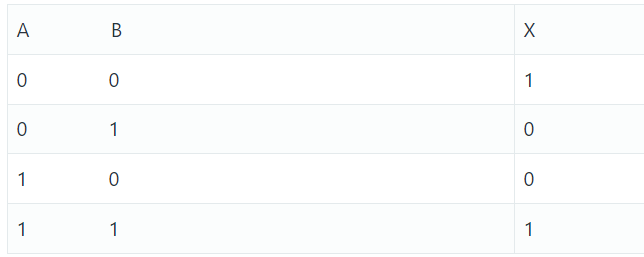

圖中給出了同或門四個可能輸入組合及其對應的輸出結果。表中總結了同或門的運算。注意同或門的輸入電平相同時,輸出才為高電平。

異或門的布爾表達式為:X=A+B

同或門的邏輯表達式為: X=(A+B)’

異或和同或的邏輯表達式也可以用與,或及反相運算表示:

對于異或門有:X=AB’+A’B

對于同或門有:X=(AB)’+AB

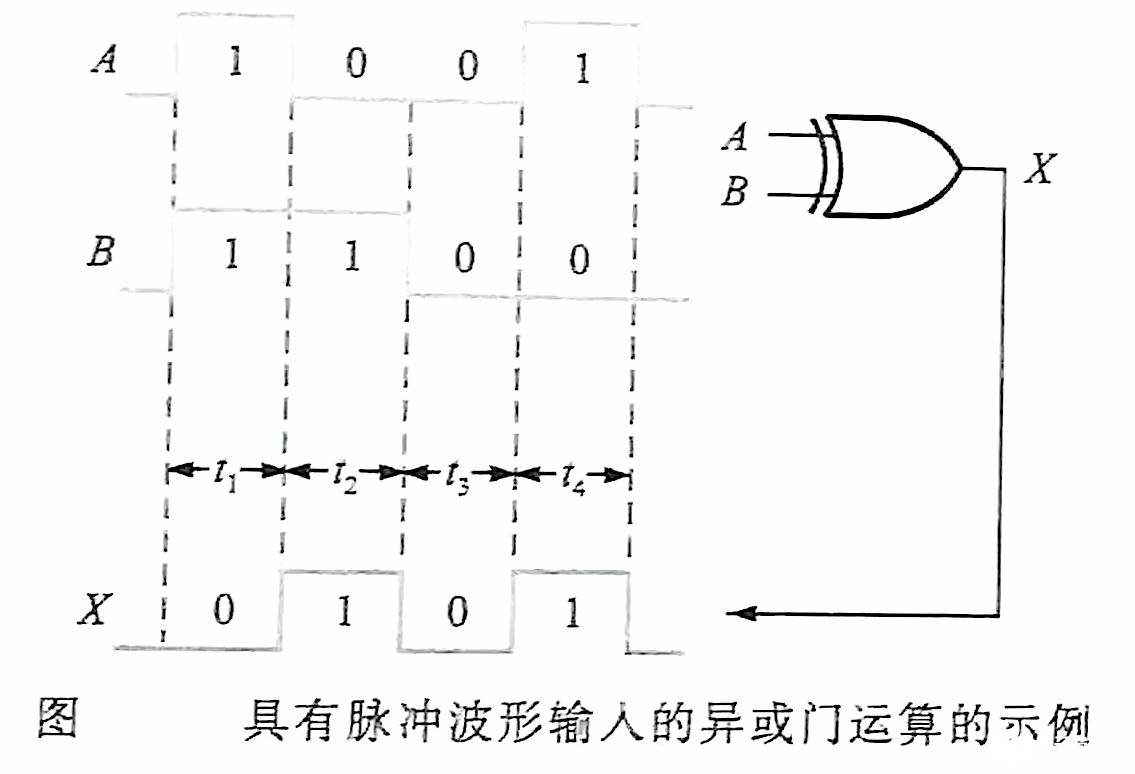

正如對其他門所做的一樣,觀察具有脈沖波形輸入的異或門和同或門運算,跟以前一樣,我們在脈沖波形輸入的每個不同的時間間隔上應用真值表,圖中給出了異或門的情況,可以看到在時間段t2和t4上,輸入A與B是不同的電平,因此,在這個時間間隔上,輸出為高電平。在t1和t3上,輸入A和B為相同的電平,故輸出為低電平。

異或門還可以做2位模2加法器。回憶之前所學的進制基本運算規則如下: 0+0=0,0+1=1,1+0=1和1+1=10。仔細觀察異或門的真值表,可以發現異或門的輸出是兩個輸入位的二進制和,如果輸入都為1,則輸出為0,舍棄進位1。后面將會學習異或門是如何組合起來形成復雜的加法電路。

審核編輯:黃飛

-

加法器

+關注

關注

6文章

183瀏覽量

30091 -

異或門

+關注

關注

1文章

32瀏覽量

17790 -

邏輯門電路

+關注

關注

2文章

67瀏覽量

11993 -

脈沖波形

+關注

關注

0文章

25瀏覽量

9814

發布評論請先 登錄

相關推薦

同或門標準邏輯符號

同或門標準邏輯符號

評論