ttl和cmos多余輸入端如何處理

TTL (Transistor-Transistor Logic) 和 CMOS (Complementary Metal-Oxide-Semiconductor) 是兩種常見的數(shù)字邏輯電路家族。當在TTL和CMOS邏輯門中存在多余的輸入端時,處理方法有所不同。

在TTL電路中,多余的輸入端通常稱為浮置(floating)輸入。TTL邏輯門中的浮置輸入應該被明確地連接到邏輯高電平(VCC)或邏輯低電平(GND)以確保準確的邏輯功能。這可以通過連接到適當?shù)?a target="_blank">電源電壓或通過使用上拉/下拉電阻網(wǎng)絡來實現(xiàn)。上拉電阻將浮置輸入連接到VCC,下拉電阻將浮置輸入連接到GND。

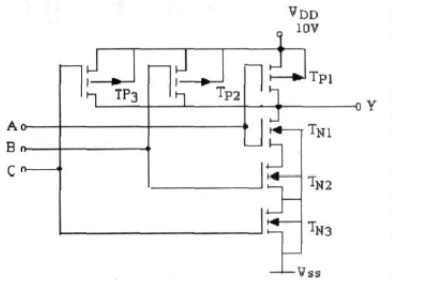

對于CMOS電路而言,多余的輸入端是不會影響電路的運行的,因為CMOS電路使用的是恒定電流源和MOSFET器件,不存在浮置輸入問題。在多余的輸入端上不需要連接電阻或者特定電平,它們可以被簡單地忽略。

怎么判斷ttl和cmos

要判斷一個電路是 TTL(Transistor-Transistor Logic)還是 CMOS(Complementary Metal-Oxide-Semiconductor),可以通過以下幾種途徑:

1. 型號和標識:查看器件上的標識或芯片的型號,一般會明確標明是 TTL 還是 CMOS。例如,器件型號中包含 “TTL” 或 “74” 的通常是 TTL,而型號中包含 “CMOS” 或 “40” 的通常是 CMOS。

2. 電源電壓:查看電路的工作電源電壓。TTL 通常工作在 5V 電源電壓下,而 CMOS 則可以工作在 3.3V、5V 或其他電壓范圍下。

3. 邏輯電平范圍:觀察電路的邏輯電平范圍。TTL 邏輯門的輸出電平通常接近于供電電壓(如 5V),邏輯低電平接近于 0V。而 CMOS 邏輯門的輸出電平可以接近于供電電壓(如 3.3V 或 5V),邏輯低電平接近于地電位。

4. 功耗:TTL 電路相對于 CMOS 電路來說具有較高的功耗。TTL 在每次切換時都會有一定的功耗,而 CMOS 技術(shù)在邏輯門沒有切換時基本上沒有功耗。

5. 噪聲容忍度:TTL 電路對輸入信號的噪聲相對敏感,而 CMOS 電路對噪聲有較高的容忍度。

除以上方法外,最準確的方式是查看器件的數(shù)據(jù)手冊或規(guī)格表,其中會詳細描述電路的類型、特性和工作參數(shù)。

現(xiàn)代的數(shù)字集成電路(IC)通常會明確標明是 TTL 還是 CMOS,以便區(qū)分。因此,通過觀察型號和型號標識、電源電壓、邏輯電平范圍、功耗和噪聲容忍度等特征,你應該能夠判斷出一個電路是 TTL 還是 CMOS。

ttl高低電平標準

在TTL(Transistor-Transistor Logic)電路中,高電平和低電平的標準通常是以電壓來定義的。以下是常見的TTL高低電平標準:

1. 高電平(logic high):一般情況下,TTL電路中的高電平狀態(tài)被定義為電壓在2.4伏特(V)到5伏特(V)之間。電壓在這個范圍內(nèi)時,電路被認為處于邏輯高狀態(tài)。

2. 低電平(logic low):TTL電路中的低電平狀態(tài)被定義為電壓在0伏特(V)到0.8伏特(V)之間。當電壓在這個范圍內(nèi)時,電路被認為處于邏輯低狀態(tài)。

需要注意的是,這些電壓標準是基于傳統(tǒng)的TTL電路。不同型號和實現(xiàn)方式的TTL電路可能會略有差異,因此在具體的應用中,還需要參考相關(guān)器件的數(shù)據(jù)手冊或規(guī)格表以獲得準確的高低電平標準。

現(xiàn)代的數(shù)字邏輯電路中也發(fā)展出了其他類型的邏輯家族,如低壓差動邏輯(LVDS)、高速CMOS(HCMOS)等,它們具有不同的高低電平標準。

審核編輯:黃飛

-

集成電路

+關(guān)注

關(guān)注

5382文章

11396瀏覽量

360955 -

CMOS

+關(guān)注

關(guān)注

58文章

5689瀏覽量

235171 -

TTL

+關(guān)注

關(guān)注

7文章

502瀏覽量

70147 -

電源電壓

+關(guān)注

關(guān)注

2文章

987瀏覽量

23947

發(fā)布評論請先 登錄

相關(guān)推薦

CMOS和TTL集成門電路多余輸入端的處理方法

CMOS電路多余輸入端懸空,會造成邏輯混亂,該如何處理?

關(guān)于TTL和CMOS門電路的邏輯輸入端輸入關(guān)系的區(qū)別/總結(jié)

TTL電路多余的輸入端的處理方式

ttl和cmos多余輸入端如何處理

ttl和cmos多余輸入端如何處理

評論