串?dāng)_,也稱為串音干擾,是指由于線路之間的電磁耦合導(dǎo)致的信號和噪聲的傳播。串?dāng)_可以引起信號質(zhì)量下降、數(shù)據(jù)錯誤和系統(tǒng)性能受限,因此在高速數(shù)字設(shè)計和高密度電路布局中需要特別關(guān)注和管理。

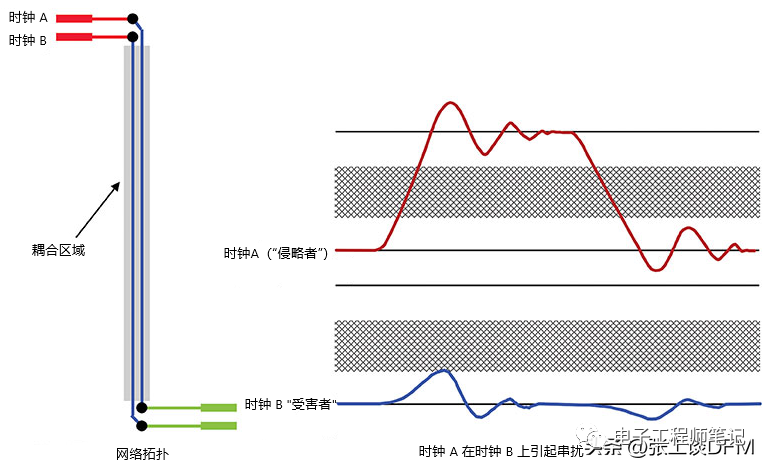

在通信系統(tǒng)中,特別是模擬通信時代,“串音”一詞直觀地描述了這種現(xiàn)象。當(dāng)兩根導(dǎo)線(包括印刷電路板上的薄膜布線)獨(dú)立存在時,它們之間理論上不應(yīng)有電氣信號或噪聲的相互影響。然而,當(dāng)兩根導(dǎo)線平行布置時,由于線間存在的雜散(寄生)電容和互感,就會產(chǎn)生干擾。因此,串?dāng)_也可以被理解為一種感應(yīng)噪聲。

線間的耦合主要包括兩種形式:由雜散(寄生)電容引起的電容性(靜電)耦合,以及由互感引起的電感性(電磁)耦合。這些耦合效應(yīng)會導(dǎo)致干擾,影響系統(tǒng)的正常運(yùn)行。

為了形象地說明這兩種耦合現(xiàn)象,可以使用簡化的等效電路圖來表示。電容性耦合的等效電路中,雜散電容并聯(lián)在干擾源和受影響的線路之間,而電感性耦合的等效電路中,互感器串聯(lián)在干擾源和受影響的線路之間。

在設(shè)計和布局電子系統(tǒng)時,工程師需要采取多種措施來減少串?dāng)_的影響,例如增加導(dǎo)線間的距離、使用屏蔽、采用差分信號技術(shù)、優(yōu)化布線和層序、降低信號頻率,以及使用絞合線等方法。通過這些方法,可以有效地管理和控制串?dāng)_,確保電子系統(tǒng)的穩(wěn)定性和可靠性。

串?dāng)_的產(chǎn)生機(jī)理:

串?dāng)_通常發(fā)生在并行運(yùn)行的信號路徑之間,如多根緊鄰的電線或印刷電路板(PCB)上的緊密布線。當(dāng)一個導(dǎo)體上的信號發(fā)生變化時,由于電磁場的相互作用,它會在相鄰的導(dǎo)體上誘導(dǎo)出電流或電壓波動。這些波動可能表現(xiàn)為噪聲,對鄰近線路的正常信號傳輸產(chǎn)生干擾。

串?dāng)_是現(xiàn)代電子和通信系統(tǒng)中不可避免的問題,它可能導(dǎo)致信號品質(zhì)下降和數(shù)據(jù)傳輸錯誤。通過合理的設(shè)計、布線技術(shù)和材料選擇,可以顯著地減少串?dāng)_的影響。有效的串?dāng)_管理對于確保高速數(shù)字系統(tǒng)的可靠性和性能至關(guān)重要。

-

電容

+關(guān)注

關(guān)注

99文章

5996瀏覽量

150005 -

等效電路

+關(guān)注

關(guān)注

6文章

292瀏覽量

32730 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

189瀏覽量

26932

發(fā)布評論請先 登錄

相關(guān)推薦

什么是串擾?如何減少串擾?

高速數(shù)字電路設(shè)計串擾問題產(chǎn)生的機(jī)理原因

請問ADC電路的串擾原因是什么?

PCB設(shè)計中串擾的產(chǎn)生以及如何避免

什么是碼間串擾_碼間串擾產(chǎn)生的原因是什么

串擾的類型,串擾產(chǎn)生的原因?

什么是串擾crosstalk?它是如何產(chǎn)生的?

PCB產(chǎn)生串擾的原因及解決方法

在PCB設(shè)計中,如何避免串擾?

嵌入式開發(fā)中引起串擾的原因是什么?

串?dāng)_產(chǎn)生的原因是什么

串?dāng)_產(chǎn)生的原因是什么

評論