D觸發(fā)器是一種常見的數(shù)字邏輯電路,它在數(shù)字系統(tǒng)和計算機中扮演著重要的角色。本文將詳細探討D觸發(fā)器的邏輯功能、工作原理以及RD(Reset-D)觸發(fā)器和SD(Set-D)觸發(fā)器的作用。

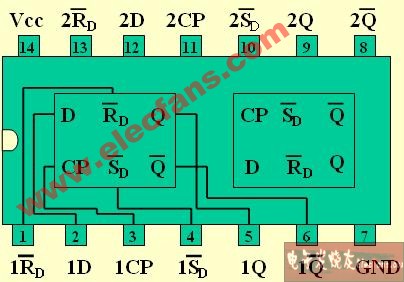

首先,我們先來了解一下D觸發(fā)器的邏輯功能。D觸發(fā)器是一種存儲設(shè)備,它可以存儲和傳輸一個二進制位數(shù)值。D觸發(fā)器有兩個輸入端和兩個輸出端。其中一個輸入端稱為數(shù)據(jù)輸入端D,另一個輸入端稱為時鐘輸入端CLK。D觸發(fā)器的兩個輸出端分別是Q和Q',其中Q是與數(shù)據(jù)輸入端D相同的數(shù)值,而Q'則是Q的反值。

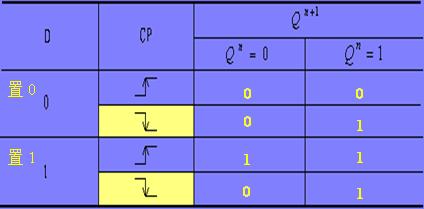

D觸發(fā)器的工作原理如下:當CLK輸入信號從低電平(0)變?yōu)楦唠娖剑?)時,如果D為高電平(1),則Q會跟隨D變?yōu)楦唠娖剑?);如果D為低電平(0),則Q會跟隨D變?yōu)榈碗娖剑?)。當CLK再次變?yōu)榈碗娖綍r,Q會保持之前的數(shù)值。換句話說,Q的數(shù)值會在每個正脈沖周期的上升沿發(fā)生變化,并在下一個上升沿之前保持不變。

D觸發(fā)器的邏輯功能可以通過邏輯電路圖表示。邏輯電路圖可用邏輯門符號表示。在D觸發(fā)器的電路圖中,輸入端D通過一個與門與時鐘輸入端CLK連接。輸出端Q通過一個非門與時鐘輸入端CLK和輸入端D'連接。非門的作用是得到Q的反值。

RD(Reset-D)觸發(fā)器是一種特殊類型的D觸發(fā)器。RD觸發(fā)器有一個Reset輸入端,當Reset輸入為高電平(1)時,Q的數(shù)值會被強制置為低電平(0),無論數(shù)據(jù)輸入端D的數(shù)值如何。當Reset輸入為低電平(0)時,RD觸發(fā)器會恢復(fù)到正常的D觸發(fā)器功能。

SD(Set-D)觸發(fā)器也是一種特殊類型的D觸發(fā)器。SD觸發(fā)器有一個Set輸入端,當Set輸入為高電平(1)時,Q的數(shù)值會被強制置為高電平(1),無論數(shù)據(jù)輸入端D的數(shù)值如何。當Set輸入為低電平(0)時,SD觸發(fā)器會恢復(fù)到正常的D觸發(fā)器功能。

RD和SD觸發(fā)器常常被用來對D觸發(fā)器進行重置和設(shè)置操作。例如,在一個計數(shù)器電路中,當計數(shù)器達到最大值時,RD觸發(fā)器可以通過Reset輸入將計數(shù)器的數(shù)值強制置為0,實現(xiàn)重置的功能。而SD觸發(fā)器可以通過Set輸入將計數(shù)器的初始值設(shè)置為一個非零值,從而實現(xiàn)對計數(shù)器的設(shè)置操作。

總結(jié)起來,D觸發(fā)器是一種常見的存儲設(shè)備,它可以存儲和傳輸一個二進制位數(shù)值。RD和SD觸發(fā)器是D觸發(fā)器的特殊類型,它們可以通過Reset和Set輸入實現(xiàn)對D觸發(fā)器的重置和設(shè)置操作。這些觸發(fā)器在數(shù)字系統(tǒng)和計算機中扮演著重要的角色,被廣泛應(yīng)用于各種數(shù)字電路和計算機硬件中。

-

存儲

+關(guān)注

關(guān)注

13文章

4117瀏覽量

85265 -

D觸發(fā)器

+關(guān)注

關(guān)注

2文章

164瀏覽量

47730 -

SD

+關(guān)注

關(guān)注

1文章

157瀏覽量

33557 -

數(shù)字系統(tǒng)

+關(guān)注

關(guān)注

0文章

137瀏覽量

20774

發(fā)布評論請先 登錄

相關(guān)推薦

D觸發(fā)器/J-K觸發(fā)器的功能測試及其應(yīng)用

JK觸發(fā)器 D觸發(fā)器 RS觸發(fā)器 T觸發(fā)器 真值表

D觸發(fā)器組成T和J-K觸發(fā)器電路圖

J-K觸發(fā)器組成D觸發(fā)器電路圖

d觸發(fā)器的邏輯功能 d觸發(fā)器sd和rd作用

d觸發(fā)器的邏輯功能 d觸發(fā)器sd和rd作用

評論