半減器

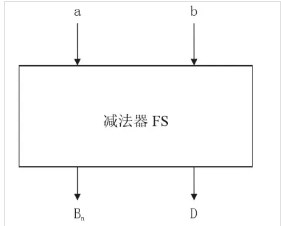

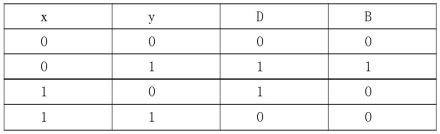

半減器(Half Subtractor,HS),二輸入、二輸出變量函數(shù)模塊。一個(gè)半減器模塊有兩個(gè)輸入 x、y 和兩個(gè)輸出 D、B,其中 x 稱(chēng)為被減數(shù),y稱(chēng)為減數(shù); D 稱(chēng)為差,B 稱(chēng)為借位輸出信號(hào)。半減器是只有兩個(gè)輸入變量、兩個(gè)輸出變量,無(wú)借位輸入的一位減法器, 半減器的真值表如圖3所示。

圖3 半減器真值表

由半減器的真值表可推導(dǎo)出半減器的邏輯表達(dá)式為:

D=x⊕y (“⊕”表示異或運(yùn)算)

B=-x·y (“-”表示非運(yùn)算,“·”表示與運(yùn)算)

半減器的門(mén)級(jí)邏輯電路

圖4 半減器的符號(hào)

由半減器模塊的邏輯表達(dá)式我們可以得到最常用的半減器模塊門(mén)級(jí)的邏輯電路圖和半減器模塊的符號(hào),如圖4所示。

全減器

一個(gè)全減器模塊有三個(gè)輸入 a i 、bi和 B i ,兩個(gè)輸出 D i 、B i+1 ,其中 ai稱(chēng)為被減數(shù),bi稱(chēng)為減數(shù),Di稱(chēng)為差,Bi稱(chēng)為第 i 位的借位輸入信號(hào),Bi+1稱(chēng)為第 i 位的借位輸出信號(hào)。

全減器是包含低位借位的三個(gè)輸入變量、兩個(gè)輸出變量的一位減法器,在半減器的基礎(chǔ)上再加一個(gè)低位借位輸入位,全減器的真值表如圖5所示。

圖5

由全減器的真值表推導(dǎo)出全減器的邏輯表達(dá)式為:

Di**=a i ⊕b i ⊕B**i

Bi+1**=(a i ⊕b i )·b i +(a i ⊕b i )·B**i

圖6 全減器的門(mén)級(jí)邏輯電路

圖7 全減器的符號(hào)

由全減器的邏輯表達(dá)式可以得到全減器模塊門(mén)級(jí)的邏輯電路圖和全減器模塊的符號(hào),分別如圖6、圖7所示 。

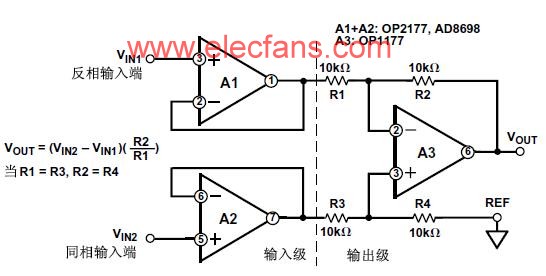

對(duì)于 n 位的二進(jìn)制數(shù),將兩個(gè) n 位的二進(jìn)制數(shù)相減得到一個(gè) n 位的二進(jìn)制的差以及一個(gè) 1 位的借位輸出信號(hào),這個(gè)借位輸出信號(hào)可以作為它下一位的借位輸入信號(hào),或者作為一個(gè)溢出標(biāo)志,圖8為一個(gè) n 位減法器電路的一般表示符號(hào)(其中 a、b 和 D 是 n 位的二進(jìn)制數(shù),Bn是 1 位的二進(jìn)制數(shù)) 。

圖8 n位減法器

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42581 -

門(mén)電路

+關(guān)注

關(guān)注

7文章

199瀏覽量

40127 -

全減器

+關(guān)注

關(guān)注

0文章

4瀏覽量

4857

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路中加法器和減法器邏輯圖分析

減法器電路與原理 減法器電路圖分享

如何設(shè)計(jì)一個(gè)16比特的減法器呢?

菜鳥(niǎo)請(qǐng)教一個(gè)運(yùn)放減法器的問(wèn)題

哪一個(gè)是減法器?負(fù)反饋在減法器電路中的原理?

設(shè)計(jì)一個(gè)基于RS觸發(fā)器余3碼十進(jìn)制減法器

如何用最簡(jiǎn)單的方法設(shè)計(jì)一個(gè)減法器?

本的二進(jìn)制加法/減法器,本的二進(jìn)制加法/減法器原理

減法器電路

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

減法器電路設(shè)計(jì)方案匯總(五款模擬電路設(shè)計(jì)原理圖詳解)

FPGA常用運(yùn)算模塊-加減法器和乘法器

求一種減法器的設(shè)計(jì)方案

求一種減法器的設(shè)計(jì)方案

評(píng)論