總體方案設(shè)計(jì)

本設(shè)計(jì)使用EWB進(jìn)行仿真,使用74LS48、七段譯碼器、LED、開關(guān)、異或門、或門、非門、與非門等。電路按功能分為三個(gè)部分:減數(shù)部分:減數(shù)變成補(bǔ)碼(原碼取反加1);被減數(shù)部分:被減數(shù)與減數(shù)的補(bǔ)碼相加;差部分:被減數(shù)減減數(shù)的結(jié)果顯示。四位二進(jìn)制減法器的總體仿真圖如圖所示。

圖9 四位二進(jìn)制減法器的總體仿真圖

被減數(shù)模塊的設(shè)計(jì)

本模塊由開關(guān)、74LS48、VCC(+12 V)、GND、七段譯碼器構(gòu)成,用開關(guān)控制輸入信號( 被減數(shù)),5、6、7、8 從高位到低位,用74LS48和七段譯碼器構(gòu)成顯示電路。四位二進(jìn)制減法器的被減數(shù)模塊的仿真圖如圖10所示。

圖10 四位二進(jìn)制減法器的被減數(shù)模塊的仿真圖

減數(shù)模塊的設(shè)計(jì)

本模塊由開關(guān)、74LS48、VCC(+12 V)、GND、七段譯碼器、異或門、或門、非門、與非門構(gòu)成。用開關(guān)控制輸入信號(減數(shù)),1、2、3、4 從高位到低位,將輸入信號的原碼變成補(bǔ)碼供計(jì)算使用,用74LS48 和七段譯碼器構(gòu)成顯示電路。四位二進(jìn)制減法器的減數(shù)模塊的仿真圖如圖11所示。

圖11 四位二進(jìn)制減法器的減數(shù)模塊的仿真圖

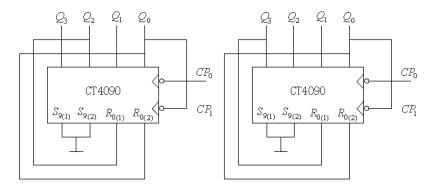

差模塊的設(shè)計(jì)

本模塊由VCC(+12 V)、GND、七段譯碼器、74LS48、LED 構(gòu)成。從右到左依次是從高位到低位,并用74LS48和七段譯碼器構(gòu)成顯示電路。四位二進(jìn)制減法器的差模塊的仿真圖如圖12所示。

圖12 四位二進(jìn)制減法器的差模塊的仿真圖

-

二進(jìn)制

+關(guān)注

關(guān)注

2文章

761瀏覽量

41476 -

顯示電路

+關(guān)注

關(guān)注

6文章

95瀏覽量

33116 -

減法器

+關(guān)注

關(guān)注

1文章

26瀏覽量

16761 -

GND

+關(guān)注

關(guān)注

2文章

525瀏覽量

38446 -

74ls48

+關(guān)注

關(guān)注

1文章

13瀏覽量

11740

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)字電路中加法器和減法器邏輯圖分析

減法器電路與原理 減法器電路圖分享

4位二進(jìn)制乘法器電路

如何理解二進(jìn)制運(yùn)算規(guī)則 二進(jìn)制是如何運(yùn)算的

集成四位二進(jìn)制計(jì)數(shù)器

## 線上實(shí)驗(yàn)五:2個(gè)2位二進(jìn)制乘法器 精選資料分享

如何去實(shí)現(xiàn)一個(gè)2位二進(jìn)制乘法器的設(shè)計(jì)呢

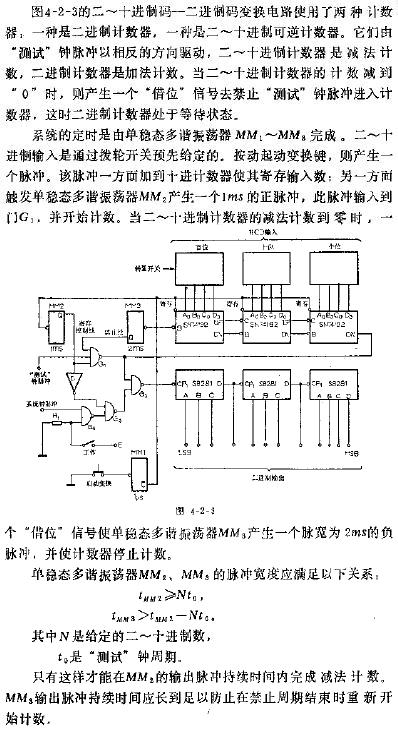

采用減法計(jì)數(shù)簡化二~十進(jìn)制一二進(jìn)制碼變換

二進(jìn)制編碼和二進(jìn)制數(shù)據(jù)

本的二進(jìn)制加法/減法器,本的二進(jìn)制加法/減法器原理

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

DM74LS83A四位快速進(jìn)位二進(jìn)制加法器的數(shù)據(jù)手冊免費(fèi)下載

4位二進(jìn)制并行加法器的程序和工程文件免費(fèi)下載

四位二進(jìn)制減法器的設(shè)計(jì)與實(shí)現(xiàn)

四位二進(jìn)制減法器的設(shè)計(jì)與實(shí)現(xiàn)

評論