據韓國媒體ETNews透露,三星電子正在研究將非導電膠(NCF)更換為模塑底部填膠(MUF),以提升公司的封裝技術水平。

此前,三星一直利用非導電膠來完成半導體間的垂直連接。盡管NCF能有效避免芯片變形,但其難度較大且生產率低下的缺點使其未受到廣泛認同。

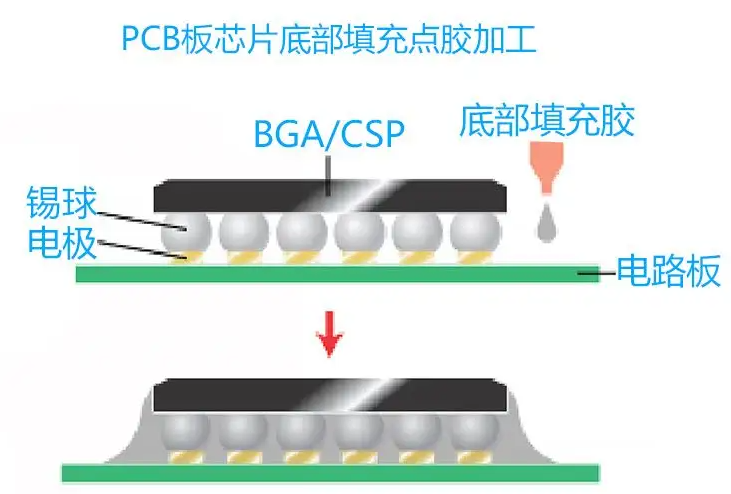

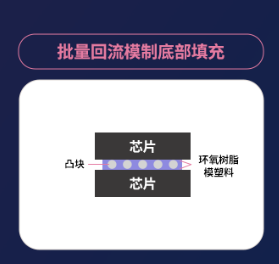

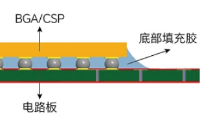

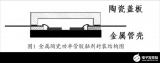

據報道,三星電子擬在硅通孔(through-silicon electrode,TVS)的制造過程中引用MUF材料。TVS可以在晶圓或裸晶表面鉆出許多微小的孔洞,提供垂直連接通道。而MUF則可以填充這些孔洞,減小半導體間的空隙,從而讓各種垂直堆疊的半導體更加穩定。

據悉,三星已從日本引進相關設備,以推進MUF的應用。此外,SK海力士也在第三代HBM(HBM2E)之后改用MUF,尤其是針對MR-MUF進行了調整。

業內人士評價說:“相較于NCF,MR-MUF具有更高的導熱性能,對工藝速度及良品率均有顯著改善。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

三星電子

+關注

關注

34文章

15856瀏覽量

180934 -

TVS

+關注

關注

8文章

775瀏覽量

60519 -

晶圓

+關注

關注

52文章

4851瀏覽量

127817

發布評論請先 登錄

相關推薦

三星電子計劃新建封裝工廠,擴產HBM內存

三星電子計劃在韓國天安市新建一座半導體封裝工廠,以擴大HBM內存等產品的后端產能。該工廠將依托現有封裝設施,進一步提升

三星電子:18FDS將成為物聯網和MCU領域的重要工藝

電子發燒友網報道(文/吳子鵬)今年上半年,三星在FD-SOI工藝上面再進一步。3月份,意法半導體(STMicroelectronics)宣布與三星聯合推出18nm FD-SOI

發表于 10-23 11:53

?235次閱讀

芯片封裝膠underfill底部填充膠點膠工藝基本操作流程

的脫落。在烘烤工藝中,參數制定的依據PCBA重量的變化,具體可以咨詢漢思新材料。二、預熱對主板進行預熱,可以提高Underfill底部填充膠的流動性。要注意的是——

詳解點膠工藝用途和具體要求?

電子產品芯片的微型化正變得越來越受歡迎。但是微型化帶來了焊點可靠性問題。元件和基板使用錫膏進行焊接,但是由于體積太小使得焊點更容易受到應力影響而出現脫落問題。因此引入了底部填充工藝。該

消息稱三星顯示擬引入每周64小時工作制

在全球科技產業競爭日益激烈的背景下,韓國科技巨頭三星顯示(SDC)正試圖通過一系列創新措施來鞏固其市場地位。最近,有消息稱三星顯示擬引入每周64小時工作制,并已率先在其芯片和手機團隊中

mos封裝工藝是什么,MOS管封裝類型

MOS封裝工藝是指將制造好的MOS管芯片通過一系列步驟封裝到外殼中的過程。以下是MOS封裝工藝的詳細步驟和相關信息:

受困于良率?三星否認HBM芯片生產采用MR-MUF工藝

芯片生產中應用MR-MUF(批量回流模制底部填充)技術的傳言并不屬實。 ? 三星在HBM生產中目前主要采用非導電薄膜(NCF)技術,而非SK海力士使用的批量回流模制底部填充(MR-MUF)封裝

三星效仿SK海力士,采用競爭對手主導的芯片封裝工藝

就此,知情人士指出,三星此舉體現出該公司提升HBM良率的決心。對此,一家行業分析機構表示,考慮到AI行業對HBM3及HBM3E芯片需求日益增長,三星有必要作出調整。

半導體封裝工藝面臨的挑戰

半導體工藝主要是應用微細加工技術、膜技術,把芯片及其他要素在各個區域中充分連接,如:基板、框架等區域中,有利于引出接線端子,通過可塑性絕緣介質后灌封固定,使其形成一個整體,以立體結構方式呈現,最終形成半導體封裝工藝。

發表于 03-01 10:30

?755次閱讀

半導體封裝工藝的研究分析

控,能采用精細化管理模式,在細節上規避常規問題發生;再從新時代發展背景下提出半導體封裝工藝面臨的挑戰,建議把工作重心放在半導體封裝工藝質量控制方面,要對其要點內容全面掌握,才可有效提升半導體封

三星第二代3nm工藝開始試產!

據報道,三星預計在未來6個月時間內,讓SF3的工藝良率提高到60%以上。三星SF3工藝會率先應用到可穿戴設備處理器上,三星Galaxy Wa

什么是COB封裝工藝?COB封裝工藝的優勢 COB封裝工藝流程有哪些?

LED顯示屏行業發展至今,已經出現過多種生產封裝工藝,小間距市場目前以SMT貼片技術為主,在微間距市場,COB封裝技術憑借更高像素密度,更精密的顯示效果,越來越獲得市場認可。

三星電子擬升級工藝,引入模塑底部填膠提升封裝工藝

三星電子擬升級工藝,引入模塑底部填膠提升封裝工藝

評論