| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 原理圖必須采用公司統(tǒng)一原理圖庫。 | |

| 2 | 規(guī)定 | 原理圖應采用0.100柵格 | |

| 3 | 規(guī)定 | 原理圖正文字體設置參照原理圖設計規(guī)范,采用默認設置。說明文字為82mil,管腳號為66mil。 | |

| 4 | 規(guī)定 | 原理圖封面字體應調(diào)整到與欄目字體基本等大(建議使用180mil字體)。 | |

| 5 | 規(guī)定 | 原理圖首頁放置ZTE_Cover_A4做為封面,不加圖框。 | 模塊電路不加封面 |

| 6 | 規(guī)定 | 原理圖除首頁之外,一律采用ZTE_frameA4或者ZTE_frameA4plus圖框。只有在元器件符號很大,無法在圖框中擺放的情況下方可以選用ZTE_frameA3圖框。 | |

| 7 | 規(guī)定 | 原理圖首頁封面Checked,Normalized和Approved三項不填寫,其他條目需要正確填寫。 | 模塊電路無封面 |

| 8 | 規(guī)定 | 原理圖各頁圖框上除了Checked一項外,均須正確填寫。填寫的內(nèi)容和頁碼、總頁數(shù)等信息應以規(guī)定的用戶變量(Customer Text)進行標注。 | 模塊電路除外 |

| 9 | 規(guī)定 | 除封面頁,每一頁左下角應該采用環(huán)境變量注明修改日期;除封面和目錄頁之外,每頁的左下角標注本頁的功能說明。 | |

| 10 | 規(guī)定 | 原理圖必須署名。多人設計原理圖應在相應頁碼署各自的名字;封面簽署單板負責人姓名。署名采用漢語拼音,大寫字母,姓在前,名在后,以一個英文空格符隔開。對于改版、借鑒的原理圖,簽署最后一次修改者的姓名并由其對原理圖質(zhì)量負責。 | |

| 11 | 提示 | 放置一個Standard庫中的ZTE_frameA4plus圖框,以用戶變量的形式正確填寫所有內(nèi)容,包括說明、日期等信息,其他頁拷貝該頁內(nèi)容可以加快工作速度,并使各頁保持一致。 | |

| 12 | 推薦 | 目錄頁放置2個Contents框,左側(cè)為目錄,右側(cè)為模塊調(diào)用情況。兩框應水平方向應對齊。如果原理圖頁數(shù)較多,目錄頁只寫目錄,增加目錄頁說明模塊調(diào)用情況。 | |

| 13 | 推薦 | 原理圖各頁內(nèi)容依次為:封面、目錄、電源、時鐘、CPU、存儲器、邏輯、背板(母板)接口等。 | |

| 14 | 規(guī)定 | 每頁內(nèi)容緊湊但不雜亂、擁擠。 | |

| 15 | 規(guī)定 | 原理圖上所有的文字方向應該統(tǒng)一,文字的上方應該朝向原理圖的上方(正放文字)或左方(側(cè)放文字)。 | |

| 16 | 規(guī)定 | 原理圖上的各種標注應清晰,不允許文字重疊。 | 交叉標注另行規(guī)定 |

| 17 | 規(guī)定 | 各個芯片的局部去耦電容應和芯片布在同一頁面或者就近放在下一頁面上,并增加說明;多個器件的去耦電容共用一頁圖紙時,應標注去耦電容是為哪個器件放置;全局去耦(旁路)電容可以在電源部分或者原理圖最后部分放置,并增加“GLOBE DECOUPLING”字樣說明。 | |

| 18 | 規(guī)定 | 僅和芯片相關(guān)的上拉或下拉電阻等器件,建議放置在芯片附近。 | |

| 19 | 規(guī)定 | 電阻(電阻網(wǎng)絡除外)、電容(電容網(wǎng)絡除外)、電感的管腳標注,器件的path信息等不必要信息不要顯示。 | |

| 20 | 規(guī)定 | 元器件的位號要顯示在該元件的附近位置,不應引起歧義。 | |

| 21 | 規(guī)定 | 芯片的型號和管腳標注,精密電阻、大功率電阻、極性電容、高耐壓電容、共模電感、變壓器、晶振,保險絲等有特殊要求的器件參數(shù)要顯示出來,LED應標示型號或顏色。 | |

| 22 | 規(guī)定 | 差分信號規(guī)定使用“+/-”符號,“+/-”可以在網(wǎng)絡名的中間或末尾。 | |

| 23 | 推薦 | 無特殊要求(例如系統(tǒng)方案命名需求)差分信號以“+/-”結(jié)尾。 | |

| 24 | 規(guī)定 | E1信號線采用TIP來表示同軸電纜芯線(雙絞線的+),用RING來表示同軸電纜屏蔽層(雙絞線的-)。 | |

| 25 | 規(guī)定 | 有確定含義的低電平有效信號采用*或者_N(引入邏輯的需要用_N)后綴結(jié)尾。“有確定含義”包括但不限于如下信號:片選,讀寫,控制,使能。 | |

| 26 | 規(guī)定 | 所有的時鐘網(wǎng)絡要有網(wǎng)絡標號,以CLK 字符結(jié)尾,以便于SI分析、PCB布線和檢查;非時鐘信號禁止以CLK等時鐘信號命名后綴結(jié)尾。時鐘信號命名應體現(xiàn)出時鐘頻率信息。 | |

| 27 | 規(guī)定 | 采用串聯(lián)端接的信號(包括時鐘),串阻在原理圖上應就近放置于驅(qū)動器的輸出端。串阻和驅(qū)動器之間不放置網(wǎng)絡標號,串阻后的網(wǎng)絡進行命名(時鐘信號必須命名并滿足時鐘信號的命名規(guī)范)。 | |

| 28 | 規(guī)定 | 所有單板內(nèi)部電源網(wǎng)絡的命名都必須采用“VCC”開頭,單板接口電源的定義和系統(tǒng)定義保持統(tǒng)一。 | |

| 29 | 規(guī)定 | 經(jīng)過濾波的電源必須命名,命名也必須以“VCC”開頭。 | |

| 30 | 規(guī)定 | 在PCB布線時有特殊要求的網(wǎng)絡要定義網(wǎng)絡名,推薦在原理圖上注明要求。 | |

| 31 | 推薦 | 全局電源和地應調(diào)用原理圖庫中的符號。 | |

| 32 | 規(guī)定 | 確認多個部分組成的器件原理圖庫,在打包過程中位號正確,沒有出現(xiàn)錯位等現(xiàn)象。 | |

| 33 | 推薦 | 不推薦使用“Location”硬屬性解決位號錯位問題。 | |

| 34 | 規(guī)定 | 使用Alias連接的網(wǎng)絡,必須使用網(wǎng)絡標號的方式進行連接,不能使用連線(wire)進行連接。 | |

| 35 | 規(guī)定 | 禁止使用SIZE屬性放置多個器件,例如測試點、去耦電容、光學定位點等。 | |

| 36 | 規(guī)定 | 所有出頁網(wǎng)絡應放置出頁符offpage/offpg,出頁符的方向應和信號流向一致。原理圖必須進行交叉標注。除總線等字符太多無法調(diào)整的網(wǎng)絡之外,交叉標注的字符不應重疊。 | |

| 37 | 規(guī)定 | offpage/offpg符號的調(diào)用,應根據(jù)信號流向采用正確的符號,不應將符號進行翻轉(zhuǎn)、鏡像后使用。 | |

| 38 | 推薦 | Offpage/offpg符號和交叉標注文字應盡量對齊。 | |

| 39 | 器件管腳上的引線,應引出后再分叉,不得直接在器件管腳上分叉。 | ||

| 40 | 規(guī)定 | 兼容設計、料單可配置部分、調(diào)試用最終不安裝部分器件,應在原理圖上注明。 | |

| 41 | 規(guī)定 | 原理圖中的實現(xiàn)與設計說明中的描述一致。信號的命名應有意義。邏輯芯片管腳命名與設計說明、邏輯設計說明文檔一致。建議信號命名盡量和有意義的芯片管腳命名一致。 | |

| 42 | 規(guī)定 | 提供各單點網(wǎng)絡列表和未連接管腳列表,并一一確認 | |

| 43 | 提示 | 采用Cadence提供的工具對原理圖和PCB的網(wǎng)表一致性進行檢查。 | |

| 44 | 推薦 | 原理圖打印為PDF文件時,推薦使用Arial字體。 | |

| 45 | 規(guī)定 | 模塊電路不加封面和目錄頁。 | |

| 46 | 規(guī)定 | 模塊電路內(nèi)部位號禁止使用硬屬性。 | |

| 47 | 規(guī)定 | 模塊電路使用Standard庫中的inport,outport和ioport和頂層相連。 | |

| 48 | 規(guī)定 | 模塊電路設計其他規(guī)范待添加 |

2 電路設計

通用要求

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 單板網(wǎng)絡的連接必須正確無誤。(個人自查) | |

| 2 | 規(guī)定 | 器件之間的接口電平匹配。 | |

| 3 | 規(guī)定 | PECL到LVPECL的接口使用交流耦合(直流平衡情況)或3電阻端接。采用交流耦合作熱拔插時需注意防止因電容積累電荷放電導致器件損傷,可在電容與單板輸入/輸出接口采用大電阻下拉。 | |

| 4 | 規(guī)定 | 單板熱拔插對外接口器件選型必須能夠滿足熱拔插要求。 | |

| 5 | 規(guī)定 | 熱拔插接口設計,選用的器件內(nèi)部不允許有從端口對電源的二極管鉗位保護網(wǎng)絡。 | |

| 6 | 提示 | 在不同電平接口時利用鉗位二極管實現(xiàn)接口,需要考慮限制電流。 | |

| 7 | 規(guī)定 | 差分信號應考慮Failsafe功能。 | |

| 8 | 提示 | 了解CMOS器件的閂鎖現(xiàn)象,選用不易發(fā)生閂鎖的器件。(一般要求Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II。) | |

| 9 | 規(guī)定 | 器件工作速率符合設計要求。 | |

| 10 | 推薦 | 在滿足系統(tǒng)性能要求的情況下,盡量降低信號的速率,采用慢速器件。 | |

| 11 | 規(guī)定 | 凡公司、事業(yè)部、部門有模塊電路、通用電路,能夠滿足設計要求者,無特殊原因一律采用模塊電路。優(yōu)先選用公司級模塊電路。 | |

| 12 | 規(guī)定 | 無模塊電路可以調(diào)用,但是產(chǎn)品約定設計方式或者器件者,無特殊原因一律按照產(chǎn)品約定進行設計。 | |

| 13 | 規(guī)定 | 相同功能的電路,如無特殊要求應采用相同的電路和器件。 | |

| 14 | 規(guī)定 | 使用同一個物料代碼下有多個器件,確認每一種器件的能夠滿足應用要求。 | |

| 15 | 規(guī)定 | 單板上所有有復位管腳的芯片,要求復位腳軟件可控。 | |

| 16 | 推薦 | CPU等的控制信號應使用上/下拉電阻保證上電時的狀態(tài)確定。 | |

| 17 | 推薦 | 初次設計CPU、DSP和ASIC的配置管腳的上拉或下拉狀態(tài)盡量設計成可調(diào)。 | |

| 18 | 提示 | 閱讀器件手冊時,應該到器件廠商網(wǎng)站上尋找最新版本,并了解其版本變更歷史和查閱最新版本勘誤表。 | |

| 19 | 規(guī)定 | 對于設計中的可配置部分(包括為調(diào)試設計而最終不安裝的部分),必須注明本板在線運行和調(diào)試使用的所有配置方式。 | |

| 20 | 規(guī)定 | 要考慮器件輸出或驅(qū)動器輸出的驅(qū)動能力,等效負載不能超過器件的驅(qū)動能力的80%。 | |

| 21 | 規(guī)定 | MCU串口信號經(jīng)芯片驅(qū)動后,將收發(fā)信號和地引到預留的3Pin插座 | |

| 22 | 規(guī)定 | 單板3Pin RS-232串口插座統(tǒng)一定義為:Pin1—本地發(fā)送Tx;Pin2—地線;Pin3—本地接收Rx。 | |

| 23 | 規(guī)定 | 通用件率滿足事業(yè)部通用件率的要求:新板滿足90%,改版滿足80%。優(yōu)先選用部門推薦的公用器件。 | |

| 24 | 規(guī)定 | ||

| 25 | 規(guī)定 |

邏輯器件應用

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 不帶內(nèi)部上下拉和總線保持功能的CMOS/BiCMOS器件,未用輸入端嚴禁懸空,必須通過電阻進行上拉或下拉處理。 | |

| 2 | 規(guī)定 | 單板帶有可以裁減部分,原理圖中部分器件可能不焊接時,需要確保這些器件不焊接不會導致其他器件的輸入端懸空。 | |

| 3 | 規(guī)定 | 邏輯器件不用的引腳或者固定電平的信號如需預置電平處理,必須通過電阻上拉或者下拉,不允許直接接電源或地。 | |

| 4 | 規(guī)定 | 對器件未用輸入端進行上拉或下拉處理,必須滿足可測試性設計要求。 | |

| 5 | 規(guī)定 | 中斷信號要通過上拉或下拉來使中斷信號處在默認的非觸發(fā)態(tài)。 | 器件手冊規(guī)定優(yōu)先 |

| 6 | 規(guī)定 | 多級具有上電3態(tài)的器件級聯(lián)驅(qū)動信號時,如果信號上電過程要求確定電平,則各級輸入端都必須采用上拉或下拉電阻確定狀態(tài)。 | |

| 7 | 規(guī)定 | 采用具有上電3態(tài)的器件驅(qū)動背板輸入控制信號,如果該信號上電后立刻需要讀取且不受上電復位控制(例如單片機ISP模塊中的背板復位信號和下載使能信號),則必須采用電阻置初始電平。 | |

| 8 | 規(guī)定 | 信號線上的上拉或下拉電阻能夠滿足可靠預置電平要求。 | |

| 9 | 推薦 | 對于CMOS器件,如無特殊要求單個管腳的上拉或下拉可以取10k,多個管腳或其他具體情況可以參見下面的條目和以及進行計算確定。 | |

| 10 | 規(guī)定 | 對使能內(nèi)部上拉的ISP MACH 4000型EPLD,以及和Cyclone型FPGA通用IO管腳連接的網(wǎng)絡,下拉電阻采用1K,上拉電阻可選擇10K。 | |

| 11 | 推薦 | 數(shù)據(jù)總線的下拉不宜使用太大的電阻,推薦使用1K。 | |

| 12 | 規(guī)定 | OSC的ST_N管腳應該加上拉電阻(推薦值為1k,建議直接調(diào)用晶振濾波模塊電路)。 | |

| 13 | 規(guī)定 | 對背板輸出的驅(qū)動器,如果其OE端需要控制,應采用電阻設置為輸出無效狀態(tài)。對于常見的244器件,OE*應該采用電阻上拉。 | |

| 14 | 規(guī)定 | 參照器件的Datasheet將所有控制腳通過電阻進行上拉或下拉,特別是芯片的OE /CE端。 | |

| 15 | 規(guī)定 | Enable、Set、Reset、Clear和三態(tài)器件輸出的上拉、下拉正確 | |

| 16 | 推薦 | 上下拉電阻放在接收端器件處。對于1個驅(qū)動多個接收的網(wǎng)絡,非特殊需要只放置1個上下拉電阻。若接收器件全部放置在同一頁面,在接收器頁面放置上下拉電阻;若接收器件分布在不同頁面上,在驅(qū)動器端放置上下拉電阻。 | |

| 17 | 規(guī)定 | 避免使用一個排阻同時對信號進行上拉和下拉。 | |

| 18 | 規(guī)定 | 如果總線可能處于浮空狀態(tài),那么總線需要有上拉電阻或下拉電阻,保證在沒有器件占用總線時,總線能處于一個有效電平,以降低器件功耗和干擾。 | |

| 19 | 規(guī)定 | UART器件16C55X,如果不使用其DSR、DCD、CTS信號,需要進行下拉,使信號為有效狀態(tài),避免自動流控制的器件不能正常工作。 | |

| 20 | 規(guī)定 | PCI的三態(tài)和OD、OC信號要有上拉。 | |

| 21 | 規(guī)定 | PCI總線設計中FRAME#, TRDY#, IRDY#, DEVSEL#, STOP#, SERR#, PERR#, LOCK#,INTx#, REQ64#和 ACK64#等信號需要采用合適的電阻進行上拉處理。上拉的阻值須依照負載情況計算。 | |

| 22 | 規(guī)定 | 避免輸入信號的緩慢變化(如按鍵復位信號),對緩慢變化的信號需要使用施密特觸發(fā)器輸入的器件進行驅(qū)動。 | |

| 23 | 規(guī)定 | 設計中應防止上電及正常工作時出現(xiàn)總線沖突。對于可能出現(xiàn)沖突的情況,應采用互斥設計,確保不會因為軟件問題導致沖突。 | |

| 24 | 規(guī)定 | 和背板直接相連的驅(qū)動器必須滿足熱拔插要求(我們要求有OE端控制,上電三態(tài)、關(guān)斷電流控制)。 | |

| 25 | 推薦 | MCS-51單片機的總線及端口需要加驅(qū)動。驅(qū)動器選型禁止采用總線保持器件或者內(nèi)置下拉電阻的器件。 | |

| 26 | 推薦 | 原則上不推薦使用總線保持器件或者啟用可編程器件的總線保持功能。 | |

| 27 | 推薦 | 具有BUS-HOLD特性的器件,通過外接上拉或下拉電阻實現(xiàn)狀態(tài)預置時,電阻取值不宜過多于3K,推薦采用1K電阻。 | |

| 28 | 提示 | BUS HOLD器件,不論其輸出端口處于何種狀態(tài),其輸入端口的BUS HOLD特性一直有效。對于雙向器件,其兩個方向端口在輸出高阻態(tài)下輸入Bus Hold特性一直有效。 | |

| 29 | 規(guī)定 | 與背板相連的普通邏輯電平信號,如非特別要求,需要采用串接電阻;背板輸入的信號,為防止當發(fā)送端關(guān)斷、未插、掉電時懸空,應采用上拉或下拉電阻,選擇上拉還是下拉的原則是一塊板的局部失效不會對其他板產(chǎn)生嚴重影響。 | 信號完整性優(yōu)先 |

| 30 | 推薦 | 一般情況下背板接口輸出串聯(lián)電阻選取33.2歐姆(或33歐姆排阻),輸入串聯(lián)電阻選擇100歐姆電阻或者排阻。對于既有輸出又有輸入的信號,如果單板布線布局困難,可以考慮采用一個33歐姆電阻;對于總線型拓撲負載多于4個時,應根據(jù)SI仿真測試結(jié)果選取電阻;對于需要把發(fā)送到背板的信號收回來的拓撲,必須在33驅(qū)動器輸出端直接輸入,不得在33歐姆電阻后接收。 | 信號完整性優(yōu)先 |

| 31 | 推薦 | 背板輸入信號緩沖器應用下拉電阻和串阻。背板輸入信號緩沖器下拉電阻取10K,串阻取100歐姆。背板輸入信號緩沖器輸入先下拉再經(jīng)過串阻,設計上會具有更大的靈活性。設計中應嚴格遵守產(chǎn)品設計約定。 | |

| 32 | 推薦 | 對于總線保持器件或者輸入內(nèi)置上下拉的器件,未用輸入管腳懸空處理。 | |

時鐘設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 對于輸出多于5個的時鐘驅(qū)動芯片,電源推薦采用磁珠濾波,磁珠后應該添加電解電容和足夠的陶瓷去耦電容,布局時推薦局部鋪一小塊銅皮。 | |

| 2 | 推薦 | 時鐘芯片的電源和地參考器件手冊處理。對鎖相環(huán)電源采用磁珠濾波的,磁珠后應該采用多級陶瓷去耦電容以保證電源低阻抗。 | |

| 3 | 推薦 | 單板50MHz以上時鐘驅(qū)動器件未用管腳,備用放置不大于15pF的電容接地平面。該電容缺省不焊,如果EMC測試高頻輻射超標,可以焊上調(diào)試。 | 參見說明 |

| 4 | 推薦 | 時鐘驅(qū)動器件未用管腳對平面電阻/電容采用分立器件,不得使用排阻排容。 | |

| 5 | 規(guī)定 | 時鐘信號網(wǎng)絡必須采用合適的端接方式。 | |

| 6 | 推薦 | 時鐘網(wǎng)絡推薦采用點對點,源端端接方式。 | |

| 7 | 規(guī)定 | 當接口標準或器件對時鐘網(wǎng)絡等布線有要求時,依照接口標準或器件要求執(zhí)行。 | |

| 8 | 規(guī)定 | 鎖相環(huán)串聯(lián)使用,須注意不會引發(fā)諧振。 | |

| 9 | 推薦 | 不推薦使用多通道輸入時鐘驅(qū)動器驅(qū)動不同時鐘。 | |

| 10 | 推薦 | 板間傳輸?shù)臅r鐘信號,上單板后在時鐘的輸入端備用去回鉤電容。 | |

| 11 | 推薦 | 子卡與母板間傳輸?shù)臅r鐘,應保證子卡不在位時,時鐘輸入不懸空,時鐘的輸出有匹配。 | |

| 12 | 推薦 | 對于VCXO,如果要求寬的牽引范圍(如±90ppm),不要選用3次泛音晶振。 |

保護器件應用

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | TVS管的最大鉗位電壓VCMAX應不大于電路的最大允許安全電壓。 | |

| 2 | 規(guī)定 | TVS管的最大反向工作電壓VRWM應不低于電路的最大工作電壓,一般可選VRWM為電路最高工作電壓的1.1~1.2倍。 | |

| 3 | 規(guī)定 | TVS管的額定最大脈沖功率必須大于電路中出現(xiàn)的最大瞬態(tài)浪涌功率。 | |

| 4 | 規(guī)定 | 對于高速鏈路,需要考慮TVS管結(jié)電容的要求 | |

| 5 | 規(guī)定 | 注意單向和雙向TVS管的選擇。 | |

| 6 | 規(guī)定 | 在RS-232鏈路中必須采用雙向TVS管。TVS管放在信號線串聯(lián)電阻外側(cè),單板入口處;串聯(lián)電阻靠近232接口器件放置。 | |

| 7 | 規(guī)定 | TVS器件的選型時要考慮器件的響應時間滿足要求。 | |

| 8 | 規(guī)定 | 當TVS和壓敏電阻聯(lián)合使用進行浪涌保護時,壓敏電阻的壓敏電壓要低于TVS的鉗位電壓VC。 | |

| 9 | 規(guī)定 | 保護器件應與被保護器件接在相同的地平面。如采用變壓器隔離,隔離變壓器初次級兩側(cè)的器件要分別接對應的參考地。 | |

| 10 | 規(guī)定 | PTC與TVS配合使用時,PTC要能及時動作,對TVS進行過流保護,同時,PTC本身也要能夠滿足工作電壓的要求。 | |

| 11 | 規(guī)定 | 對于需要出機框的信號線(例如勤務電話、網(wǎng)線、E1線、232、485等等),需要添加保護電路或者進行隔離;對于在機架內(nèi)部的信號線一般不需要添加保護電路。 |

可編程邏輯器件

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 推薦 | FPGA的LE資源利用率要保證在50%~80%之間,EPLD的MC資源的利用率要保證在50%~90%之間。對于FPGA中的鎖相環(huán)、RAM、乘法器、DSP單元、CPU核等資源,經(jīng)過精確預算,允許使用到100%。 | |

| 2 | 推薦 | 預留一定數(shù)量的測試IO(一般推薦不小于實際使用的IO數(shù)的10%),測試IO中要有一定量(不少于40%)要連接在測試針上。根據(jù)邏輯的復雜程度和管腳占用情況、版面緊湊程度可以斟酌安排。第一版測試針可以多留一些,穩(wěn)定之后的版本可以少一些。 | |

| 3 | 規(guī)定 | 可編程邏輯器件的輸入時鐘至少有一個本地的不間斷時鐘。CPU接口等部分的設計,必須采用本地時鐘完成。 | |

| 4 | 規(guī)定 | 對于邏輯芯片的輸入時鐘,如果使用內(nèi)部鎖相環(huán),必須保證時鐘的輸入頻率、占空比、抖動、輸出頻率滿足鎖相環(huán)要求。鎖相環(huán)電路盡量按照芯片提供的參考電路設計。 | |

| 5 | 規(guī)定 | 對于可編程邏輯器件的懸空管腳(包括測試管腳、設計裁減導致的懸空輸入等),必須確認其在正常工作中不能懸空。 | |

| 6 | 推薦 | Lattice ISP Mach4000系列器件,建議使能內(nèi)部上拉,外部上拉采用10K,下拉采用1K設計。 | 參考上下拉部分規(guī)范 |

| 7 | 推薦 | 一般情況下,Cyclone器件外圍上拉可采用10K,下拉采用1K設計,避免下載之前出現(xiàn)不定態(tài)電平。 | 參考上下拉部分規(guī)范 |

| 8 | 提示 | Cyclone器件設計時應對可能懸空的輸出管腳使能內(nèi)部上拉。 | |

| 9 | 規(guī)定 | PLD設計中,不推薦使用可編程的總線保持功能。 | |

| 10 | 規(guī)定 | EPLD/FPGA的專用輸入管腳(時鐘輸入管腳)不要懸空 | |

| 11 | 規(guī)定 | FPGA的Done指示管腳(包括Conf_Done和Init_Done信號)需要被監(jiān)控。 | |

| 12 | 規(guī)定 | 不要用特殊管腳當做普通的IO使用。 | |

| 13 | 規(guī)定 | FPGA全局時鐘輸入必須從全局時鐘輸入管腳引入;其他時鐘信號也應盡量從專用時鐘輸入管腳引入;全局復位以及其他全局信號盡量從專用的全局引腳引入。 | |

| 14 | 規(guī)定 | 邏輯芯片的nConfig、Conf_Done和nStatus管腳應上拉,電阻選擇參考手冊規(guī)定。 | |

| 15 | 推薦 | 為了防止FPGA的nConfig信號受到毛刺干擾,導致邏輯芯片異常掉邏輯,可在nConfig管腳加一個RC電路。RC電路靠近FPGA防止 | |

| 16 | 規(guī)定 | 對于采用AS模式下載的設計,要保證nConfig的上升沿落在3.3V電源穩(wěn)定之后。 | |

| 17 | 提示 | 可能的話提供一定的慢速時鐘給EPLD/FPGA,在長定時時可以節(jié)省資源。 | |

電源設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 熱拔插系統(tǒng)必須使用電源緩啟動設計。 | |

| 2 | 推薦 | 在壓差較大或者電流較大的降壓電源設計中,建議采用開關(guān)電源,避免使用LDO作為電源。對紋波要求較高的場合中,可以采用開關(guān)電源和LDO串聯(lián)使用的方法。 | |

| 3 | 規(guī)定 | LDO輸出端濾波電容選取時注意參照手冊要求的最小電容、電容的ESR/ESL等要求確保電路穩(wěn)定。推薦采用多個等值電容并聯(lián)的方式,增加可靠性以及提高性能。 | |

| 4 | 推薦 | 電源濾波可采用RC、LC、π型濾波。電源濾波建議優(yōu)選磁珠,然后才是電感。同時電阻、電感和磁珠必須考慮其電阻產(chǎn)生的壓降。 | |

| 5 | 規(guī)定 | 大容量電容應并聯(lián)小容量陶瓷貼片電容使用。 | |

| 6 | 規(guī)定 | 電源必須有限流保護。 | |

| 7 | 推薦 | 升壓電源(BOOST)使用必須增加一個保險管以防止負載短路時,電源直通而導致整個單板工作掉電。保險的大小由模塊的最大輸出電流或者負載最大電流而定。 | |

| 8 | 規(guī)定 | 單板輸入電源要有防反接處理,輸入電流超過3A,輸入電源反接只允許損壞保險絲;低于或等于3A,輸入電源反接不允許損壞任何器件。 | |

| 9 | 規(guī)定 | 電源禁用磁飽和電路;禁止選用采用磁飽和電路的電源模塊。 | |

| 10 | 規(guī)定 | 對于多工作電源的器件,必須滿足其電源上掉電順序要求。 | |

| 11 | 提示 | 多個芯片配合工作,必須在最慢上電器件初始化完成后開始操作。 | |

| 12 | 推薦 | 采用SO-8封裝的LDO(如MIC5209BM),用于密封環(huán)境時,為保證熱應力降額滿足要求,通常熱耗不應超過0.3W。 | 以可靠性工程師熱設計為準 |

| 13 | 提示 | 電源控制芯片JTAG下載口單獨引出。 | |

| 14 | 推薦 | 在存在分板工藝,以及需要過波峰焊的單板上,-48V電源濾波盡量避免使用貼片陶瓷電容,必須使用的要保證布局時避免電容受到過多機械應力。 | |

| 15 | 規(guī)定 | 單板電源引出單板使用,應該添加限流保護措施,避免外部負載短路造成單板無法正常工作。 | |

| 16 | 推薦 | 電源模快/芯片感應端在布局時應采用開爾文方式。 | |

| 17 | 提示 | 三端穩(wěn)壓器輸出到輸入應該有反向泄放二極管,防止掉電時損壞器件。 | |

| 18 | 提示 | 不允許出現(xiàn)過大壓差的不同電源之間,可用二極管限制壓差。 | |

其他應用經(jīng)驗

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 使用CY2302時鐘驅(qū)動器,應注意如果對輸入輸出時鐘的相位要求一致,那么必須選擇OUT2反饋、OUT1輸出。 | |

| 2 | 規(guī)定 | 有極性的耦合電容注意其直流偏置電壓,尤其是串聯(lián)電感使用時應防止反向電壓的產(chǎn)生。 | |

| 3 | 規(guī)定 | 電容的耐壓和溫度降額都必須滿足公司降額要求。工作溫度升高,電壓的降額程度要增大。 | |

| 4 | 規(guī)定 | 電阻的功率和溫度降額都必須滿足公司降額要求。工作溫度升高,功率的降額程度要增大。 | |

| 5 | 規(guī)定 | ADM706R在使用中應該將PFI直接接電源,避免器件上電時進入測試模式。公司通用電路采用上下拉設計。在ADM706更改設計之前,我部門指定不使用ADM706R器件,采用MAX706避免此問題。 | |

| 6 | 規(guī)定 | MPC860 的TRST*設計時接/PRESET,避免器件上電時進入測試模式。 | |

| 7 | 規(guī)定 | 860的TA上拉要1K,不能太大。 | |

| 8 | 規(guī)定 | 在使用MPC860的設計中,如果只對MPC860硬件復位配置字用到的部分數(shù)據(jù)線通過硬件復位配置字驅(qū)動器進行驅(qū)動,其他數(shù)據(jù)線默認為MPC860內(nèi)部下拉,那么MPC860的數(shù)據(jù)總線不能使用帶總線保持功能的驅(qū)動器。 | |

| 9 | 規(guī)定 | 系統(tǒng)應對指示燈顏色、狀態(tài)進行規(guī)定。指示燈設計,綠燈亮/滅表示正常或者工作狀態(tài),紅燈亮表示有告警,滅表示無告警。特殊情況下允許采用黃燈指示。除非外觀需要,不推薦采用其他顏色的指示燈。 | |

| 10 | 規(guī)定 | 面板燈必須經(jīng)過驅(qū)動器進行驅(qū)動,應該采用低電平有效方式點燈(純電源板另外考慮)。 | |

| 11 | 規(guī)定 | 面板指示燈/輸入輸出外部信號不與單板內(nèi)重要信號共用驅(qū)動器。 | |

| 12 | 規(guī)定 | 面板燈5V使用510歐姆左右的電阻,3.3V使用330歐姆左右的電阻。電阻應在公司通用件庫中選取常用器件。 | |

| 13 | 規(guī)定 | 單板內(nèi)部3.3V指示燈推薦統(tǒng)一采用1K限流電阻。 | |

| 14 | 規(guī)定 | 內(nèi)部電源指示燈,如果電源電壓低于2V,必須經(jīng)過三極管驅(qū)動發(fā)光二極管。 | |

| 15 | 規(guī)定 | 面板燈(撥碼開關(guān)、按鈕)等上串接的電阻必須接在驅(qū)動器和指示燈(開關(guān)、按鈕)之間,電阻靠近驅(qū)動器放置,避免外界干擾對驅(qū)動器的沖擊。 | |

| 16 | 推薦 | 單板內(nèi)部指示燈推薦使用低電平驅(qū)動指示燈,驅(qū)動能力足夠時可以采用高電平點燈,選擇主要從節(jié)省成本角度出發(fā)。 | |

| 17 | 規(guī)定 | 單板內(nèi)必須有電源指示,邏輯下載指示燈 | |

| 18 | 規(guī)定 | ADC和DAC的模擬地和數(shù)字地引腳,在外面應該用最短的連線接到同一個低阻抗的接地平面上。 | |

| 19 | 提示 | 以太網(wǎng)非點對點連接時。PHY器件的驅(qū)動能力在器件的允許范圍內(nèi)要調(diào)到最大。 | |

| 20 | 規(guī)定 | 正確配置CPU的上電配置管腳,配置管腳通過電阻上拉或下拉。(配置的內(nèi)容主要包括:BOOT的數(shù)據(jù)寬度、FLASH的數(shù)據(jù)寬度、時鐘的工作模式、地址映射模式、PCI的主從模式、PCI仲裁使能、BOOT是從LOCATION BUS還是PCI上啟動、鎖相環(huán)時鐘配置、輸出阻抗等) | |

| 21 | 規(guī)定 | MOSFET的柵極(Gate)串10歐姆電阻可有效抑止振蕩;MOSFET并聯(lián)使用時,每個MOSFET的柵極要分別串10歐姆電阻。電阻盡量靠近柵極放置。 | |

| 22 | 規(guī)定 | 與MOSFET柵極并聯(lián)的ZENER二極管可能會引發(fā)振蕩,要將其連接到柵極串阻的外側(cè)。 | |

| 23 | 規(guī)定 | 與MOSFET柵極并聯(lián)的電容可能會引發(fā)振蕩,要將其連接到柵極串阻的外側(cè)。注意并聯(lián)電容減慢了開關(guān)的速度,增加了MOSFET 并聯(lián)應用時的不平衡。 | |

| 24 | 提示 | 保證MOSFET的柵極驅(qū)動類似一個電壓源,具有盡可能小的阻抗。 | |

| 25 | 提示 | 漏極和源極間并聯(lián)阻容緩沖器或并聯(lián)齊納二極管和電容的串聯(lián)吸收電路,這樣在管子關(guān)斷時漏極電流較快減小,使漏源極之間的電壓在擊穿電壓值之下,起到保護管子的作用。 | |

| 26 | 提示 | 應減小MOSFET柵極電壓的上升時間,使MOSFET盡量少的時間處于負溫度系數(shù)區(qū)域,從而降低熱失控的危險。 | |

| 27 | 提示 | MT9040、IDT82V3001A等鎖相環(huán)上電后或輸入?yún)⒖碱l率改變后必須復位鎖相環(huán)。 | |

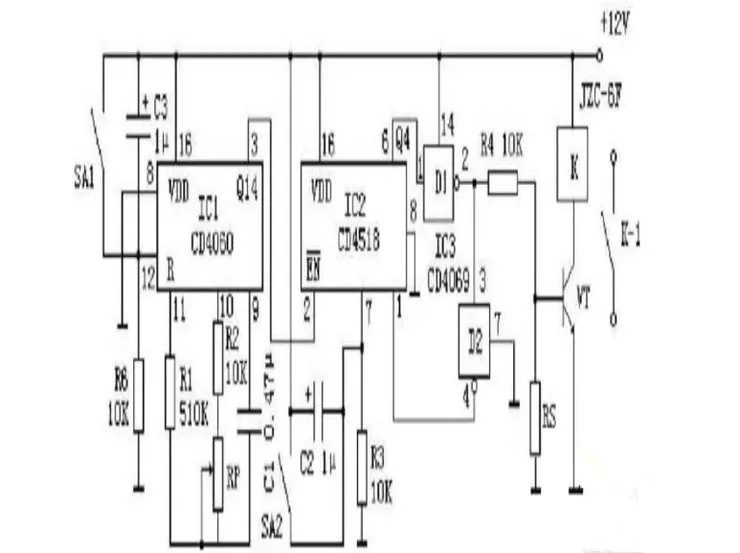

| 28 | 規(guī)定 | 繼電器線圈、風扇電機繞組等感性負載必須有續(xù)流二極管。 | |

| 29 | 規(guī)定 | 繼電器線圈工作電壓不允許降額使用,繼電器在應用中應注意是線圈是否有極性要求,避免退磁。 | |

| 30 | 提示 | 繼電器電路在設計中,應盡量讓繼電器長期處于釋放狀態(tài),減小功耗,并減小線圈溫升降低壽命的概率。 | |

| 31 | 提示 |

要保證光電耦合器能可靠地工作在開關(guān)狀態(tài), IF取值不能太小(可取值CTR最大值對應IF的40%左右),并且集電極負載電阻要滿足如下的關(guān)系式: (VCC-VIL)/(CTR(min)*IF-II)? £RL£ (VCC – VIH)/( ICEO + II)。 |

|

| 32 | 規(guī)定 | 按鍵、跳線、撥碼開關(guān)與IC端口之間串接小電阻(推薦100歐姆)或并接TVS管做ESD防護。推薦采用電阻以節(jié)省成本。對于上下拉都有電阻的設計方式,可將電阻放在跳線和器件之間作為保護。 | |

| 33 | 規(guī)定 | 運算放大器設計為放大器時,同相輸入和反相輸入端的輸入等效電阻要一致,減小輸入偏置電流和誤差電流引起的的誤差和噪聲。 | |

| 34 | 規(guī)定 | ADC、DAC如果使用外部電壓參考,應注意參考電壓的精度和穩(wěn)定性,只有在要求不高的情況下才可以采用電源作為參考電壓,并且必須經(jīng)過濾波。 | |

| 35 | 推薦 | 單板上有多個處理器或高速器件,并且各處理器/高速器件對時鐘同相工作無要求時,各器件的時鐘相位盡量錯開,減少同時動作的邏輯門數(shù)量,降低瞬態(tài)工作電流,從而降低單板或系統(tǒng)的EMI。 | |

| 36 | 提示 | 三態(tài)/OC/OD時分數(shù)據(jù)/狀態(tài)總線釋放時應注意釋放速度的問題。 | |

| 37 | 規(guī)定 | 非變壓器隔離的差分信號,例如RS-485信號,LVDS信號等,發(fā)送和接收側(cè)必須采用相同的參考地。 | |

| 38 |

3  可靠性設計

可靠性設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 鉭電容的耐壓要降額到1/3以下。 | |

| 2 | 推薦 | 紋波電流大和沖擊電流大可能引起鉭電容失效,故沖擊電流場合慎用鉭電容,熱插拔等電源瞬變場合謹慎選用鉭電容。 | |

| 3 | 推薦 | 避免使用大容量鉭電容;可用并聯(lián)的形式。 | |

| 4 | 規(guī)定 | 鉭電容失效易產(chǎn)生明火,故避免明火的場合慎用鉭電容。 | |

| 5 | 規(guī)定 | 電源模塊選型時,應確保電源模塊上的鉭電容符合降額標準。 | |

| 6 | 規(guī)定 | 工業(yè)級及商業(yè)級器件在實際使用中,結(jié)溫降額應采用同樣的降額標準,以確保實際使用中具有較高的可靠性水平。 | |

| 7 | 規(guī)定 | 面板監(jiān)控線纜必須加入防靜電保護電路(調(diào)用部門模塊電路)。 | |

| 8 | 推薦 | 單板上關(guān)鍵芯片、功耗較大IC,附近預留接地插座以備未來加裝散熱器接地用 | |

| 9 | 規(guī)定 | 散熱器盡量多點、低阻抗、短距離接工作地平面。散熱器與支柱、螺釘?shù)鹊倪B接處采用星月孔與工作地平面連接; | |

| 10 | 規(guī)定 | LDO等芯片的散熱體如果是接在電源腳上時,與之接觸的散熱器應該多點接到該電源上。 | |

| 11 | 規(guī)定 | 器件或模塊對散熱器接地有明確要求時,按要求接地。如:帶鋁基板電源模塊的基板和安裝孔及散熱器要接保護地。 | |

| 12 | 規(guī)定 | 單板上無法實現(xiàn)將散熱器接地方式處理時,散熱器可以采用浮空方式。 | |

| 13 | 規(guī)定 | 同軸電纜的外屏蔽層,屏蔽電纜的屏蔽層可以通過接口接保護地 | |

| 14 | 規(guī)定 | 明確標注金屬殼體的處理方式 | |

| 15 | 推薦 |

器件帶有金屬殼體的引腳,將引腳連接到相應的地上。 ESD防護器件接地端、金屬外殼的元器件的金屬外殼、屏蔽裝置接到靜電防護與屏蔽地; 具有金屬殼體而人手又經(jīng)常接觸的部件如接插件等部件,其金屬殼體應與接地的機殼或底板緊密相連。內(nèi)部電路在靠近這些部件的部位,應采用大面積接地。 |

|

| 16 | 推薦 | 如果上面的規(guī)則實現(xiàn)困難,推薦金屬殼體接地的優(yōu)先順序:通過泄放電阻連接到屏蔽地>保護地>工作地 | |

| 17 | 提示 | 對于一些敏感電路,設計中應進行容限分析,以確認器件選型滿足電路容限要求。 | |

| 18 | 規(guī)定 | 單板保險絲降額合理(額定電流降額至少50%,標稱熔斷熱降額至20%),應放在保護器件的前面。對于可能工作于溫度較高環(huán)境的設計,必須充分考慮保險絲降額。 | |

| 19 | 提示 | 對于沖擊電流很大的場合,保險絲不能按照標稱的熔斷熱計算。有案例表明,即使很大降額,仍然不能滿足要求。廠家不能解釋。增加緩啟動是根本方法,不能加緩起可以考慮不用保險絲。 | |

| 20 | 規(guī)定 | 盡量不采用無鎖定裝置的連接器,必須使用時需評審。 | |

| 21 | 提示 | 跳線帽和撥碼開關(guān)等機械器件存在可靠性,腐蝕等多方面問題,且失效模式通常容易使系統(tǒng)進入不正常的分支。盡量避免使用,通過電阻的方式用料單區(qū)分。 | |

4  信號完整性/電源完整性設計

信號完整性/電源完整性設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 提示 | 選擇更不易造成信號完整性問題的接口方式/器件。 | |

| 2 | 規(guī)定 | 關(guān)鍵路徑經(jīng)過時序設計,具備時序分析報告。凡涉及時序控制的電路,比如CPU/FPGA/專用IC訪問外掛存儲器等必須進行時序分析。 | 時序設計另行規(guī)定 |

| 3 | 規(guī)定 |

滿足以下任意一項或多項的網(wǎng)絡必須附帶信號完整性前仿真分析報告: 時鐘信號;頻率較高;有較嚴格的時序要求;對邊沿單調(diào)性有要求(邊沿敏感信號);網(wǎng)絡拓撲復雜(帶有多個分支和負載);對過沖等敏感(參見器件手冊);相關(guān)標準對信號質(zhì)量有要求。 |

SI仿真另行規(guī)定 |

| 4 | 推薦 | 采用16244驅(qū)動器驅(qū)動變化信號,建議在驅(qū)動器輸出添加33.2歐姆電阻或者33歐姆排阻。 | |

| 5 | 提示 | 有一些可編程邏輯器件可以設置輸出的驅(qū)動強度、電流等參數(shù),通過合理設置可以改善信號完整性。 | |

| 6 | 提示 | 如果時序允許,應將可編程邏輯器件的輸出擺率設置為慢擺率。 | |

| 7 | 推薦 | 讀寫信號的驅(qū)動拓撲應盡量簡化,必要應采用多個驅(qū)動器的方法簡化拓撲,并進行信號完整性仿真,采用合適的端接。 | |

| 8 | 推薦 | 可編程邏輯器件,輸出交變信號時應進行端接。不便端接的信號應采用設置電流、擺率等方式改善信號完整性。 | |

| 9 | 提示 | 單向的片選等信號,可以采用源端端接。 | |

| 10 | 規(guī)定 | EPLD/FPGA輸出的UART時鐘等交變信號,必須進行端接。 | |

| 11 | 規(guī)定 | 電源上電解電容的數(shù)目應該滿足電源完整性要求。 | |

| 12 | 規(guī)定 | 去耦電容的設計滿足對工作電源的目標阻抗的要求,并按PI分析報告實施。 | PI設計另行規(guī)定 |

| 13 | 推薦 | 考慮為換層、穿越平面割裂的信號配置旁路電容。 | |

| 14 | 推薦 | 在需要對電源完整性進行測試的位置,放置電源完整性測試點。 | |

| 15 | 規(guī)定 | 對處理器等大規(guī)模關(guān)鍵器件,必須放置電源完整性測試點。 |

5  系統(tǒng)相關(guān)設計

系統(tǒng)相關(guān)設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 單板接口設計要和設計規(guī)范保持完全一致。 | |

| 2 | 規(guī)定 | 背板插座上本板沒有使用的PIN,不要連接到單板內(nèi)的任何網(wǎng)絡。 | |

| 3 | 規(guī)定 | 熱插拔系統(tǒng)的接口不應采用不支持插拔的標準。 | |

| 4 | 規(guī)定 | 熱拔插系統(tǒng)避免使用I2C總線。如因歷史原因使用I2C總線,電源須采用二極管防止電流反灌。 | |

| 5 | 規(guī)定 | 背板輸入的TTL/CMOS控制信號應該設置成高電平有效,一般情況處于低電平。 | |

| 6 | 規(guī)定 | 單板輸出到背板的總線信號以及主備單板公用的信號,在單板上電前、單板異常狀態(tài)下處于高阻態(tài),各控制和狀態(tài)信號符合設計方案約束。 | |

| 7 | 規(guī)定 | 單板在局部掉電時不應出現(xiàn)器件損壞,不影響其他單板總線信號。 | |

| 8 | 推薦 | 在基本不增加成本的情況下,在第一版設計時,建議保留可調(diào)部分設計,并增加可調(diào)部分的設計和冗余設計,要盡量多的增加可調(diào)部分的設計。如,通過電阻或跳線實現(xiàn)靈活的功能選擇、盡量多的引出測試點、合理使用器件的空閑管腳增加器件之間的冗余通道(特別是邏輯器件之間),不同器件方案驗證的兼容設計等。 | |

| 9 | 規(guī)定 | 單板運行時不需要進行調(diào)節(jié)的地方一律不用可調(diào)器件。 | |

| 10 | 推薦 | 設計應保證所有測試使用的跳線帽、跳線針在最終產(chǎn)品中不需安裝。 | |

| 11 | 規(guī)定 | 系統(tǒng)設計階段必須進行系統(tǒng)級信號完整性設計,盡量避免復雜拓撲,對每塊單板接口的拓撲進行約束,時鐘等關(guān)鍵信號盡量采用點對點方式傳送。 | |

| 12 | 規(guī)定 | 系統(tǒng)設計階段必須進行系統(tǒng)接口時序設計,考慮連接器、變化負載、溫度、信號完整性等帶來的波動,留出充分時序裕量,并規(guī)定各單板接口時序。 | |

| 13 | 規(guī)定 | RS-485應考慮Fail Safe設計,在空閑時差分電平應為200mV以上。 | |

| 14 | 提示 | RS-485上拉或下拉偏置電阻的選擇要注意器件的驅(qū)動能力。 | |

| 15 | 提示 | RS-485總線要考慮總線上多塊單板并聯(lián)時總線上負載的影響。 | |

| 16 | 推薦 | 單板能夠檢測自己輸出的數(shù)據(jù)、時鐘,方便故障定位。 | |

| 17 | 規(guī)定 | 應能夠承受可能出現(xiàn)的最大電流 (包括熱插拔時的電流)。插座有額定電流的參數(shù),插座電源的針承受最大電流不得超過其額定電流,并要求有一定的降額。例如歐式48PIN的插座,每根針通過的電流不得超過1A。 | |

| 18 | 推薦 | 面板的RUN,ALARM燈用軟件來控制,其他燈由硬件控制點亮。 | |

| 19 | 推薦 | 子卡連接器定義時,不用的插針接地,分布分配,減小信號線間互感串擾。 | |

| 20 | 推薦 | E1接口RING接地遵守公司慣例,發(fā)端接地,收端建議可配置為直接接地或者通過電容接地。可以套用公司模塊電路的,依照公司模塊電路實施。 | |

| 21 | 規(guī)定 | 需要熱拔插的接口,在連接器選型時必須保證工作地先于信號和電源連接。推薦的順序為地線-電源-信號。 | |

| 22 | 規(guī)定 | 用于電纜互連的連接器,設計時注意信號引腳之間定義足夠的地信號,以減小回流路徑,降低信號之間的串擾,特別是電纜中的時鐘信號和小信號要用地線與其它信號隔離。 | |

| 23 | 推薦 | 系統(tǒng)設計時主控單板和受控單板間增加少量備用的信號線,在背板上予以設計,以提高系統(tǒng)的可升級性。 | |

| 24 | 提示 | 資源板用量較大,尤其要考慮成本因素,盡量采用可裁剪配置的設計方法。綜合器件平滑升級設計的原則,盡量選擇成本較低器件。 | |

| 25 | 推薦 | 單板應采用面板扳手狀態(tài)監(jiān)控電路監(jiān)控面板扳手狀態(tài),并定義背板連接器左上角、右上角、左下角、右下角四根針為查拔到位指示信號。面板監(jiān)控電路應采用防靜電模塊避免靜電騷擾。 | |

| 26 | 提示 | 主備單板切換應盡量減少對系統(tǒng)的影響:負責時鐘分發(fā)單板應考慮時鐘不丟失,不錯誤;復位、拔出主用單板應考慮盡量檢測到操作并在復位、拔插前發(fā)起主備倒換;拔出、插入備用單板不應對主板工作產(chǎn)生影響。 | 參見說明分析 |

6  可生產(chǎn)性設計

可生產(chǎn)性設計

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 選用的器件必須滿足公司生產(chǎn)工藝要求,布局須通過公司工藝技術(shù)人員審核。 | |

| 2 | 規(guī)定 | 靜電敏感器件慎用,如果采用要加防靜電保護措施。 | |

| 3 | 規(guī)定 | 放置數(shù)量恰當?shù)腗ark點,數(shù)量參考原理圖設計規(guī)范確定。 | |

| 4 | 規(guī)定 | 雙面貼焊的單板,在選擇器件時盡量使用貼片器件,不使用插裝器件。盡量使單板采用雙面回流焊工藝。 | |

| 5 | 規(guī)定 | 除非信號完整性特殊要求,背板上一般不應放置串阻等器件。背板盡量采用壓接連接器,避免焊接連接器。 | |

| 6 | 提示 | 選用器件應注意器件的潮敏等級,必要時注明以保證生產(chǎn)加工可靠性;其間選型時避免選擇潮敏等級高的器件。 | |

| 7 | 推薦 | 因為焊接溫度不同,盡量避免板內(nèi)有鉛無鉛工藝器件混用。 | |

| 8 |

7  可測試性設計

可測試性設計

JTAG

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 含JTAG口的器件都需要使用事業(yè)部規(guī)定的JTAG接口電路,單板提供JTAG插座。 | |

| 2 | 規(guī)定 | 芯片的JTAG口管腳TDI,TMS,TCK,TRST(若有)可控,不能懸空或直接拉低/拉高(注意芯片內(nèi)部的上/下拉電阻)。 | |

| 3 | 規(guī)定 | 芯片的TCK,TMS的驅(qū)動能力滿足掃描鏈路的要求。 | |

| 4 | 規(guī)定 | 芯片的BSDL文件要齊全、完整和正確。 | |

| 5 | 推薦 | 多個同樣的芯片,設計JTAG串行鏈路。 | |

| 6 | 規(guī)定 | 不同芯片,單獨設計JTAG鏈路。 | |

| 7 | 提示 | 設計中TRST*管腳注意正確上拉或下拉,確保測試模式不被啟動。 | |

| 8 | 提示 | 電源控制芯片JTAG下載口單獨引出。 | |

| 9 | 提示 | Xilinx Spartan III器件的JTAG接口為2.5V,設計中須防止過壓。 |

測試點

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 測試點滿足康訊的可測試性要求。應設置充分的內(nèi)部和外部測試點,以便給測量、故障檢測和故障隔離提供手段。測試點應有盡量明顯的標記。 | |

| 2 | 規(guī)定 | 電源和地必須有足夠的通孔測試點,要求每一種電源都至少有一個測試點,地的測試點至少每10cm一個,要求平均分布在單板上。 | |

| 3 | 推薦 | 高頻時鐘信號或高速信號的測試點旁邊應放置接地測試點;信號的測試點應該放在接收端。 | |

| 4 | 規(guī)定 | 時序較為復雜的信號要求每個信號都引出測試點,以方便單板測試。布局時必須注意測試點(包括ICT測試點)引入的分岔盡量短,不得影響信號的信號完整性。對速度很高的信號,必須考慮測試點引入的阻抗不連續(xù)對信號的影響。 | |

| 5 | 推薦 | 多針測試點,空余的管腳應接地處理。 | |

| 6 | 規(guī)定 | 向PCB提供不焊接插裝器件清單。 |

電路可測試性

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 時鐘電路或振蕩器電路的輸出可控。 | |

| 2 | 規(guī)定 | 數(shù)字器件特殊引腳需要全部獨立處理。 | |

| 3 | 推薦 | 反饋回路可以斷開。 |

系統(tǒng)可測試性

| 編號 | 級別 | 條目內(nèi)容 | 備注 |

| 1 | 規(guī)定 | 對輸入單板內(nèi)的時鐘進行檢測。 | |

| 2 | 規(guī)定 | 對從背板輸入或輸出至背板的數(shù)字IO信號線的可以控制 | |

| 3 | 推薦 | CPU能夠檢測輸入單板的信號狀態(tài),便于實現(xiàn)系統(tǒng)互聯(lián)時的測試。 |

整理自百度文庫《CDMA事業(yè)部設計開發(fā)部電路設計規(guī)范》

審核編輯 黃宇

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

電路設計

+關(guān)注

關(guān)注

6665文章

2428瀏覽量

203316 -

中興

+關(guān)注

關(guān)注

6文章

1995瀏覽量

66010 -

ZTE

+關(guān)注

關(guān)注

0文章

24瀏覽量

9072

發(fā)布評論請先 登錄

相關(guān)推薦

硬件電路設計的思路介紹

原理圖以及電子元件型號,如何查找移步:元件及其規(guī)格書的查找與理解。 2、沒有參考設計,自主設計 1)確定設計目標:確定硬件電路設計的目標和要求,例如性能、功耗、成本等方面。 1)選擇適合的芯片:根據(jù)設計目標選擇適合的芯片,查找Data

硬件電路設計的一般思路

原理圖以及電子元件型號,如何查找移步:元件及其規(guī)格書的查找與理解。 2、沒有參考設計,自主設計 1)確定設計目標:確定硬件電路設計的目標和要求,例如性能、功耗、成本等方面。 1)選擇適合的芯片:根據(jù)設計目標選擇適合的芯片,查找Data

110kv變電站設計規(guī)范

110kV變電站設計規(guī)范涉及多個方面,包括選址、電氣設計、設備選擇、安全保護等。以下是根據(jù)相關(guān)規(guī)范和標準整理的一些主要設計規(guī)范: 一、總則 目的與范圍 :規(guī)范適用于電壓為35~110k

pcb設計中有哪些常用設計規(guī)范

在PCB(Printed Circuit Board,印刷電路板)設計中,常用的設計規(guī)范涉及多個方面,以確保電路板的性能、可靠性、可制造性和可維護性。以下是一些主要的設計規(guī)范: 一、電

純干貨!RS485接口電路設計攻略

時為高電平1,小于200mV時為邏輯電平0。一般會在首末兩端接120Ω電阻,其作用是進行阻抗匹配,消除信號反射。

RS485硬件電路設計

RS485電路設計可以分為隔離型和非隔離型,下圖是非隔離型

發(fā)表于 05-27 14:29

干貨!原理圖設計規(guī)范133條checklist

, 版本號;對于重點設計的相關(guān)模擬電路產(chǎn)品,沒有主用芯片、外圍芯片以及芯片與芯片之間的連接方面的問題。所以,元器件的選項尤為重要,對于硬件設計的一些基本原則一定要注意。9、原理圖設計規(guī)范

發(fā)表于 04-01 15:50

干貨 | 電路設計中如何減少ESD?

今天給大家分享的是:在電路設計和PCB設計如何防止ESD損壞設備。

今天給大家分享的是:在電路設計和PCB設計如何防止ESD損壞設備。

在電子行業(yè)中,保護設備免受ESD

發(fā)表于 03-26 18:47

ZTE研發(fā)電路設計準則與規(guī)范

背板輸入信號緩沖器應用下拉電阻和串阻。背板輸入信號緩沖器下拉電阻取10K,串阻取100歐姆。背板輸入信號緩沖器輸入先下拉再經(jīng)過串阻,設計上會具有更大的靈活性。設計中應嚴格遵守產(chǎn)品設計約定。

PCB layout在布線上的設計規(guī)范有哪些?

。 pcb layout設計規(guī)范 一、組件放置 組件在PCB板上的布置方式對電路性能和電路密度產(chǎn)生影響。在組件放置方面,必

華為印制電路板(PCB)設計規(guī)范

電子發(fā)燒友網(wǎng)站提供《華為印制電路板(PCB)設計規(guī)范.pdf》資料免費下載

發(fā)表于 01-02 10:44

?43次下載

中興ZTE內(nèi)部電路設計規(guī)范【硬件干貨】

中興ZTE內(nèi)部電路設計規(guī)范【硬件干貨】

評論