簡介

時鐘是芯片正確高效運行的基礎,正確的時鐘配置是芯片能正確運行的必要條件,其重要性不言而喻。AT32各系列產品的時鐘配置部分可能存在細微的差異和需要注意的事項,本文檔就著重針對各系列的情況來詳細介紹如何結合雅特力提供的V2.x.x的板級支持包(BSP)來配置時鐘。以下介紹時鐘配置的方法主要分兩種:1、以手動編寫代碼調用BSP中提供的驅動函數接口來進行時鐘配置。2、采用時鐘工具來配置并生成相應的源碼文件。

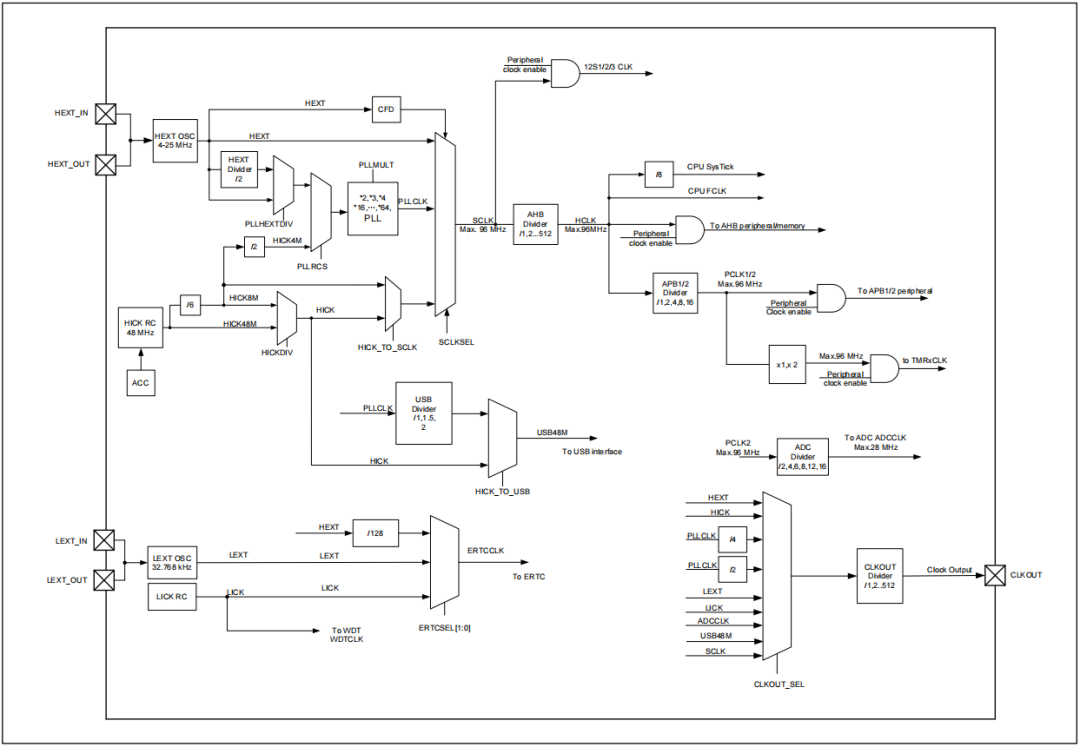

時鐘樹

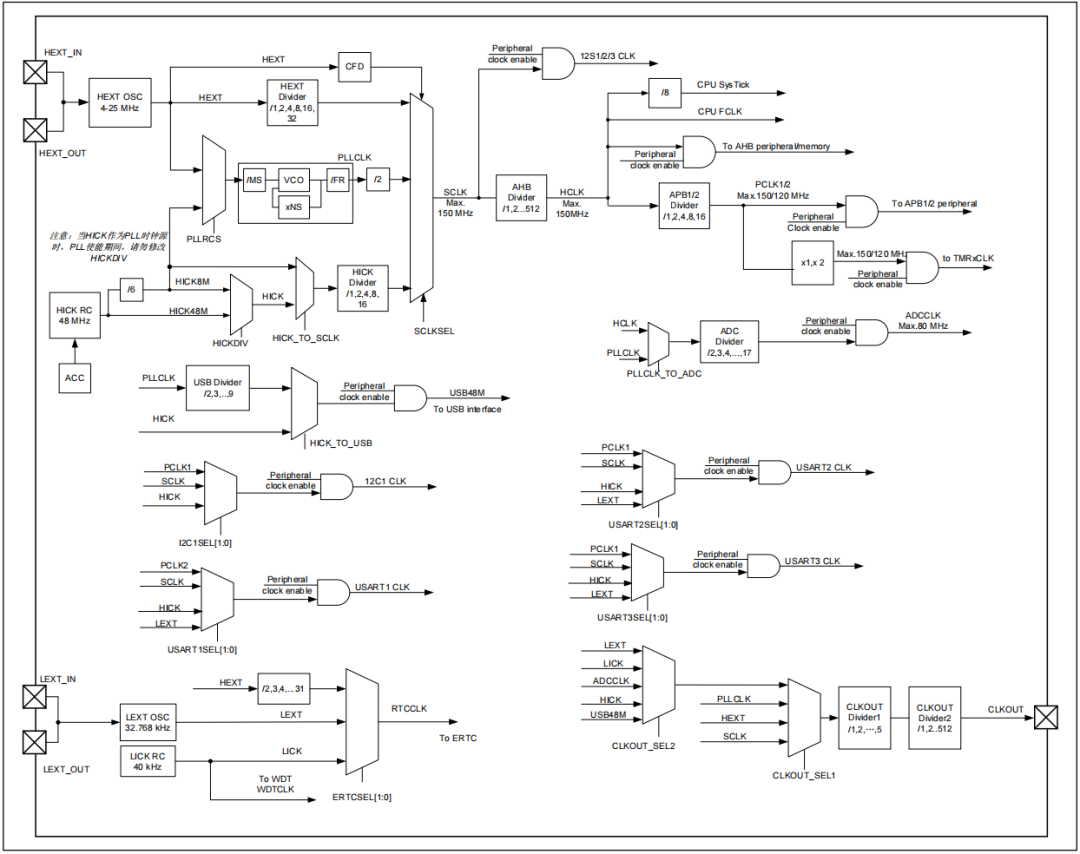

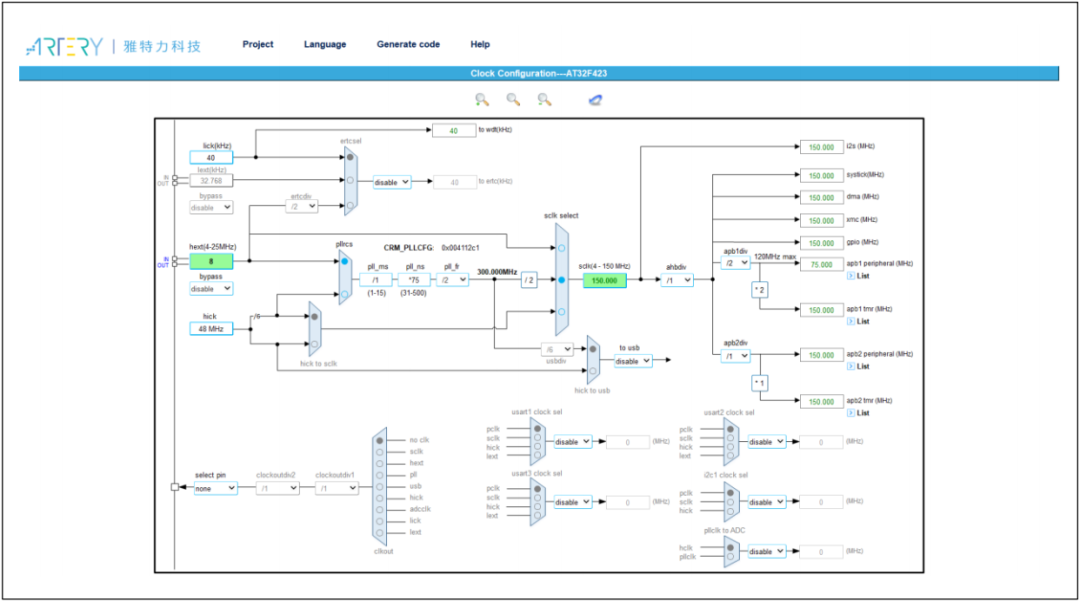

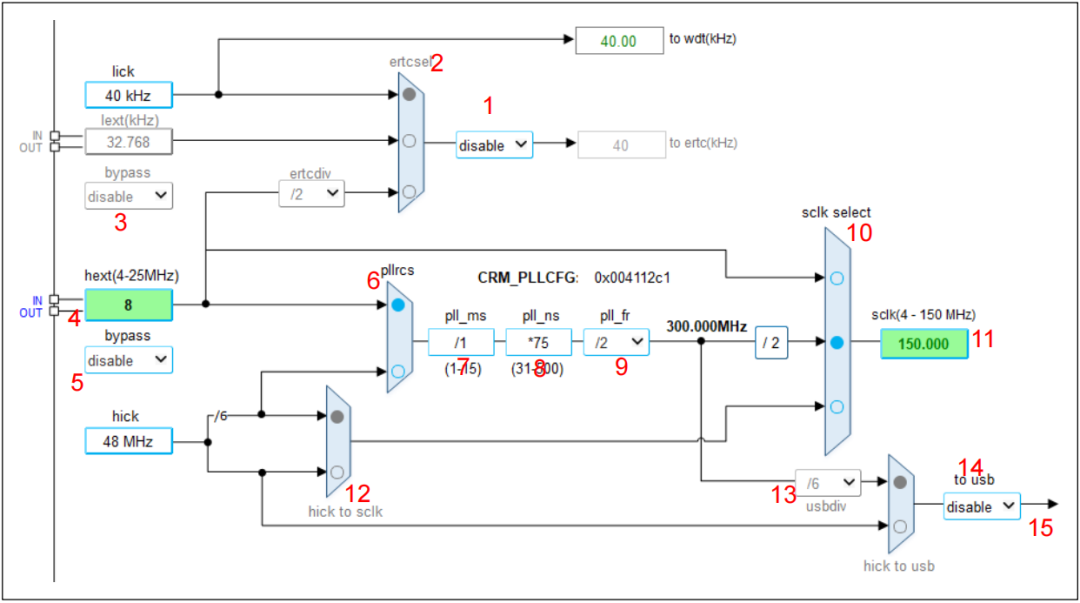

在進行時鐘配置之前,應充分了解對應芯片的時鐘樹結構,這樣在進行時鐘配置時才會游刃有余。對于系統時鐘頻率及路徑的配置我們需要關注時鐘源、倍頻及系統時鐘部分。類似如下圖:圖1. 時鐘框圖 可由圖中得到以下幾個關鍵信息:1) SCLKSEL:系統時鐘可以由HEXT、PLLCLK、HICK三大時鐘源提供。2) HEXT:HEXT是外部高速時鐘,其可以外接范圍是4~25 MHz的晶振或時鐘源。3) HICK:HICK RC是內部高速振蕩器,頻率為48MHz。HICK時鐘由內部振蕩器給出,但在初始情況下由HICKDIV控制并默認6分頻后為8MHz,亦可配置為不分頻,保持48MHz的頻率。4) PLLCLK:PLL時鐘=PLL輸入時鐘/PLL_MS*PLL_NS/PLL_FR。5) PLL輸入時鐘:PLL的輸入時鐘由PLLRCS決定,有兩個來源:HICK 8 MHz和HEXT。

可由圖中得到以下幾個關鍵信息:1) SCLKSEL:系統時鐘可以由HEXT、PLLCLK、HICK三大時鐘源提供。2) HEXT:HEXT是外部高速時鐘,其可以外接范圍是4~25 MHz的晶振或時鐘源。3) HICK:HICK RC是內部高速振蕩器,頻率為48MHz。HICK時鐘由內部振蕩器給出,但在初始情況下由HICKDIV控制并默認6分頻后為8MHz,亦可配置為不分頻,保持48MHz的頻率。4) PLLCLK:PLL時鐘=PLL輸入時鐘/PLL_MS*PLL_NS/PLL_FR。5) PLL輸入時鐘:PLL的輸入時鐘由PLLRCS決定,有兩個來源:HICK 8 MHz和HEXT。

代碼配置解析

以下將以庫函數接口為核心來對時鐘配置流程和方法進行說明。

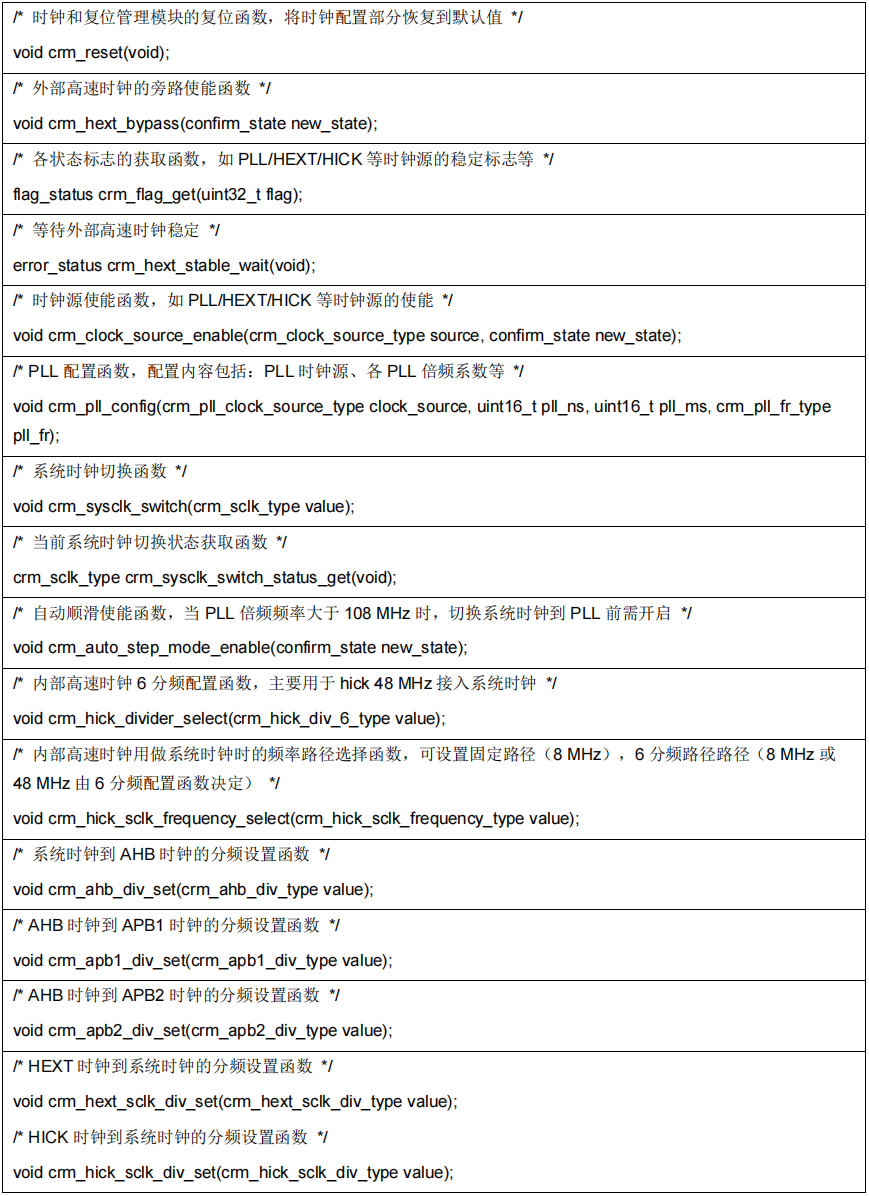

函數接口

各系列產品對應提供的BSP中對硬件的時鐘設置部分已封裝好接口函數以供調用,以下羅列出時鐘配置常用的函數接口,各函數的具體參數及返回值類型等請參考at32f425_crm.c/.h文件。

時鐘配置流程

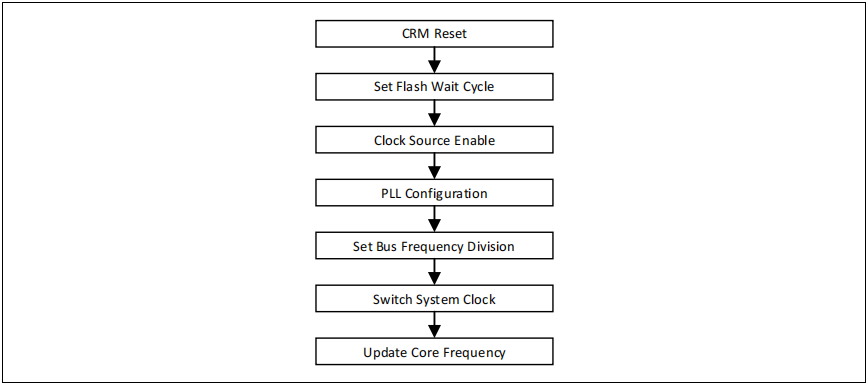

按常規應用來講解時鐘配置流程,其內容可大致分為如下步驟:圖2. 時鐘配置流程圖 一、復位(CRM Reset)首先按規范流程應復位CRM配置參數,其主要是將系統時鐘切換到HICK,其余的系統時鐘配置寄存器寫入默認值,待后續進行新配置參數的寫入。函數調用的代碼實現如下:

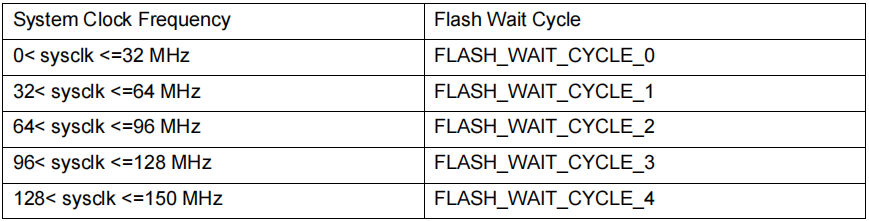

一、復位(CRM Reset)首先按規范流程應復位CRM配置參數,其主要是將系統時鐘切換到HICK,其余的系統時鐘配置寄存器寫入默認值,待后續進行新配置參數的寫入。函數調用的代碼實現如下: 二、Flash 等待周期(Set Flash Wait Cycle)AT32F423片上采用的是嵌入式Flash,當運行在不同的主頻下時需對應設定Flash等待周期。flash等待周期與運行主頻關系如下:

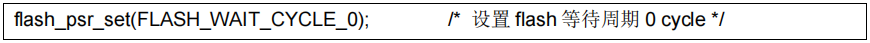

二、Flash 等待周期(Set Flash Wait Cycle)AT32F423片上采用的是嵌入式Flash,當運行在不同的主頻下時需對應設定Flash等待周期。flash等待周期與運行主頻關系如下: 函數調用的代碼實現如下:

函數調用的代碼實現如下:

三、時鐘源配置(Clock Source Configuration)與系統時鐘相關的高速時鐘源主要包括HEXT和HICK,PLL也是使用以上時鐘源來進行倍頻。需要在配置使能PLL前將所使用的PLL參考時鐘源開啟并等待其穩定。

- HEXT

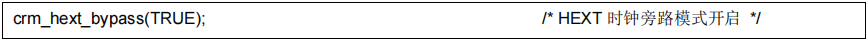

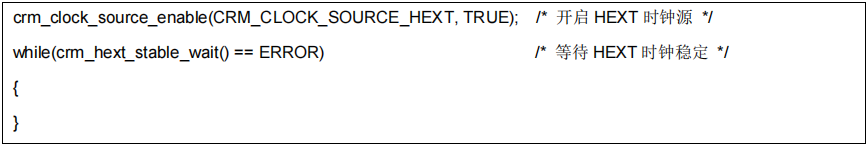

外部高速時鐘如采用外接有源時鐘的方式時,可開啟旁路模式來進行使用,采用晶振時,不能開啟旁路模式,旁路模式應在外部高速時鐘源使能前進行設定,其默認情況為關閉。旁路模式使能代碼實現如下: 使能HEXT時鐘源并等待HEXT時鐘穩定,代碼實現如下:

使能HEXT時鐘源并等待HEXT時鐘穩定,代碼實現如下:

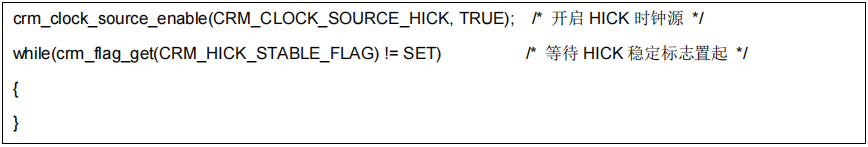

- HICK

內部高速時鐘是由芯片內部振蕩器提供,使能HICK時鐘源并等待HICK時鐘穩定,代碼實現如下: 四、PLL配置(PLL Configuration)PLL配置主要包括:PLL時鐘源、PLL倍頻系數、PLL倍頻頻率范圍等的設置。倍頻時鐘公式為:PLLCLK=(PLL輸入時鐘*PLL_NS)/(PLL_MS*PLL_FR)。

四、PLL配置(PLL Configuration)PLL配置主要包括:PLL時鐘源、PLL倍頻系數、PLL倍頻頻率范圍等的設置。倍頻時鐘公式為:PLLCLK=(PLL輸入時鐘*PLL_NS)/(PLL_MS*PLL_FR)。

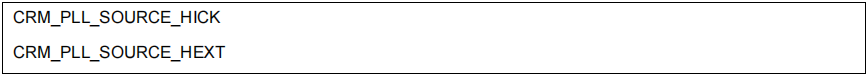

- PLL時鐘源

PLL時鐘源細分有如下來源:1、HICK(8MHz),2、HEXT。PLL時鐘源應在PLL配置使能前開啟并等待穩定。以上PLL時鐘源在crm_pll_config函數中對應的參數定義如下:

- PLL倍頻系數

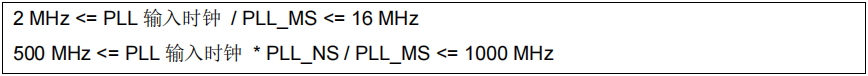

PLL_MS:PLL預分頻系數,范圍值1~15。其功能是對PLL輸入時鐘進行預分頻。PLL_NS:PLL倍頻參數,范圍值31~500。其功能是對PLL_MS進行預分頻處理后的時鐘進行倍頻。PLL_FR:PLL后分頻系數,范圍(1、2、4、8、16、32)。其功能是對PLL_NS倍頻后的時鐘進行后除頻,除頻后的時鐘才是PLL時鐘。以上參數在搭配使用時有如下限制條件,詳情可參考RM的時鐘源章節:

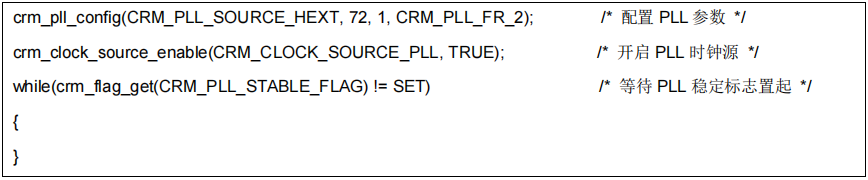

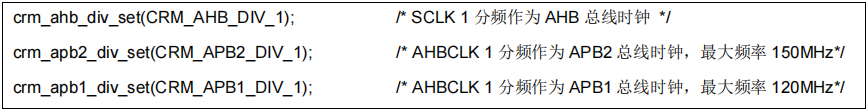

當PLL參數設置完成后,即可開啟PLL并等待PLL穩定。示例:外部時鐘晶振8MHz,采用HEXT時鐘作為PLL時鐘源,PLLCLK倍頻到288MHz的代碼實現如下: 五、總線分頻(Set Bus Frequency Division)總線分頻包含SCLK到AHBCLK分頻、AHBCLK到APB1CLK分頻、AHBCLK到APB2CLK分頻。AHB總線1分頻、APB1/APB2總線1分頻的代碼實現如下:

五、總線分頻(Set Bus Frequency Division)總線分頻包含SCLK到AHBCLK分頻、AHBCLK到APB1CLK分頻、AHBCLK到APB2CLK分頻。AHB總線1分頻、APB1/APB2總線1分頻的代碼實現如下: 注:APB2CLK的最大頻率為150MHz,APB1CLK的最大頻率為120MHz。六、切換系統時鐘(Switch System Clock)系統時鐘來源主要有三個:HICK、HEXT、PLLCLK。在切換系統時鐘到如上時鐘源時應提前確保對應時鐘源已穩定。

注:APB2CLK的最大頻率為150MHz,APB1CLK的最大頻率為120MHz。六、切換系統時鐘(Switch System Clock)系統時鐘來源主要有三個:HICK、HEXT、PLLCLK。在切換系統時鐘到如上時鐘源時應提前確保對應時鐘源已穩定。

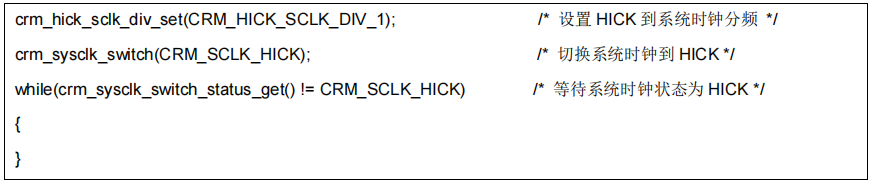

- HICK系統時鐘

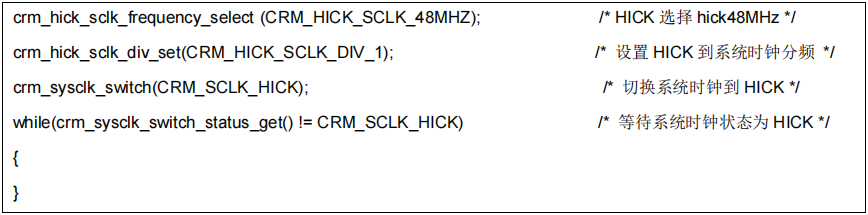

內部高速時鐘在系統復位重新運行時默認作為系統時鐘,后期代碼進行設定時,可有兩種頻率值來進行設定(8MHz和48MHz)。如圖1所述HICK默認情況下用的是8MHz,可配置為48MHz。HICK 8 MHz用作系統時鐘的代碼實現如下: HICK 48 MHz用作系統時鐘的代碼實現如下:

HICK 48 MHz用作系統時鐘的代碼實現如下:

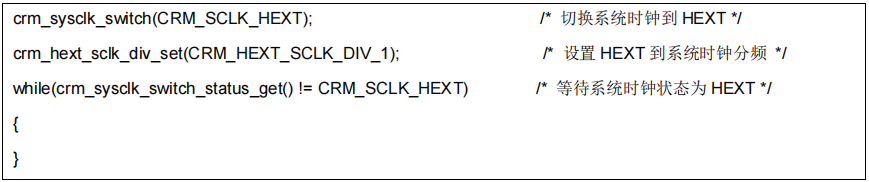

- HEXT系統時鐘

外部高速時鐘用作系統時鐘時,其系統時鐘頻率以實際使用的外部時鐘頻率為準,范圍為4~25 MHz。HEXT用作系統時鐘的代碼實現如下:

- PLLCLK系統時鐘

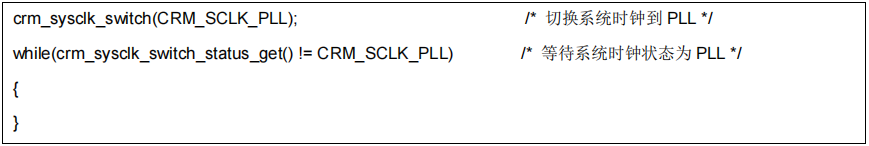

PLLCLK用作系統時鐘時,系統時鐘頻率=PLLCLK/2,頻率值以實際的PLL倍頻結果為準。其最高頻率應滿足芯片規格為基礎。PLLCLK用作系統時鐘的代碼實現如下: 七、更新核心頻率(Update Core Frequency)提供的BSP中,其代碼框架內保留了一個表示系統核心頻率的參數值system_core_clock,其保存的是CPU核心的運行頻率值,應該在每次系統時鐘配置完成后來進行更新。為的是在整個代碼框架下,各外設驅動的頻率配置能很快獲取到當前核心運行頻率值并使用。代碼實現如下:

七、更新核心頻率(Update Core Frequency)提供的BSP中,其代碼框架內保留了一個表示系統核心頻率的參數值system_core_clock,其保存的是CPU核心的運行頻率值,應該在每次系統時鐘配置完成后來進行更新。為的是在整個代碼框架下,各外設驅動的頻率配置能很快獲取到當前核心運行頻率值并使用。代碼實現如下:

時鐘配置示例

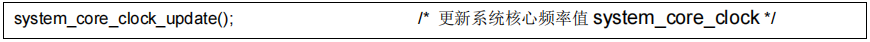

以下將以完整的時鐘配置流程來進行說明,示例:由8MHz外部時鐘晶振作為時鐘源,經PLL倍頻后,144MHz用做系統時鐘,AHB不分頻,APB2采用1分頻,APB1采用2分頻。函數system_clock_config代碼實現如下:

時鐘工具

時鐘配置工具是雅特力科技為方便對AT32系列MCU進行時鐘配置而開發的一個圖形化配置工具,其主旨是使用戶清晰了解時鐘路徑和配置出期望的時鐘頻率并生成源碼文件。

環境要求

- 軟件要求

需要Windows7及以上操作系統支持。

安裝

- 軟件安裝

本軟件不需要安裝,只需直接運行可執行程序AT32_New_Clock_Configuration.exe。

功能介紹

本章節將介紹此工具的基本操作,其主要的啟動界面和配置界面如下所示圖3. 啟動界面 圖4. 配置界面

圖4. 配置界面

菜單欄

菜單欄內容如圖所示:圖5. 菜單欄

- “項目”(Project)菜單:

新建:新建時鐘配置項目

打開:打開已存在的配置項目

保存:保存已打開的配置項目

- “語言”(Language)菜單:

English:選擇English作為顯示語言

簡體中文:選擇簡體中文作為顯示語言

- “生成代碼”(General code)菜單:

當在對應型號的操作配置界面將所期望的時鐘路徑和時鐘頻率配置完成之后,可點擊“生成代碼”菜單來選擇源碼文件的存儲路徑并生成相應的源碼文件。

- “幫助”(Help)菜單:

新版本下載:聯網進行新版本下載版本:查看當前版本

新建配置項目

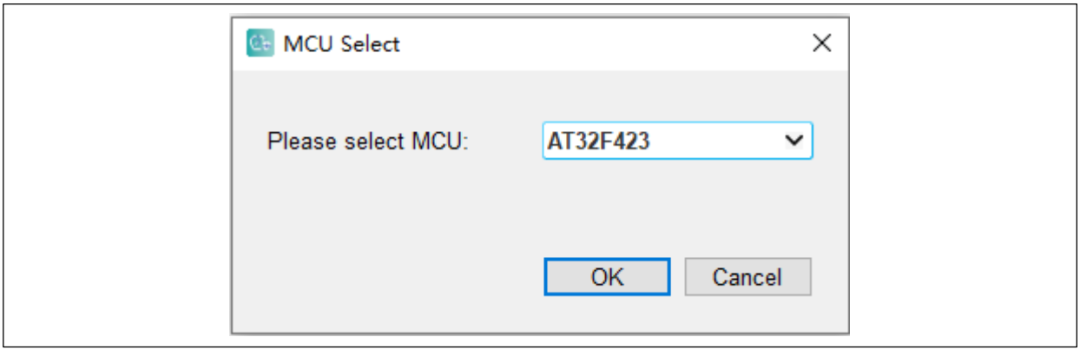

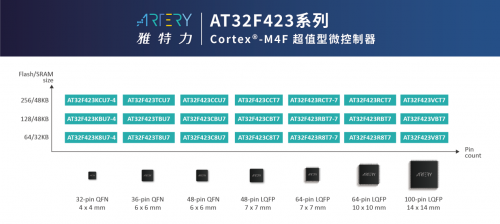

雙擊打開時鐘配置工具,可看到圖示的啟動界面,可點擊“項目”菜單-->“新建”,進行配置項目的新建,在新建配置項目的過程中需要對芯片的系列所屬進行選擇,操作方法如下圖所示圖6. MCU選擇界面 MCU系列的選擇,可點擊下拉框來進行選擇,當選擇好MCU后點擊“確定”可進入到時鐘配置界面。

MCU系列的選擇,可點擊下拉框來進行選擇,當選擇好MCU后點擊“確定”可進入到時鐘配置界面。

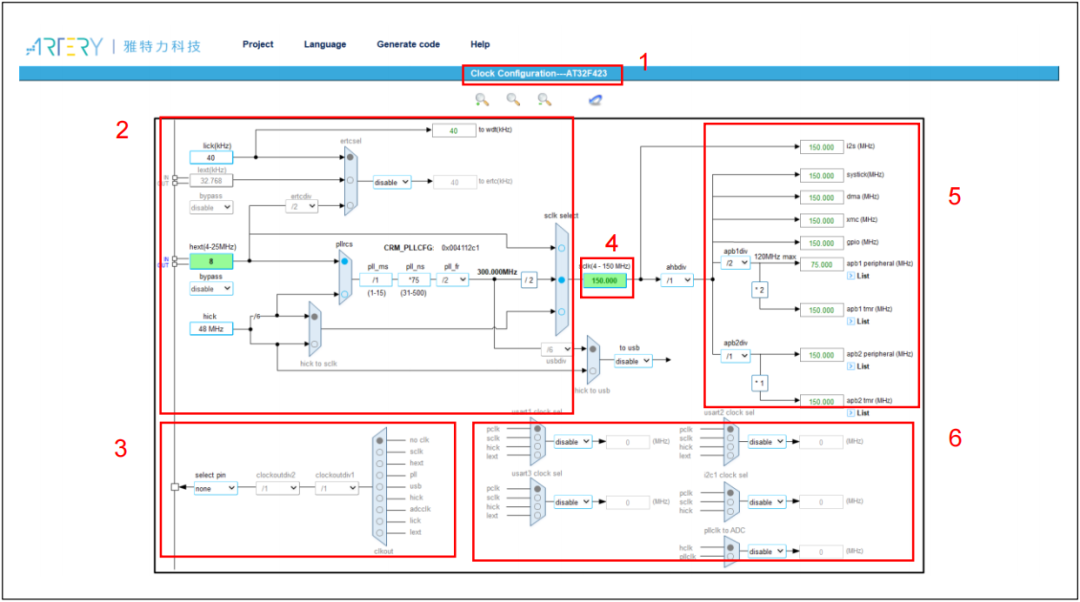

配置界面的使用

配置界面主要用來進行時鐘路徑及參數的配置,以下的介紹將以AT32F425系列作為示例來展開進行,其余系列的配置方法與此類似。整個配置界面主要可以分為四個大塊,如下圖所示圖7. 配置界面框架 1. 標題部分:用于展示當前配置項目所選擇的MCU系列。2. 配置部分:用于對時鐘路徑和時鐘參數進行選擇和配置,以達到期望的應用需求。3. 輸出部分:用于時鐘輸出(CLKOUT)的配置。4. 在SCLK欄也可在選中PLL為系統時鐘時作為輸入框,可輸入期望的系統時鐘頻率來反向自動配置出倍頻參數。5. 結果部分:用于顯示當前外設所使用的時鐘頻率及總線上的外設。6. 時鐘源配置部分:用于對擁有獨立時鐘源的外設進行時鐘源的設置。接下來就著重介紹一下配置部分的使用。配置部分的流程界面是對應著MCU時鐘樹來進行的,各系列MCU的此部分可能存在著差異,但使用方式大同小異。時鐘路徑的配置可按流程對各開關進行點選來進行選擇,配置部分如下圖所示,將逐個流程點的功能及其注意事項進行介紹。圖8. 時鐘配置框

1. 標題部分:用于展示當前配置項目所選擇的MCU系列。2. 配置部分:用于對時鐘路徑和時鐘參數進行選擇和配置,以達到期望的應用需求。3. 輸出部分:用于時鐘輸出(CLKOUT)的配置。4. 在SCLK欄也可在選中PLL為系統時鐘時作為輸入框,可輸入期望的系統時鐘頻率來反向自動配置出倍頻參數。5. 結果部分:用于顯示當前外設所使用的時鐘頻率及總線上的外設。6. 時鐘源配置部分:用于對擁有獨立時鐘源的外設進行時鐘源的設置。接下來就著重介紹一下配置部分的使用。配置部分的流程界面是對應著MCU時鐘樹來進行的,各系列MCU的此部分可能存在著差異,但使用方式大同小異。時鐘路徑的配置可按流程對各開關進行點選來進行選擇,配置部分如下圖所示,將逐個流程點的功能及其注意事項進行介紹。圖8. 時鐘配置框 1. ertc使能:ertc時鐘代碼配置的使能下拉框。2. ertcsel:點選框,ertc時鐘源選擇。當ertc使能開啟后,此點選框可配置。3. lext bypass:外部低速時鐘的旁路使能。4. hext:此為輸入框,8MHz為所采用外部時鐘源的默認頻率,用戶可根據實際使用的外部時鐘源頻率進行修改。(注:此8MHz被修改為其他頻率值時,對應的BSP中demo目錄下的inc/at32f423_conf.h文件內的HEXT_VALUE宏定義也應該一致修改,也可以采用工具生成的at32f423_conf.h文件來進行使用)。5. hext bypass:高速外部時鐘的旁路使能。6. pllrcs:點選框,可配置PLL時鐘源為HEXT或HICK。7. pll_ms:輸入框,PLL預分頻系數,范圍值1~15。其功能是對PLL輸入時鐘進行預分頻。8. pll_ns:輸入框,PLL倍頻參數,范圍值31~500。其功能是對PLL_MS進行預分頻處理后的時鐘進行倍頻。9. pll_fr:下拉框,PLL后分頻系數,范圍(1、2、4、8、16、32)。其功能是對PLL_NS倍頻后的時鐘進行后除頻,除頻后的時鐘才是PLL時鐘。10. sclk select:點選框,可配置HEXT、PLL或HICK作為系統時鐘。11. sclk頻率:當采用正向配置時,此作為系統時鐘頻率的配置結果顯示,當將其用作輸入框時,輸入期望的頻率后點擊回車鍵,會根據此輸入值反向計算一組合適的或最接近期望值的PLL配置參數。12. hick to sclk:點選框,當sclk select選擇HICK作為系統時鐘時,可配置HICK的8MHz或48MHz到系統時鐘(注:當選擇48 MHz HICK到系統時鐘后,CLKOUT輸出HICK時的頻率也為48MHz)。13. usbdiv:下拉框。當PLL時鐘被選作為USB的時鐘來源時,此處配置PLL時鐘到USB時鐘的分頻系數。14. USB使能:USB時鐘代碼配置的使能下拉框。15. USB時鐘頻率的顯示。此顯示欄會實時計算USB時鐘的頻率并顯示,如果配置出來的USB時鐘不等于48MHz時,顯示出來的USB時鐘頻率會標注為紅色,而實際應用中沒有用到USB時選擇disable則不會顯示。(注:此部分只針對USB時鐘頻率的配置,USB外設時鐘使能需自行額外打開)

1. ertc使能:ertc時鐘代碼配置的使能下拉框。2. ertcsel:點選框,ertc時鐘源選擇。當ertc使能開啟后,此點選框可配置。3. lext bypass:外部低速時鐘的旁路使能。4. hext:此為輸入框,8MHz為所采用外部時鐘源的默認頻率,用戶可根據實際使用的外部時鐘源頻率進行修改。(注:此8MHz被修改為其他頻率值時,對應的BSP中demo目錄下的inc/at32f423_conf.h文件內的HEXT_VALUE宏定義也應該一致修改,也可以采用工具生成的at32f423_conf.h文件來進行使用)。5. hext bypass:高速外部時鐘的旁路使能。6. pllrcs:點選框,可配置PLL時鐘源為HEXT或HICK。7. pll_ms:輸入框,PLL預分頻系數,范圍值1~15。其功能是對PLL輸入時鐘進行預分頻。8. pll_ns:輸入框,PLL倍頻參數,范圍值31~500。其功能是對PLL_MS進行預分頻處理后的時鐘進行倍頻。9. pll_fr:下拉框,PLL后分頻系數,范圍(1、2、4、8、16、32)。其功能是對PLL_NS倍頻后的時鐘進行后除頻,除頻后的時鐘才是PLL時鐘。10. sclk select:點選框,可配置HEXT、PLL或HICK作為系統時鐘。11. sclk頻率:當采用正向配置時,此作為系統時鐘頻率的配置結果顯示,當將其用作輸入框時,輸入期望的頻率后點擊回車鍵,會根據此輸入值反向計算一組合適的或最接近期望值的PLL配置參數。12. hick to sclk:點選框,當sclk select選擇HICK作為系統時鐘時,可配置HICK的8MHz或48MHz到系統時鐘(注:當選擇48 MHz HICK到系統時鐘后,CLKOUT輸出HICK時的頻率也為48MHz)。13. usbdiv:下拉框。當PLL時鐘被選作為USB的時鐘來源時,此處配置PLL時鐘到USB時鐘的分頻系數。14. USB使能:USB時鐘代碼配置的使能下拉框。15. USB時鐘頻率的顯示。此顯示欄會實時計算USB時鐘的頻率并顯示,如果配置出來的USB時鐘不等于48MHz時,顯示出來的USB時鐘頻率會標注為紅色,而實際應用中沒有用到USB時選擇disable則不會顯示。(注:此部分只針對USB時鐘頻率的配置,USB外設時鐘使能需自行額外打開)

生成代碼

當時鐘配置完成后,可點擊生成代碼,然后選擇代碼生成的路徑并確認,最后會在所選目錄下生成兩個文件夾inc和src,源文件存放在src文件夾下,頭文件存放在inc文件夾下。這些文件可結合到BSP_V2.x.x內的工程來進行使用。可以采用新生成的時鐘代碼文件(at32f4xx_clock.c/at32f4xx_clock.h/at32f4xx_conf.h)將原BSPdemo中的對應文件替換,在main函數中進行system_clock_config函數調用即可。

注意事項

外部時鐘源(HEXT)修改

因本文檔所示例的demo和配置工具都默認采用的8MHz外部時鐘頻率,當實際硬件使用的外部時鐘源是非8MHz頻率時需注意以下幾點。

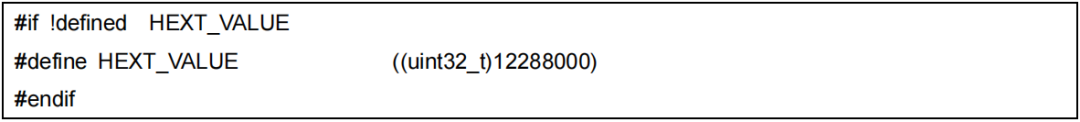

- 代碼修改

1、以實際的外部時鐘頻率按文中時鐘配置流程章節所描述的時鐘配置流程及方法來編寫相應的代碼,配置出期望的時鐘配置及時鐘路徑。2、修改對應demo工程中at32f4xx_conf.h文件的HEXT_VALUE值,以實際使用的外部時鐘源頻率值來進行修改。如實際外部高速時鐘使用12.288MHz的晶振或時鐘源時,at32f4xx_conf.h文件應修改如下:

- 工具修改

1、在時鐘配置工具中的HEXT輸入框內填入外部時鐘源實際頻率值并按“Enter”鍵確認。2、配置好所需的時鐘路徑及時鐘頻率,生成代碼。采用新生成的時鐘代碼文件(at32f4xx_clock.c/at32f4xx_clock.h/at32f4xx_conf.h)將原BSP demo中的對應文件替換或取其中函數內容進行替換,在main函數中進行system_clock_config函數調用即可。

工具使用

在使用本時鐘配置工具時需注意:1. 此工具生成的時鐘配置源碼文件需結合雅特力科技提供的BSP_V2.x.x進行使用。2. 不同系列所生成的時鐘配置源碼文件不能型號混用,只能在相對應的工程項目中進行調用。3. 配置工具中各輸入框參數修改后,請以“Enter”鍵結束。

-

芯片

+關注

關注

453文章

50387瀏覽量

421783 -

時鐘配置

+關注

關注

1文章

14瀏覽量

8618 -

雅特力

+關注

關注

0文章

156瀏覽量

7974

發布評論請先 登錄

相關推薦

雅特力正式推出AT32F423系列超值型Cortex-M4F MCU

雅特力發布超值型AT32F423系列MCU,以高性價比搶攻高性能應用市場

雅特力發布超值型AT32F423系列MCU,以高性價比搶攻高性能應用市場

雅特力推出AT32F423系列超值型Cortex-M4F MCU

重磅!雅特力發布全新超值型AT32F423系列MCU,以高性價比搶攻高性能應用市場

直播預告|雅特力超值型AT32F423新品發布,多管腳高性能滿足多元市場需求

雅特力AT32F423 GPIO使用指南

雅特力AT32F423安全庫應用筆記

雅特力AT32F423時鐘配置

雅特力AT32F423時鐘配置

評論