一、什么是芯片封裝?

芯片封裝作為設(shè)計和制造電子產(chǎn)品開發(fā)過程中的關(guān)鍵技術(shù)之一日益受到半導(dǎo)體行業(yè)的關(guān)注和重視。封裝的作用主要有保護電路免受外界環(huán)境的影響、避免噪聲信號的污染,屏蔽外場的串擾,支撐封裝體內(nèi)機械機構(gòu)、電氣互連,緩解封裝體內(nèi)部的機械應(yīng)力,提供從封裝體內(nèi)功率器件到外界環(huán)境的熱傳遞路徑,使芯片間的引線從封裝體牢固地引出而非直接裝配在基片上等功能。封裝技術(shù)的優(yōu)劣直接關(guān)系到芯片自身性能的發(fā)揮以及與芯片連接的PCB(印制電路板)的設(shè)計和制備,因此封裝是至關(guān)重要的。

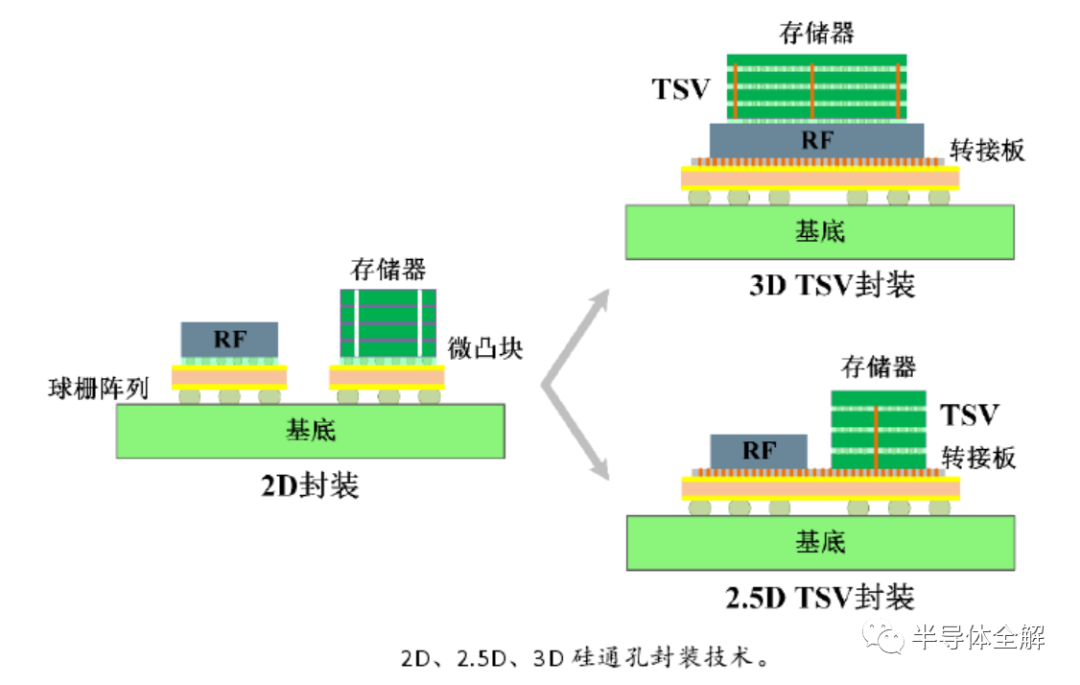

高密度封裝應(yīng)半導(dǎo)體技術(shù)的發(fā)展,實現(xiàn)電子器件由二維(2D)平面堆集到沿Z方向的高密度集成,以緩解、延續(xù)或超越摩爾定律的發(fā)展。

二、摩爾定律及后摩爾時代

1965年,美國仙童半導(dǎo)體公司的Gordon Moore博士提出了著名的Moore定律:當價格不變時,集成電路上可容納的元器件數(shù)目,每隔18-24個月就會增加一倍。

這一定律準確預(yù)測了過去五十年半導(dǎo)體行業(yè)的發(fā)展。隨著電子信息產(chǎn)業(yè)的不斷升級,半導(dǎo)體集成電路正在向超大規(guī)模、超高速、高密度、大功率方向發(fā)展,當晶體管特征尺寸達到納米級后,進一步減小晶體管尺寸無疑是困難且昂貴的,這也意味著摩爾定律接近尾聲。

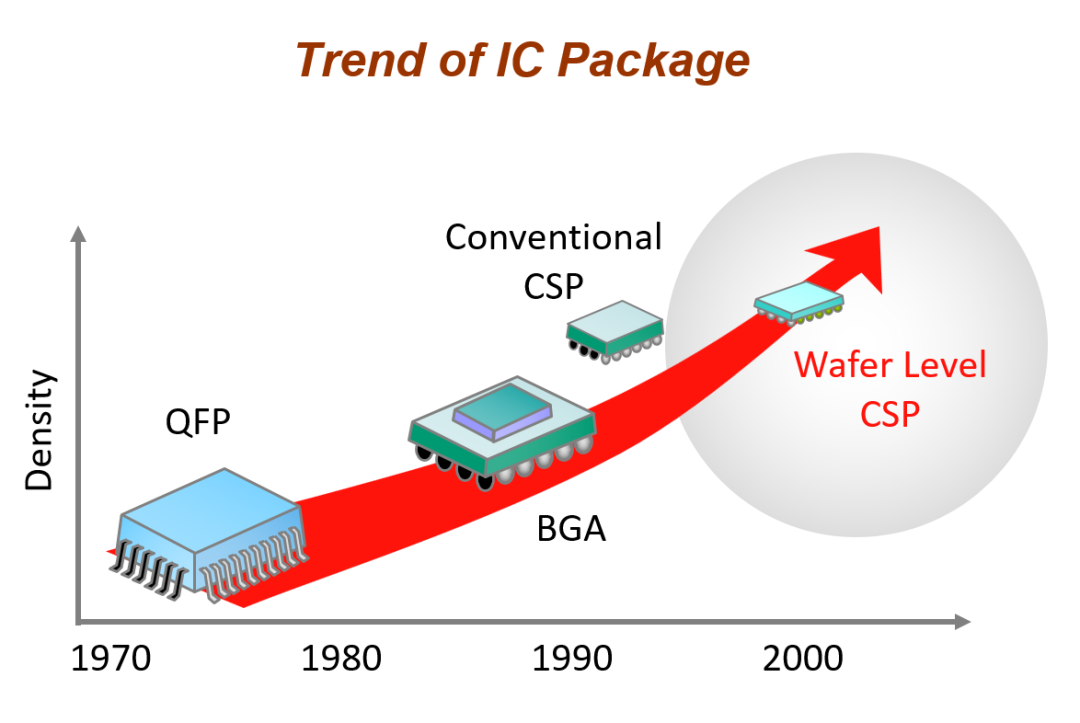

基于這種情況,業(yè)界提出了超越摩爾定律(More-Than-Moore,MTM),試圖從其它的一些途徑來延續(xù)摩爾定律的發(fā)展趨勢,并且從摩爾定律的“更多更快”,發(fā)展到MTM的“更好更全面”。如通過優(yōu)化晶體管的設(shè)計,尋找硅的替代品和發(fā)展先進封裝技術(shù)等,使一塊集成電路芯片能夠同時具有多種功能,這不僅可以降低芯片的生產(chǎn)成本還能提高電路的等效集成度。其中先進封裝技術(shù)的應(yīng)用無疑是后摩爾時代集成電路發(fā)展最有效的解決方法之一,特別是電子封裝維度從二維(2D)向三維(3D)發(fā)展,通過三維片上集成、硅通孔(TSV)芯片互連和三維封裝堆疊的形式,在晶體管特征尺寸不變的情況下,可以成倍的增加集成電路密度,從而更好的延續(xù)摩爾定律。

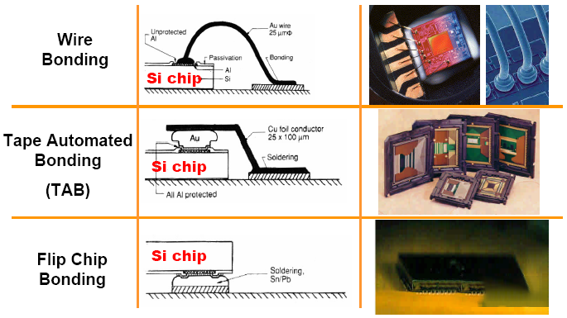

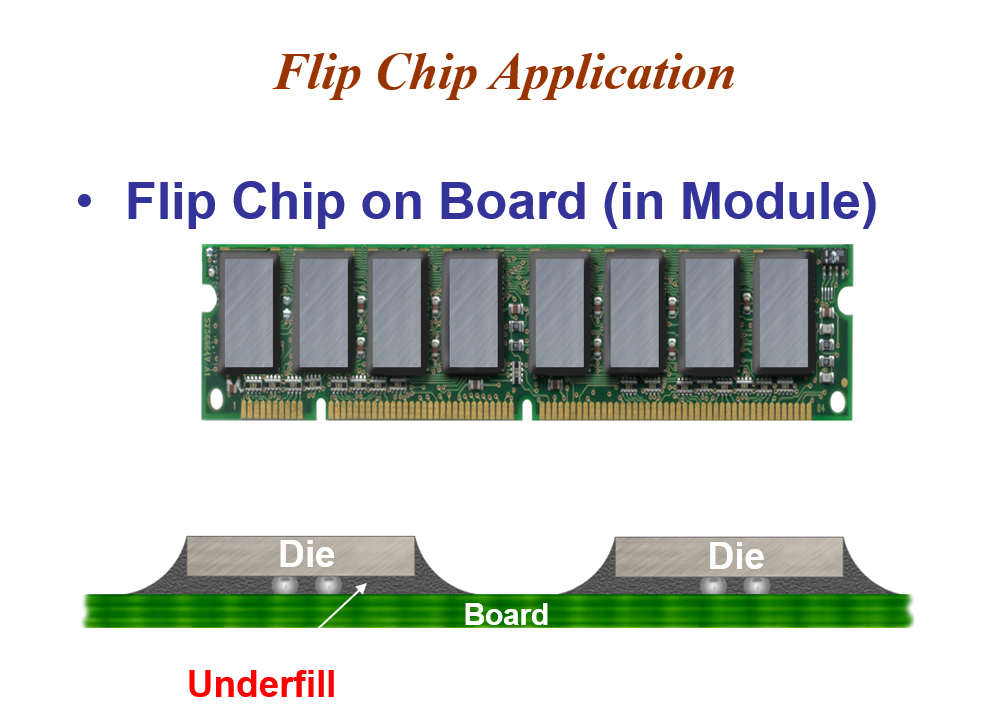

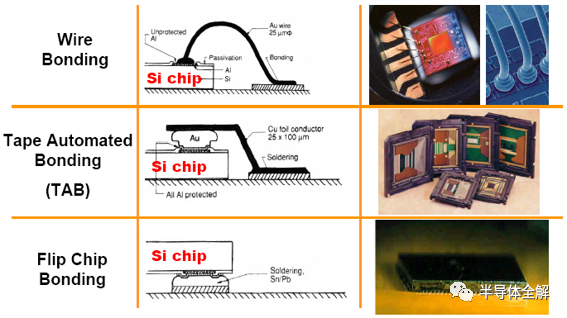

封裝的結(jié)構(gòu)方式包括引線鍵合(wire bonding,WB)、載帶自動鍵合(Tape Automated Bonding)、倒裝芯片(flip chip,FC)、硅通孔技術(shù)(Through Silicon Via)等。

?

?

三、倒裝芯片(FC)底部填充的原因

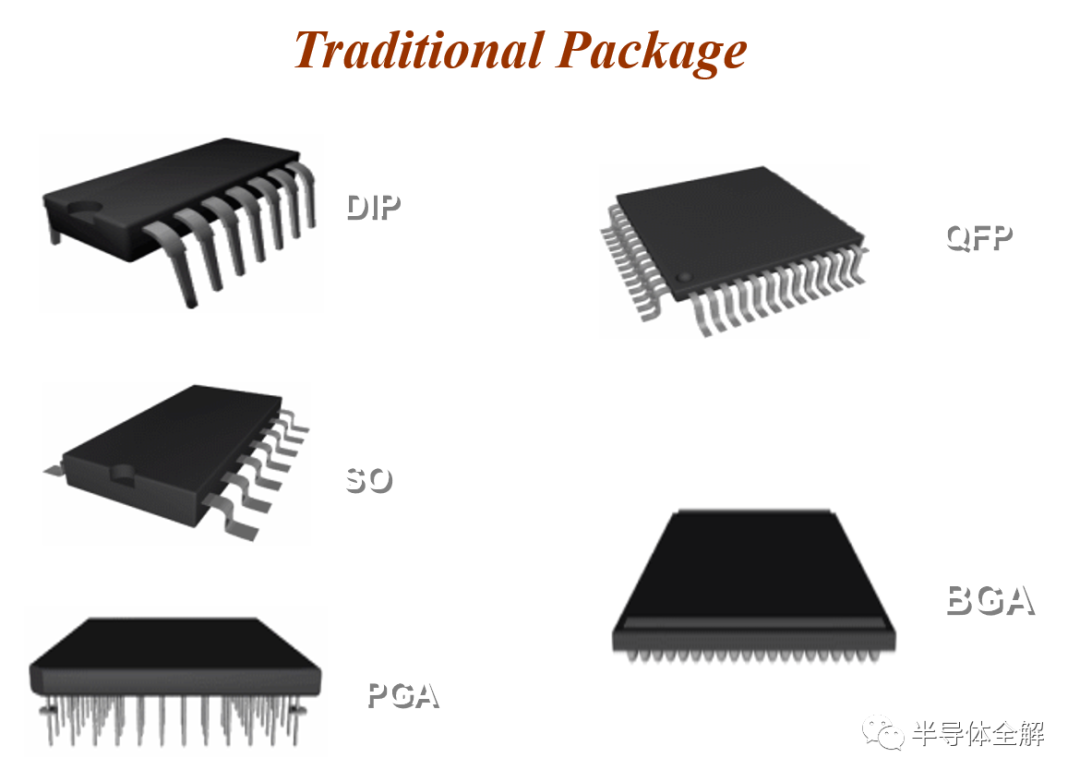

電子封裝結(jié)構(gòu)也由雙列直插式封裝(Dualin-line package, DIP)、小外型封裝(Small out-line package, SOP)、四側(cè)引腳扁平封裝(Quad flat package, QFP)等傳統(tǒng)封裝形式向倒裝芯片(Flip-chip, FC)、倒裝芯片-球柵陣列(FC-BGA)、扇入型晶圓級封裝(Fan-inwafer level package, FIWLP)、扇出型晶圓級封裝(Fan-out wafer level package, FOWLP)、嵌入式芯片封裝(Embedded chip package, ECP)等先進封裝形式發(fā)展。其中由FC與BGA技術(shù)融合而產(chǎn)生的FC-BGA封裝已成為廣泛采用的主流封裝技術(shù)之一。

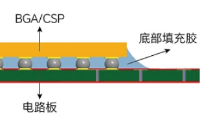

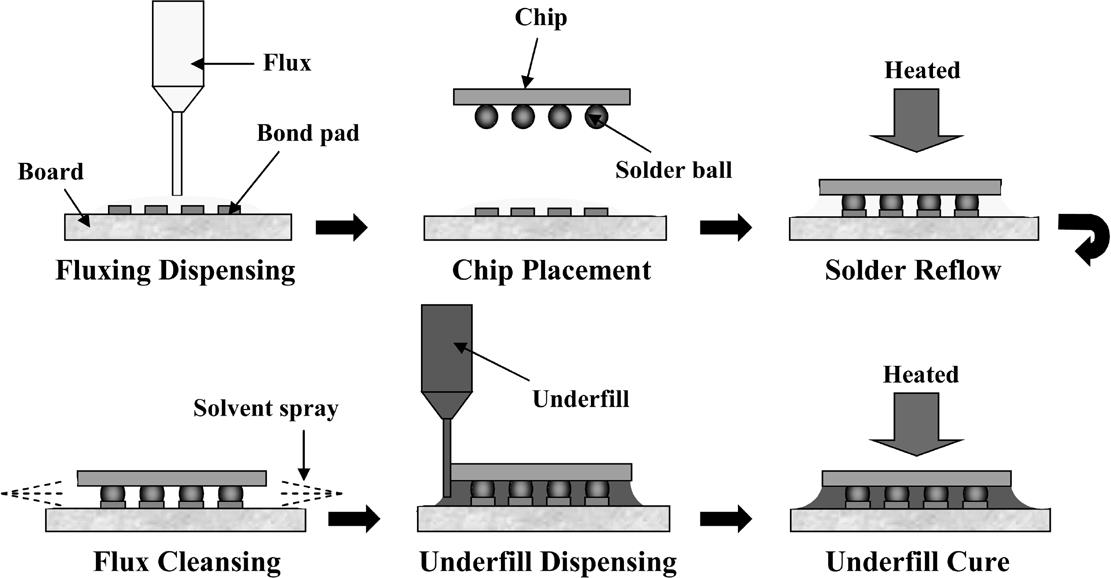

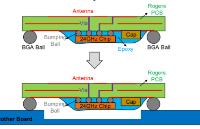

但FC封裝中硅基芯片與高分子基封裝基板之間熱膨脹系數(shù)(Coefficient of Thermal Expansion, CTE)不匹配產(chǎn)生的熱應(yīng)力易造成焊點在熱載荷作用下過早產(chǎn)生疲勞斷裂乃至失效。1987年日本日立(Hitachi)公司Nakano首次提出在環(huán)氧樹脂中加入SiO2并將其填充在芯片與基板之間來提高焊點的疲勞壽命,這種填充樹脂后來逐漸發(fā)展成為底部填充膠(Underfill),也稱為底部填充劑或底填膠等。

審核編輯:劉清

-

集成電路

+關(guān)注

關(guān)注

5367文章

11168瀏覽量

358428 -

PCB板

+關(guān)注

關(guān)注

27文章

1418瀏覽量

51235 -

芯片封裝

+關(guān)注

關(guān)注

11文章

453瀏覽量

30390 -

TSV

+關(guān)注

關(guān)注

4文章

105瀏覽量

81373 -

硅通孔

+關(guān)注

關(guān)注

2文章

21瀏覽量

11817

原文標題:一文了解芯片封裝及底部填充(Underfill)技術(shù)(上)

文章出處:【微信號:閃德半導(dǎo)體,微信公眾號:閃德半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是芯片封裝?倒裝芯片(FC)底部填充的原因

芯片封裝及底部填充(Underfill)技術(shù)詳解

【先進封裝】Underfill的基本特性

underfill底部填充工藝用膠解決方案

光電傳感器WL-CSP封裝芯片底部填充膠應(yīng)用

漢思HS700系列underfill膠水芯片底部填充膠

芯片封裝膠underfill底部填充膠點膠工藝基本操作流程

一文了解芯片封裝及底部填充(Underfill)技術(shù)(上)

一文了解芯片封裝及底部填充(Underfill)技術(shù)(上)

評論