摘要:

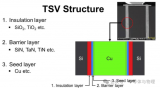

以硅通孔(TSV)為核心的2.5D/3D封裝技術可以實現芯片之間的高速、低功耗和高帶寬的信號傳輸。常見的垂直TSV的制造工藝復雜,容易造成填充缺陷。錐形TSV的側壁傾斜,開口較大,有利于膜層沉積和銅電鍍填充,可降低工藝難度和提高填充質量。在相對易于實現的刻蝕條件下制備了錐形TSV,并通過增加第二步刻蝕來改善錐形TSV形貌。成功制備了直徑為10~40μm、孔口為喇叭形的錐形TSV。通過濺射膜層和銅電鍍填充,成功實現了直徑為15μm、深度為60μm的錐形TSV的連續膜層沉積和完全填充,驗證了兩步刻蝕工藝的可行性和錐形TSV在提高膜層質量和填充效果方面的優勢。為未來高密度封裝領域提供了一種新的TSV制備工藝,在降低成本的同時提高了2.5D/3D封裝技術的性能。

0引言

微電子技術的飛速發展促進了現代集成電路在高性能、低成本和低功耗方面的突破。然而,微電子封裝技術的發展相對滯后,逐漸成為制約半導體技術進一步提升的主要瓶頸。以硅通孔(TSV)為核心的2.5D/3D封裝技術是一種新型的高密度封裝技術,通過在硅基底上形成垂直方向的通孔,并用金屬材料填充,實現了芯片之間的立體互聯,被認為是未來高密度封裝領域的主導技術。TSV封裝技術具有顯著的優勢,如縮減了芯片尺寸、提高了集成度、降低了信號傳輸延時和功耗、提升了數據傳輸速率和帶寬等。

常規的TSV是采用基于等離子刻蝕、循環交替刻蝕/鈍化過程的博世(BOSCH)工藝來刻蝕制備的,所得通孔側邊垂直度接近90°。該垂直圓柱形通孔有利于提升通孔的數量和密度。但是BOSCH工藝的循環刻蝕過程會造成側壁呈扇貝狀,導致后續沉積的膜層厚度不均勻。此外,垂直側壁也增加了后續電介質絕緣層、阻擋層和銅種子層的沉積難度,難以實現良好的階梯覆蓋。膜層沉積時往往只能在TSV開口處形成較厚的膜層,而在TSV較深處的側壁和底部很難進行沉積。這種厚度差異會影響TSV的電鍍填充效果,導致孔口過度填充,孔底出現空缺[1]。同時,由于電鍍液中的Cu 2+在TSV開口處補充的速率遠高于TSV孔深處補充的速率,從而加劇了孔口和孔底部的沉積速率的不一致,進一步導致了填充缺陷的產生。

為了解決這些問題,可以采用錐形TSV的結構。錐形TSV消除了側壁上的扇貝狀結構,并且具有傾斜的側壁,可以顯著提高絕緣層、阻擋層和銅種子層的均勻性和階梯覆蓋性能[2]。電鍍過程中,其較大的開口也有利于電鍍液中的Cu 2+在孔深處的快速補充,從而提高孔內部的電鍍填充效率。因此,通過同時改善膜層質量和離子通道,錐形TSV可以改進TSV的填充效果和性能。

研究表明,錐形TSV還具有可靠性和傳輸性能方面的優勢。對不同幾何形狀TSV(包括紡錘形、錐形、橢圓形、三角形、四角形和圓柱形)的可靠性影響的研究表明,與其他TSV形狀相比,錐形TSV能更有效地均勻釋放垂直方向的熱應力。這意味著TSV底部的應力集中程度較低,從而降低了晶圓之間外部接觸區域發生故障的可能性,提高了TSV封裝的機械可靠性[3]。另外,對圓柱形和具有不同錐形角度的錐形TSV的功率損耗進行比較研究,發現錐形TSV由于表面積和寄生參數較小,具有更好的功率性能,能夠降低功率反射損耗,提高功率傳輸效率[4]。

目前有兩種方法可以制備錐形TSV,一種是改良的BOSCH工藝,一種是SF 6 /O 2低溫反應離子刻蝕(RIE)法。改良的BOSCH工藝是在傳統的BOSCH工藝的基礎上,通過調整脈沖時間,增加刻蝕脈沖時間,減少鈍化時間,從而形成錐形TSV [5]。然而,這種方法只能獲得有限的錐形角度(85°~90°),不能滿足大多數應用的需求。為了改善錐形TSV的開口度,有些研究在BOSCH工藝后再進行一次各向異性刻蝕,使孔口呈喇叭狀[6-7]。該工藝改善了孔口位置的膜層連續性,但對孔底,尤其是孔底拐角處的膜層改善還有待提高。

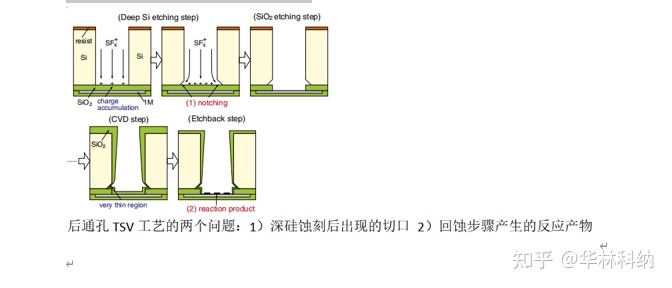

另一種方法是SF 6 /O 2低溫RIE法,此方法中SF 6分解得到的F*自由基各向同性地刻蝕硅,O 2的加入將F自由基與Si發生反應生成物SiF x氧化成SiO x F y,SiO x F y附著在刻蝕槽的側壁上,在側壁上形成保護層,從而增加刻蝕的方向性[8]。低溫可以增加對氧化硅掩膜的刻蝕選擇比,降低反應產物SiF 4的揮發性,從而增強鈍化效果,增加各向異性[9]。SF 6 /O 2低溫RIE法可以實現小于85°且可控的傾斜角并得到較大的深寬比,擴大了TSV工藝整合的可能性[10]。但是,SF 6 /O 2低溫RIE法也存在一些缺點,如在掩膜與晶圓交界處容易形成側掏尖角,導致在該處沉積的介質和金屬薄膜斷裂,增加了TSV通孔填充的難度和漏電的風險[11]。另外,低溫RIE通常要求極低的溫度(-40~ -100℃),使得大部分刻蝕機難以實現[10]。

因此,改良的BOSCH工藝和低溫RIE法都有一定的局限性,不能適應大多數應用場景。為了解決這個問題,本文提出了一種在非低溫條件下制備錐形TSV的兩步刻蝕法,并研究了如何控制和改善錐形角度和錐形TSV形貌。同時,通過研究錐形TSV中的膜層厚度和電鍍填充深度驗證了所得到的錐形TSV在膜層沉積和電鍍填充過程中的優勢。

1錐形TSV的兩步刻蝕

1.1錐形TSV的兩步刻蝕法

錐形TSV的等離子體各向異性刻蝕是在F *自由基刻蝕和氧氣鈍化之間找到一個平衡,使得側壁有節制地被刻蝕,且其刻蝕速率明顯小于孔底的刻蝕速率。錐形深孔的刻蝕是在SPTS反應離子刻蝕機中進行的。在這個刻蝕過程中,溫度、電感耦合等離子體(ICP)功率、腔室壓力、射頻(RF)偏壓、氣體體積流量、SF 6與O 2的體積流速比均會影響刻蝕結果,如刻蝕速率、選擇性、通孔輪廓、側壁傾斜程度、側掏。

ICP功率和RF偏壓是影響刻蝕速率的主要因素。ICP功率越高,等離子體的密度越大,離子通量越大,刻蝕速率越高。RF偏壓越高,轟擊晶圓的離子能量越大,刻蝕速率和陡直度越高。

腔室壓力會影響反應離子的平均自由程,進而影響到各向異性。腔室壓力的減小會產生較高的各向異性,增加刻蝕垂直度。而腔室壓力增加,離子濃度增加,反應離子的平均自由程減小,離子偏轉嚴重,會導致側掏現象。側掏會在掩膜下方形成側掏尖角(或下切),形成如圖1(a)所示的孔形。

F與O原子數比是影響側壁傾斜度(即錐形角度)的主要因素[12]。這是由于F原子和O原子在表面的競爭吸附,O原子的吸附導致鈍化,而F原子的吸附導致硅刻蝕。F與O原子數比增加,表面吸附的O原子的側壁鈍化跟不上F原子的吸附導致的刻蝕,從而導致負錐度,孔形下大上小,同時側掏現象嚴重。當F與O原子數比減小,O原子的競爭吸附減少了F原子的吸附刻蝕,鈍化效果增強,形成正錐形深孔。

溫度對各向異性和側掏均有影響。溫度降低,可降低反應產物SiF 4的揮發性,生成鈍化層,增強鈍化效果。在孔底,由于等離子體產生的離子轟擊使鈍化層脫離,進行所謂的濺射刻蝕。而側壁由于受到較少的離子轟擊,其上的鈍化層得到部分保留。這樣,溫度降低,各向異性提高,側掏減少。研究表明,將基底溫度設置為約-100℃,可以將各向異性刻蝕減至最低程度[13]。

但是,這樣的極低溫對于大多數刻蝕機來說是很難實現的。為了找到更易于實現的技術方法,此處將溫度控制為5℃。經過調整,第一步刻蝕參數設置為:溫度為5℃,腔室壓力為25 mTorr(1 Torr≈133 Pa),ICP功率為800 W,射頻(RF)功率為50 W,SF 6和O 2體積流量均為40 cm 3 /min,刻蝕時間為20 min。

圖1(b)為第一步刻蝕后帶有側掏尖角的錐形TSV截面的光學顯微鏡圖。經過20 min刻蝕,孔徑為20μm的孔深度達到了67μm。側壁的傾斜角度,即錐形TSV的錐形角度為86°。雖然第一步刻蝕形成了錐形,孔內直徑最大處達到了30μm,但是由于側掏尖角的存在,開口處孔徑依然較小,為23μm。

為了消除側掏尖角,改善孔的形狀,在去除掩膜層后進行第二步各向同性刻蝕。刻蝕參數設置為:溫度為25℃,腔室壓力為35 mTorr,ICP功率為800 W,SF 6、Ar和C 4 F 8體積流量分別為80、40和10 cm 3 /min,刻蝕時間為2 min。第二步刻蝕中只使用了有刻蝕作用的SF 6,而不用有鈍化作用的O 2。同時,Ar和C 4 F 8的加入可以降低刻蝕速度,避免由于刻蝕速率過快導致的表面粗糙。圖1(c)為第二步各向同性刻蝕去除側掏尖角的示意圖。圖1 (d)為經過2 min各向同性刻蝕后所得到的TSV截面的光學顯微鏡圖。明顯可以看到側掏尖角已被去除。同時,孔底直徑幾乎沒有變化,但是孔上部擴大,錐形角度增加,形成喇叭狀。這一形貌更有利于膜層的連續沉積和無孔隙的電鍍填充。

1.2不同孔徑的刻蝕

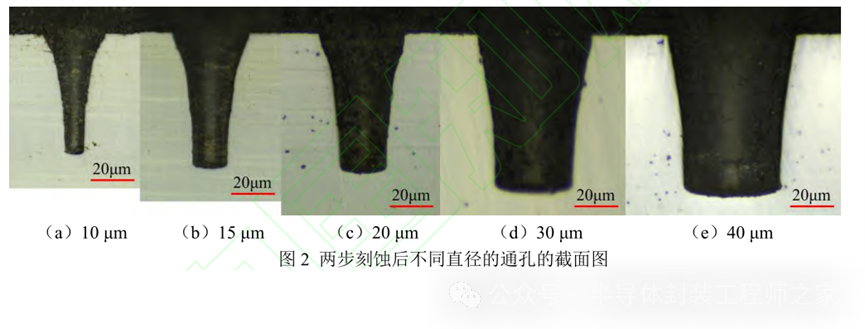

圖2為經過相同刻蝕過程(20 min的第一步刻蝕和2 min的第二步刻蝕)后不同設計直徑(即掩膜開口孔徑)的深孔的截面圖。可以明顯看到孔深隨著孔徑的增大而增大,而錐形程度卻減小了。

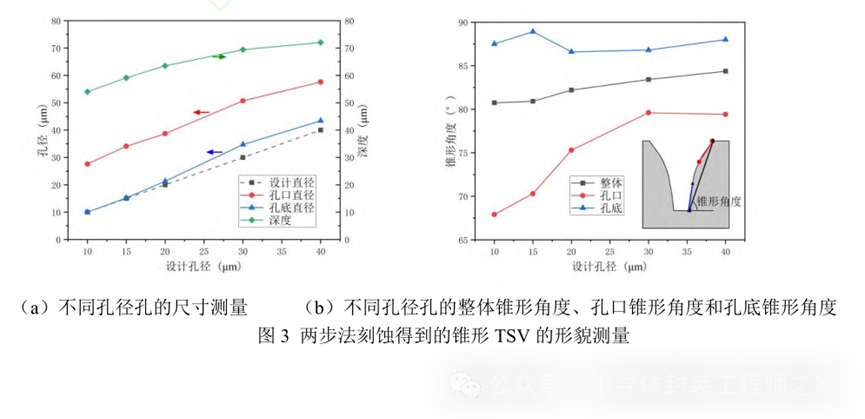

圖3(a)測量了孔深和孔底直徑、孔口直徑,并與設計直徑進行了比較。結果顯示,在相同的刻蝕條件下,大孔徑的孔深度較大,孔底直徑更容易比設計直徑偏大。這是因為在相同的刻蝕條件下,刻蝕氣體更容易進入大尺寸孔內,因此對于孔底及側壁的刻蝕會更快。相反,對于小尺寸的孔徑,刻蝕氣體難以進入,因此刻蝕速率相對較慢。這與深硅刻蝕中與深寬比相關的負載效應(ARDE)相一致。

圖3(a)中可以看到,孔口直徑均比孔底直徑大14~19μm,印證了孔的錐形形貌。通過孔口直徑(a),孔底直徑(b)和孔深(d),計算得到孔壁的錐形角度(θ),即

圖3 (b)中黑色的點線為通過孔深、孔口和孔底直徑計算得到的錐形角度。但是通過圖2可以觀察到孔側壁并不是直線,孔上部普遍孔壁更傾斜,錐形角度更小。因此選擇測量孔的上1/3和下1/3分別作為孔口和孔底的錐形角度。圖3 (b)中紅色和藍色線分別畫出了孔口和孔底的錐形角度。

可以看到,不同孔徑的孔底錐形角度比較相似,在86.6°~88.9°之間。而孔口的錐形角度則比孔底小,在68°~79°之間,并且在10~30μm孔徑范圍內隨著孔徑的增大而增大,即傾斜度降低。這說明大孔徑的喇叭口傾斜程度更小,而小孔徑的喇叭口傾斜程度更大,這一現象也可以在圖2中直觀地看出。這是因為,在相同的第二步各向同性刻蝕工藝下,樣品表面部分刻蝕速率是相同的。無論是大孔徑圖形還是小孔徑圖形,在孔口處的側向刻蝕速率是相同的。因此,對于小尺寸的孔徑來說,相同時間的刻蝕會導致其孔口直徑增加的比例更大,這也就意味著孔口處會更加傾斜。而當孔徑繼續增大,這一影響逐漸減小,導致孔徑30μm以上的孔口錐形角度變化不大。

2膜層沉積

刻蝕后的硅深孔內需要依次沉積絕緣層、阻擋層和種子層:絕緣層用來電隔離硅基底和填充的導電材料,通常選用二氧化硅;阻擋層用來防止銅原子穿透二氧化硅絕緣層而導致的封裝器件產品性能下降甚至失效,一般使用化學穩定性較高的金屬材料及其化合物,如Ta、Ti、TaN等;種子層在后續的電鍍填充中提供導電,一般使用Cu。兩步刻蝕得到的喇叭狀的孔口角度較平滑,有利于膜層在孔口的連續分布。上大下小的錐形TSV也使得孔口的遮蔽效應減小,有利于孔底部的膜層沉積。

本文使用的絕緣層、阻擋層和種子層分別為2μm SiO 2、50 nm Ta和800 nm Cu。在Oxford電感耦合等離子體化學氣相沉積(PECVD)設備中沉積SiO 2絕緣層,沉積條件為:ICP功率為1 000 W,溫度為200℃,腔室壓力12 mTorr,SiH 4、Ar和N 2 O體積流量分別為14、60和70 cm 3 /min,沉積時間為195 min。在Denton多靶磁控濺射鍍膜系統中濺射了阻擋層和種子層。阻擋層Ta的濺射條件為:濺射直流功率為200 W,Ar體積流量為40 cm 3 /min,時間為150 s。種子層Cu的濺射條件為:濺射直流功率為200 W,Ar體積流量為40 cm 3 /min,時間為1 200 s。

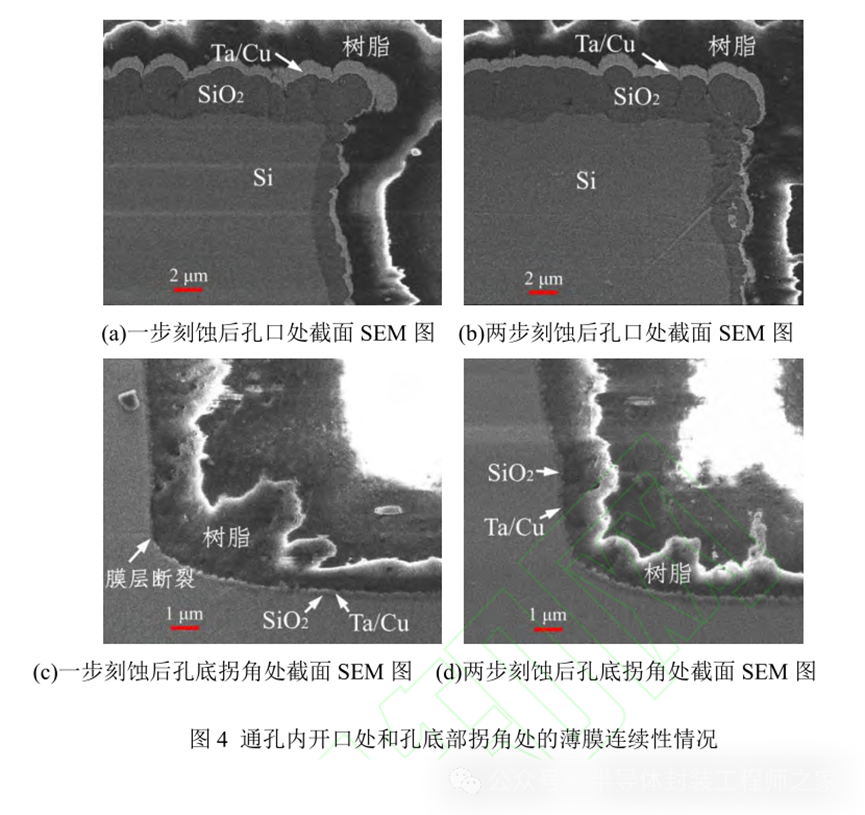

圖4對比了一步刻蝕和兩步刻蝕后得到的20μm直徑,65μm深度孔的孔口處和孔底拐角處(一般為膜層最薄處)的膜層沉積情況。由于掃描電子顯微鏡(SEM)的成像原理和精度限制,Ta和Cu層無法區分,在圖像上表現為一層(Ta/Cu層)。為了研磨得到可觀察的截面,使用樹脂填充了孔內空間,樹脂在SEM圖中表現為不導電導致的高亮區域。可以在圖4 (a)和圖4 (b)中看到,ICP-化學氣相沉積(CVD)沉積SiO 2的過程中會在孔口的側掏尖角位置沉積更多的SiO 2,使尖角更加突出,這會進一步惡化后續種子層的沉積環境。在圖4 (b)中,雖然同樣孔口位置絕緣層沉積比較多,但是喇叭狀開口可以部分彌補其導致的孔形變化。從圖4 (c)和圖4 (d)種可以看到,孔底拐角處的膜層厚度比孔口小了很多,而有側掏尖角的圖4(c)中膜層已經觀察不到連續的膜層。

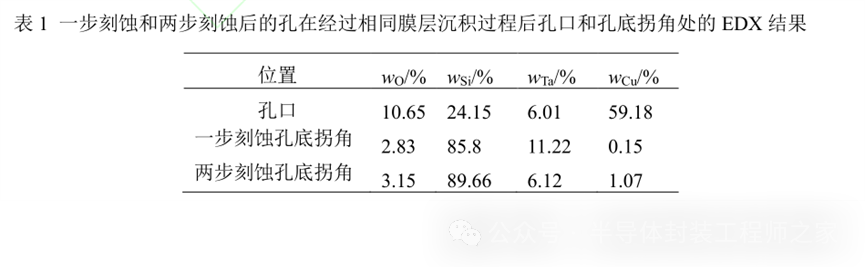

為了進一步確認孔底金屬的分布情況,對孔底部拐角處和孔口位置進行了能量色散X射線光譜(EDX)分析。表1列出了孔口位置和孔底拐角處O、Si、Ta和Cu的質量分數(w O、w Si、w Ta和w Cu)。EDX測試中電子束的穿透深度為1~2μm。因此,在孔口,當金屬膜層較厚時,EDX主要收集到金屬膜層的信號。在孔底,當金屬膜層較薄時,EDX穿過金屬膜層,更多地收集到了絕緣層和基底的材料信息。從表1中可以看到,在孔口,金屬Ta和金屬Cu的質量分數分別為6.01%和59.18%,這說明有充足量的阻擋層和種子層。而在一步刻蝕后的有側掏尖角的孔底拐角處,金屬Ta的質量分數為11.22%。說明阻擋層的沉積受側掏尖角影響不大,能夠覆蓋到孔底。而O元素和金屬Cu的質量分數下降到了2.83%和0.15%。說明絕緣層和種子層的量不足。第二步刻蝕去除側掏尖角后,O元素和Cu的質量分數上升至3.15%和1.07%。可見,兩步刻蝕去除側掏尖角對孔底絕緣層和種子層的改善有明顯作用。

在電鍍填充過程中,種子層是金屬沉積的起始點,其厚度和連續性對電鍍填充的質量具有重要影響。如果種子層過薄或不連續,金屬無法在孔底沉積,就會導致孔底缺陷,如空洞、針孔、短路等[14]。要確定膜層對填充的真實影響,還需要通過電鍍填充結果來確定。

3電鍍填充

以高純銅片作為陽極,帶有TSV的濺射了種子層的晶圓作為陰極進行電鍍填充。電鍍液采用新陽SYS2520甲基磺酸體系電鍍液,并加入針對深孔電鍍的UPT3360系列添加劑。首先,采用10 mA/cm 2的電流密度進行預電鍍,以在深孔內壁形成一層均勻的銅層。接著,將電流密度提高到40 mA/cm 2,進行正式填充電鍍。不同直徑的TSV需要不同的電鍍時間才能達到完全填充。如,10μm和30μm直徑的TSV分別需要6 h和10 h的填充時間。

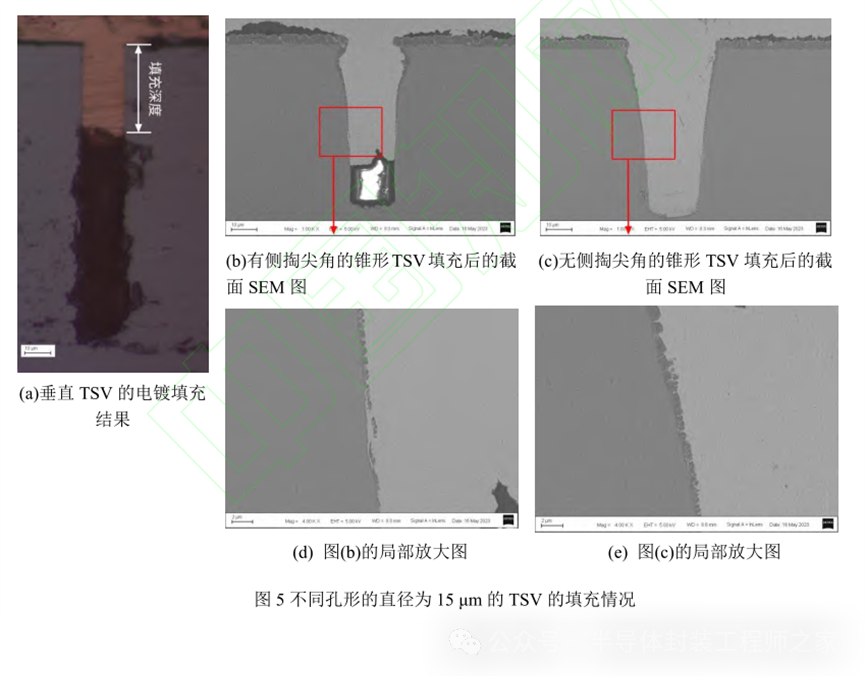

圖5為直徑15μm的孔,在不同的孔形下,經過相同的膜層濺射和電鍍填充步驟后的截面圖。圖5 (a)為一個通過BOSCH工藝刻蝕的直徑為15μm、深度為100μm的垂直TSV的電鍍填充效果。填充深度大約為30μm。由于種子層未能完全覆蓋,孔深處大部分沒有得到填充。在圖5 (b)中,一步錐形刻蝕后形成的錐形深孔的填充深度增加到了40μm。然而,由于側掏尖角的存在,孔的填充深度增加有限,因此孔仍然沒有完全填滿。在圖5 (c)中,第二步各向同性刻蝕將側掏尖角完全消除,電鍍填充深度進一步增加,使得深度為60μm的孔得以完全填充。

由此可見,錐形TSV的形成和側掏尖角的消除有助于增加TSV的填充深度。這是由于擴大了的孔口提高了種子層在深孔側壁,尤其是孔底區域的覆蓋率,從而改善了電鍍過程中孔內的導電情況;另外,較大的孔口也讓鍍液中的銅離子更容易擴散到孔內并發生還原反應。

圖5 (d)和(e)分別放大了圖5 (b)和(c)中側壁上的近似位置。由于阻擋層和種子層已經和填充的銅合為一層,很難觀察到阻擋層和種子層的具體情況。但是,在圖5 (d)中可以觀察到帶有側掏尖角的深孔中絕緣層出現了斷裂。鑒于阻擋層和種子層在絕緣層的上層,可以推斷它們也出現了斷裂情況。絕緣層的斷裂可能導致該區域出現電流泄漏和信號丟失。阻擋層的斷裂會導致銅向硅基底的擴散。種子層的斷裂會影響填充效果。在斷裂位置附近出現了填充空缺與這一推斷吻合。在圖5 (e)中側掏尖角被消除后,絕緣層保持了連續性。雖然不能直接觀察到阻擋層和種子層的連續分布,但阻擋層的EDX數據和孔的完全填充現象證明了阻擋層和種子層的完全連續覆蓋。

4結論

本文提出了一種用于制備錐形TSV的兩步刻蝕工藝。該工藝首先采用RIE在相對常溫下形成錐形TSV,然后進行各向同性刻蝕以消除側掏尖角并優化錐形輪廓。通過這種工藝,可以在直徑10~40μm的孔中實現底部錐形角度約為87°,頂部錐形角度為68°~79°的喇叭狀錐形TSV。本文還驗證了錐形側壁對薄膜連續性和TSV填充質量的影響,并在孔徑15μm,孔深60μm的TSV中實現了連續膜層分布和完全填充。證明了錐形TSV和側掏尖角的去除有助于實現完整的薄膜覆蓋,從而改善了TSV的隔離、阻擋和填充效果。通過兩步刻蝕工藝,降低了TSV制備的工藝難度和工藝成本,提高了填充質量和工藝穩定性。這將在高密度、高質量封裝中有巨大的應用潛力,對半導體產業鏈和科研領域都具有重要意義。

審核編輯:劉清

-

晶圓

+關注

關注

52文章

4838瀏覽量

127793 -

信號傳輸

+關注

關注

4文章

409瀏覽量

20145 -

電感耦合

+關注

關注

1文章

61瀏覽量

15864 -

TSV封裝

+關注

關注

0文章

12瀏覽量

2358 -

刻蝕機

+關注

關注

0文章

47瀏覽量

4195

原文標題:【光電集成】基于兩步刻蝕工藝的錐形TSV制備方法

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TSV工藝流程與電學特性研究

Sic mesfet工藝技術研究與器件研究

13um應變補償多量子阱SLD臺面制作工藝的研究

晶體硅太陽能電池刻蝕的作用及方法與刻蝕的工藝流程等介紹

通過兩步濕法刻蝕法制備黑硅

氮化鎵外延片工藝介紹 氮化鎵外延片的應用

半導體制造技術之刻蝕工藝

基于兩步刻蝕工藝的錐形TSV制備方法

基于兩步刻蝕工藝的錐形TSV制備方法研究

基于兩步刻蝕工藝的錐形TSV制備方法研究

評論