三大代工廠計劃盡快在2nm節點實現背面供電,為更快、更高效的芯片交換、減少路由擁塞和降低多個金屬層之間的噪聲奠定基礎。

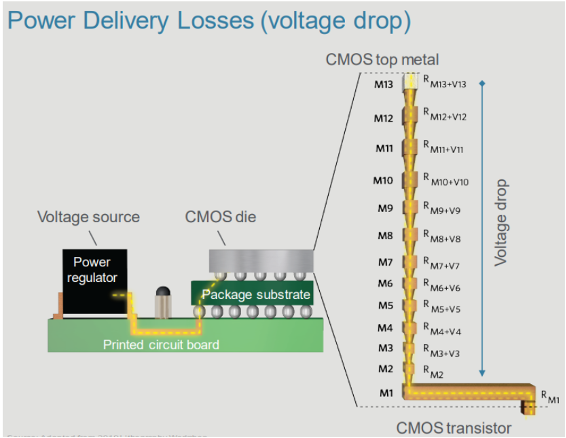

使用這種方法的好處是顯著的。通過在背面使用稍粗的、電阻較小的線路來輸送電力,而不是低效的正面方式,由于電壓降較小,功率損失可以減少30%。在典型的高級節點處理器中,電力線可能穿過15層或更多的互連層。這一變化還為信號釋放了前端的路由資源,特別是在第一個也是最昂貴的金屬層,并且減少了由于有時不可預測的、與工作負載相關的物理影響而大大增加設計復雜性的各種類型的交互。

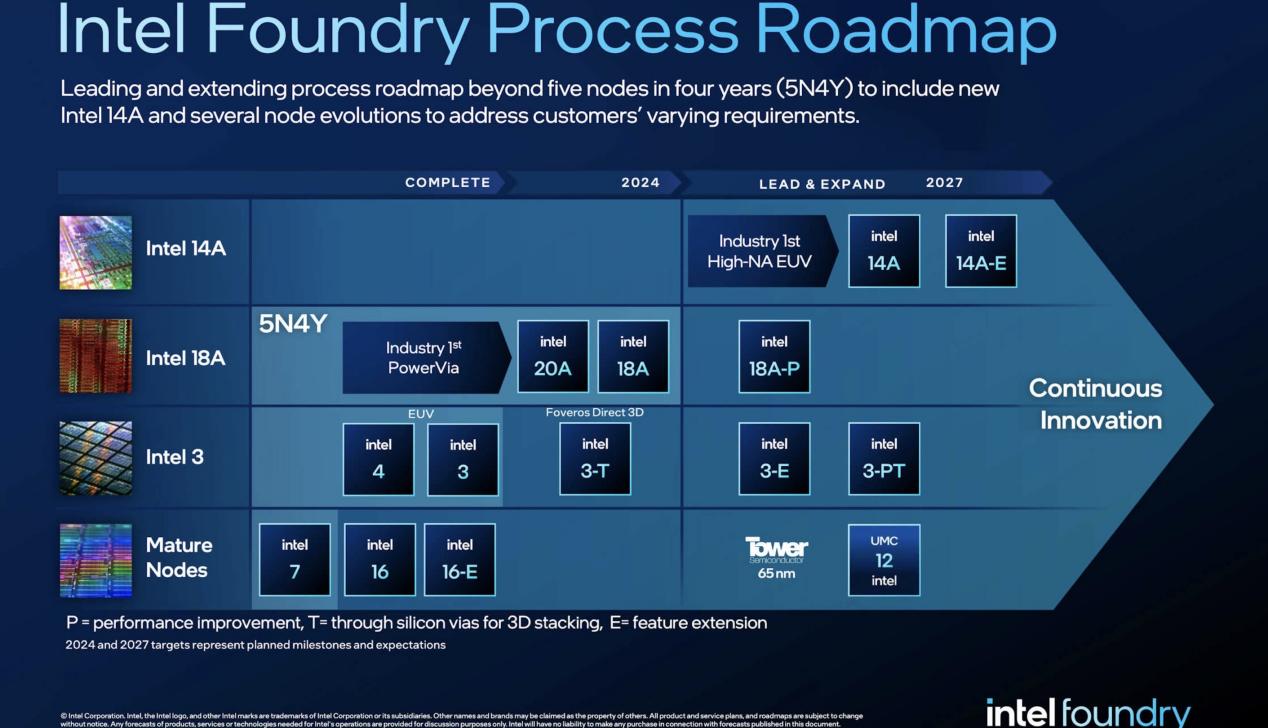

英特爾可能是第一個采用背面供電的公司,因為它正在努力恢復其在工藝技術方面的領先地位,但三星和臺積電將很快跟進。

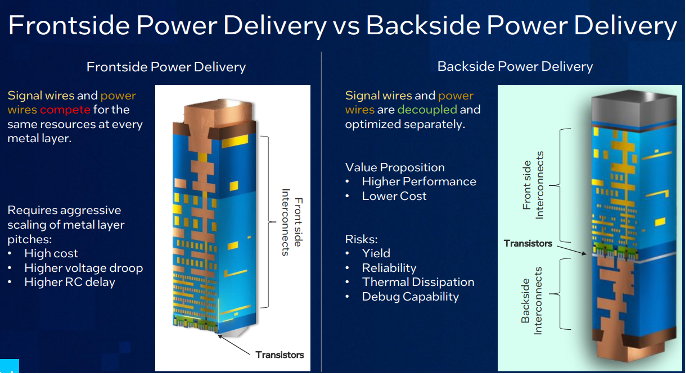

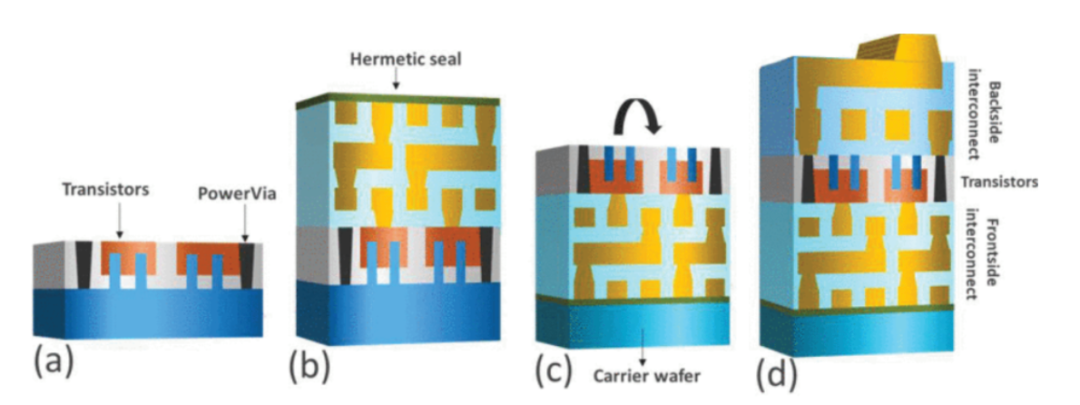

圖1:背面供電減少了電壓下降和RC延遲,但需要更長的時間才能完全處理。來源:英特爾

然而,這不是一個簡單的改變。背面供電(BPD)帶來了一系列的工藝挑戰,包括由于晶圓極度變薄和晶圓背面到正面的粘合而導致的光刻校正,后者每個芯片包含數百萬納米tsv。

盡管如此,背面供電似乎是值得的。“我們學習了很多東西,幫助我們為這一過程鋪平了道路。例如,優化如何精確研磨晶圓,這樣就不會損壞晶體管本身,”英特爾技術開發副總裁本·塞爾(Ben Sell)說。

Sell的團隊正在使用finfet和PowerVia優化Intel 4工藝,并在去年的VLSI研討會上展示了第一批器件。[1]該公司計劃在20A節點(2nm)將PowerVia與其帶狀場效應晶體管(RibbonFET)結合起來。通過BPD,該設備能夠實現6%的性能提升(Fmax), 90%的電池利用率和>30%的電壓下降。塞爾說:“既然兩邊都有布線,這確實有助于我們把標準電池排列得更近。”“就電池實際利用的面積而言,我們稱之為利用率。”

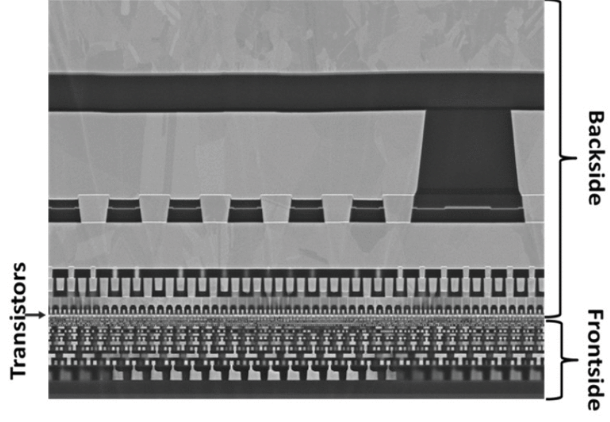

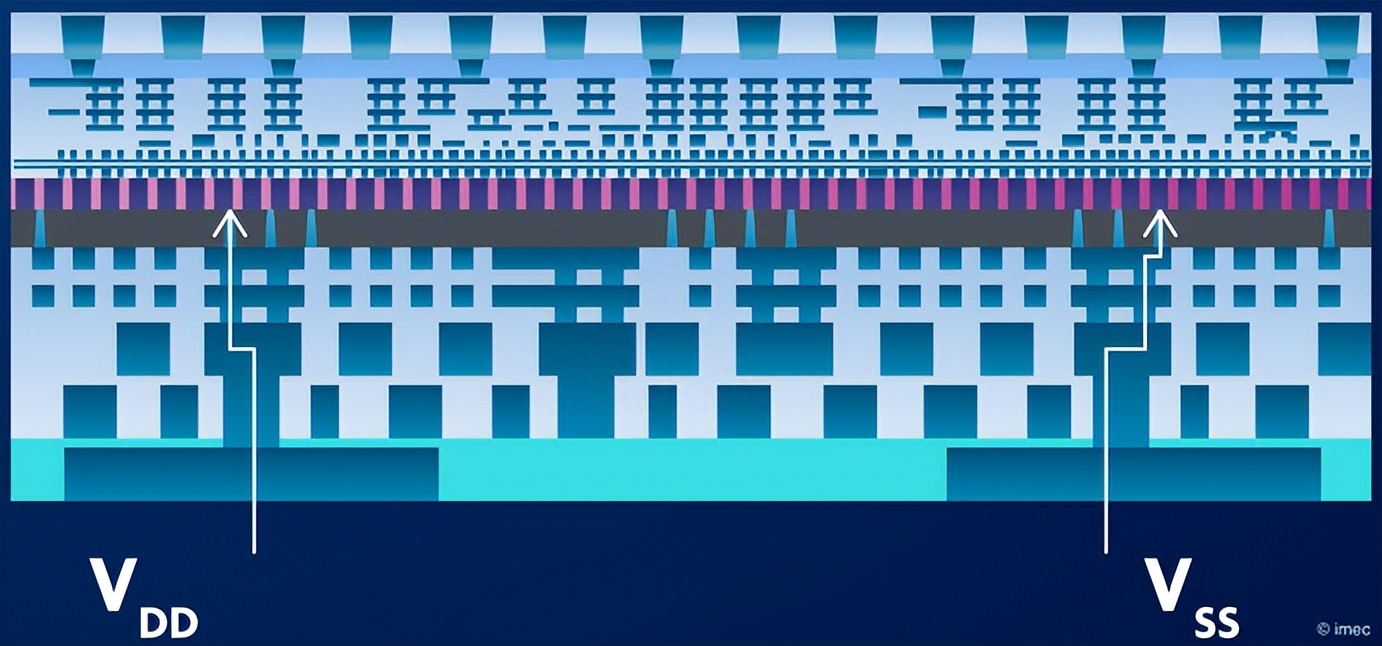

圖 2:晶圓背面使用 4 層互連,而正面使用 14 層,將微孔連接到接觸層。資料來源:英特爾

三星也在開發背面供電,早期研究表明它將實現令人印象深刻的性能指標。[2] 該公司報告稱,使用兩個不同的 Arm 內核,頻率提高了 3.6%,面積分別減少了 10% 和 19%。在標準單元之間使用 "電源分解 "單元進行電源和地面傳輸。該團隊還預計標準單元塊的面積將有所減少。

卓越的布線效率

理想的供電網絡可在任何活動中為集成電路上的有源電路持續穩定地提供電流。從集成電路的電源引腳到電路中的晶體管,所有互連路徑中的 PDN 直流電阻是最重要的參數之一。

圖 3:與需要穿越 15 層或更多互連層的正面相比,背面供電傳輸大大縮短了凸塊和晶體管之間的路徑,而正面則存在高電壓損耗。資料來源:應用材料公司

IR壓降是高度擴展互連的瓶頸。通過使用背面供電,設計人員可以獨立優化布線,在背面使用較粗的銅線傳輸電源和接地,在正面使用較細的銅線傳輸信號。設備制造商將電網從昂貴的 Metal-0 級別中移除,這需要使用 EUV 進行雙重圖案化甚至三重圖案化。通過 BPD,該層將 metal-0 間距從 30nm 放松到 36nm。據 Sell 稱,盡管吞吐量更長,但僅這一改變就超過了額外流程層的費用。擁塞的緩解還減少了 RC 延遲,因此晶體管可以在更高的頻率下運行。“大部分成本效益來自于使用更簡單的 EUV 流程,需要更少的工具。也許你可以通過一次光刻來完成光刻,而不是通過兩三次。”

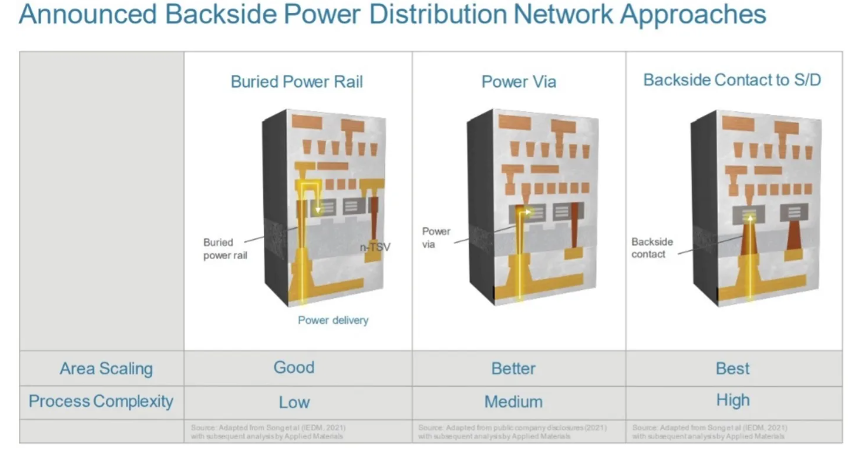

imec 研究人員于 2019 年提出的背面功率交付是實現持續邏輯擴展的關鍵一步。這種方法主要分為三類(見下圖 4)。

圖4:BPD 方案提供了與晶圓加工復雜性水平不斷提高相關的不同程度的縮放優勢。資料來源:應用材料公司

最簡單的方法是從 CMOS FET 周圍的電源軌向上連接一個深通孔,然后通過頂部觸點向下連接。PowerVia 使用納米 TSV 將背面電源網絡連接到晶體管的觸點層,從而實現了出色的擴展性。最后,"直接連接 "方法將背面微孔直接連接到每個晶體管的源極和漏極區域。

直接連接能實現最好的擴展,但也是三種方法中風險最大的一種。"imec 高級研究員、研發副總裁兼 3D 系統集成項目總監 Eric Beyne 說:"在制造器件之前,你要在鰭片之間放置金屬。"在前端之前進行金屬加工對人們來說有點可怕,但這可以讓你進行接觸,并有更多的空間。問題是,你需要將背面的光刻技術與正面對齊,但這個晶圓已經被粘合和減薄,因此會出現變形。"

不幸的是,在需要對齊頂部和底部晶圓上的特征的同時,頂部晶圓也會出現變形。即使在鍵合過程中對齊了晶圓,也需要掃描儀上的自適應光刻方案來實現校正,而校正是復雜的。并非所有的光刻都在同一方向上進行。與此同時,疊層預算也在縮減。Beyne 估計,根據不同的方案,可能會有 10 到 20 納米的疊加工作。如果采用更直接的連接方法,這一數字將急劇下降到 3 納米,這可能需要對鍵合引起的畸變進行更嚴格的控制。

"Beyne說:"這些源極/漏極特征很小,因為CPP(接觸柵極間距)只有45納米。"因此,S/D 的著陸相當具有挑戰性,必須極其精確。

微孔的長寬比(高/寬)往往在 10:1 左右。精確控制的蝕刻工藝對于新的微孔以及其他關鍵特征至關重要。"Lam Research 公司副總裁兼總經理 Kaihan Ashtiani 說:"BPD 的所有三種方法都涉及需要蝕刻的高縱橫比特征,然后用導體、絕緣體或兩者填充。

晶圓減薄工藝本身也不是那么簡單。硅片減薄后只剩下大約 500 納米。Imec 正在與 Disco 的工程師合作,以提高研磨工藝的均勻性和加工速度。

CMP 也起著至關重要的作用。Lam Research 公司高級總監 David Kretz 解釋說,在研磨過程之后要進行精細拋光 (CMP),以接近最終目標厚度并完全去除研磨損傷。然后用濕法清洗或干法蝕刻去除剩余的硅。硅鍺(SiGe)可作為蝕刻止動器。

"濕法硅蝕刻 "最初是為 CMOS 成像和功率器件開發的。其他應用還開發用于晶圓鍵合,特別是 NAND 器件--將 CMOS 陣列與存儲單元鍵合,"Kretz 說。這種蝕刻技術目前正被應用于背面電源軌應用。

濕法面臨的挑戰包括成本效益、均勻性(總厚度變化,TTV)以及修復研磨步驟造成的硅損傷。"Lam 克服了這些挑戰,首先使用快速蝕刻率工藝去除大塊硅(成本效益),然后轉用較低的蝕刻率工藝,使我們能夠更好地控制最終薄膜的粗糙度,"Kretz 說。

計量在監控均勻性方面發揮著至關重要的作用。"他解釋說:"我們的集成厚度測量系統(ITMS)使客戶能夠在濕法蝕刻前測量晶片,這樣我們就能根據研磨工藝產生的入料厚度變化調整工藝。"他解釋說:"這樣就能從整體上更嚴格地控制最終晶圓到晶圓的厚度變化。

圖 5:首先制作晶體管和電源過孔(a),然后進行多層正面金屬化和介質密封(b),再與硅載體鍵合(c),最后進行背面電源處理。資料來源:英特爾 來源:英特爾

在英特爾簡化的工藝流程中(見圖 5),該工藝首先制造出鰭式場效應晶體管(finFET)或全柵極晶體管,然后蝕刻納米硅片并填充鎢或其他低電阻金屬。接著,使用比正面配電網絡稍大的金屬 0 線制造信號互連(M0 至 M14)。接著,沉積介質(密封)密封件,然后翻轉前端晶圓并將其安裝在載體晶圓上。然后,對硅片進行研磨和拋光(CMP)。蝕刻擋塊有助于防止晶體管本身被移除。

最具挑戰性和最復雜的流程是直接接觸,將金屬接觸到晶體管的源極和漏極。"在直接源極接觸方法中,正面和背面連接的對齊是一項挑戰。此外,外延觸點的形成是從正面開始的,會在背面留下懸空。Ashtiani 說:"由于金屬填充是從背面進行的,因此懸空結構的金屬化是一個額外的挑戰。

Ashtiani 詳細闡述了由于已建成的銅堆棧所造成的熱預算限制,這使得工程師們不得不積極評估釕和鉬等金屬替代品。"他說:"鉬正在成為先進芯片制造中替代鎢的一種引人注目的替代品。"Epi 背面觸點是在 BEOL 工藝后制造的,因此溫度上限為 400 至 450°C。在 BEOL 熱預算范圍內形成歐姆低電阻觸點將是一個巨大的挑戰。

在 Lam 的研究中,鉬沉積已經顯示出形成歐姆觸點的能力,在保形和自下而上的觸點填充方案中使用低溫原子層沉積(ALD)鉬。鉬的其他優點還包括平均自由路徑更短。因此,即使在較小的特征尺寸下,電阻率仍然較低。此外,鉬對電介質沒有內在擴散性,因此不需要較高電阻率的阻擋層。

另一種正在測試的金屬是釕。在多項研究中,釕已被探索用作前端觸點的替代觸點材料,imec 公司的研究表明,與鎢電源軌相比,釕在背面電源傳輸中可將電阻降低 40%。這兩種金屬的主要區別在于成本。釕前驅體比鉬前驅體貴一個數量級。

調試

當所有互連都局限在晶片正面時,故障隔離和調試傳統上都是通過硅背面進行的。背面金屬化改變了這種分析方法。"當兩面都有金屬時,顯然就更難了,因為突然間就有金屬層擋住了去路。英特爾的塞爾說:"我們必須開發出不同的技術,以確保即使穿過這些金屬線,我們仍能定位缺陷并對其進行表征。該公司正在使用現有的和新穎的調試技術來進行這些分析。

與此同時,公司還利用等速掃描測試模式進行測試,以確定速度路徑問題,從而確定并修復設計中限制性能的路徑,使設備能夠以更高的時鐘頻率運行。對于每個故障掃描單元,都會根據邏輯模擬值的結構分析來確定故障路徑。

產量和可靠性

為確保可靠性,芯片制造商采用了與任何復雜邏輯器件相同的可靠性測試方法,包括時間相關介質擊穿(TDDB)、偏置溫度不穩定性(BTI)和熱載流子注入(HCI)。

有趣的是,三星分析了與封裝工藝相關的熱機械可靠性,以確保不會出現不連續性。工程師們分析了多層金屬堆疊引起的應力水平,包括背面背面供電與傳統互連堆疊引起的應力。該團隊利用建模對其 4nm 節點的倒裝芯片封裝方案進行了比較。"他們在最近的一篇文章中說:"......我們選擇了單個凸點(即位于芯片邊緣的凸點)所受拉伸應力最大的位置,并在封裝模型的熱位移邊界條件下檢驗了 BEOL 子模型。

使用背面電源的芯片在 Z 方向上產生的拉伸應力比使用背面電源的芯片大 62%,這些應力集中在 nanoTSV 正上方的第一層金屬上。研究小組進行了測量,包括納米 TSV 尺寸調整。通過使 TSV 加寬(或縮短)10%,應力得到緩解,阻力降低,同時利用環形振蕩器模擬提高了速度。他們的研究表明,TSV 的尺寸和阻擋金屬的厚度都會影響應力和性能。

一般來說,應力積聚是業界日益關注的問題,特別是隨著越來越多地使用臨時鍵合工藝,以便將不同的架構或材料組合在一起。"Brewer Science 公司首席技術官 Rama Puligadda 說:"客戶希望粘合材料能在整個過程中將器件晶片固定在載體上,而不會出現分層。布魯爾科技公司的首席技術官 Rama Puligadda 說:"因此,在一切準備就緒、真正可以剝離之前,剝離層不能釋放粘合劑。但這樣它就需要非常容易地脫開,可以通過機械方法或使用激光。因此,對于應力極大的晶片來說,這種平衡更具挑戰性。

結論

背面供電是一種突破性的方法,它能更有效地為器件提供功率,同時還能提高最小前端互連的可制造性。工藝改進主要圍繞光刻畸變校正、CMP、蝕刻、清潔和接合工藝。隔離故障變得更具挑戰性。不過,這種生產更快邏輯器件的方法有望最早于明年在器件中出現。

審核編輯:黃飛

-

CMOS

+關注

關注

58文章

5680瀏覽量

235136 -

英特爾

+關注

關注

60文章

9880瀏覽量

171487 -

直流電阻

+關注

關注

1文章

147瀏覽量

14842 -

晶體管

+關注

關注

77文章

9633瀏覽量

137843 -

柵極晶體管

+關注

關注

0文章

6瀏覽量

8411

原文標題:2納米芯片的背面供電

文章出處:【微信號:晶揚電子,微信公眾號:晶揚電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

2納米芯片的背面供電技術分析

2納米芯片的背面供電技術分析

評論