基于IP的設計已成為目前FPGA設計的主流方法之一,本章首先給出IP的定義,然后以FFT IP核為例,介紹賽靈思IP核的應用。

IP核綜述

IP(Intelligent Property) 核是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC 階段,IP核設計已成為ASIC電路設計公司和FPGA提供商的重要任務,也是其實力體現。對于FPGA 開發軟件,其提供的IP核越豐富,用戶的設計就越方便,其市場占用率就越高。目前,IP核已經變成系統設計的基本單元,并作為獨立設計成果被交換、轉讓和銷售。

從IP核的提供方式上,通常將其分為軟核、硬核和固核這3類。從完成IP核所花費的成本來講,硬核代價最大;從使用靈活性來講,軟核的可復用使用性最高。( 這部分內容前面已經闡述,這里再重申一下)

軟核(Soft IP Core)

軟核在EDA設計領域指的是綜合之前的寄存器傳輸級(RTL) 模型;具體在FPGA設計中指的是對電路的硬件語言描述,包括邏輯描述、網表和幫助文檔等。軟核只經過功能仿真,需要經過綜合以及布局布線才能使用。其優點是靈活性高、可移植性強,允許用戶自配置;缺點是對模塊的預測性較低,在后續設計中存在發生錯誤的可能性,有一定的設計風險。軟核是IP 核應用最廣泛的形式。

固核(Firm IP Core)

固核在EDA設計領域指的是帶有平面規劃信息的網表;具體在FPGA設計中可以看做帶有布局規劃的軟核,通常以RTL 代碼和對應具體工藝網表的混合形式提供。將RTL描述結合具體標準單元庫進行綜合優化設計,形成門級網表,再通過布局布線工具即可使用。和軟核相比,固核的設計靈活性稍差,但在可靠性上有較大提高。目前,固核也是IP核的主流形式之一。

硬核(Hard IP Core)

硬核在EDA 設計領域指經過驗證的設計版圖;具體在FPGA 設計中指布局和工藝固定、經過前端和后端驗證的設計,設計人員不能對其修改。不能修改的原因有兩個:首先是系統設計對各個模塊的時序要求很嚴格,不允許打亂已有的物理版圖;其次是保護知識產權的要求,不允許設計人員對其有任何改動。IP 硬核的不許修改特點使其復用有一定的困難,因此只能用于某些特定應用,使用范圍較窄。

IP Core生成器(Core Generator) 是Xilinx FPGA設計中的一個重要設計工具,提供了大量成熟的、高效的IP Core為用戶所用,涵蓋了汽車工業、基本單元、通信和網絡、數字信號處理、FPGA特點和設計、數學函數、記憶和存儲單元、標準總線接口等8 大類,從簡單的基本設計模塊到復雜的處理器一應俱全。配合賽靈思網站的IP中心使用,能夠大幅度減輕設計人員的工作量,提高設計可靠性。

Core Generator最重要的配置文件的后綴是xco,既可以是輸出文件又可以是輸入文件,包含了當前工程的屬性和IP Core的參數信息。

5.7.2 FFT IP核應用示例

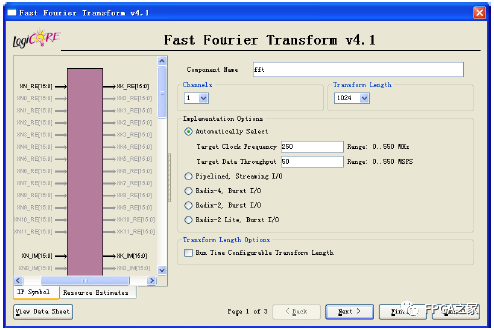

ISE提供了FFT/IFFT的IP Core,可以完成實數、復數信號的FFT以及IFFT運算。FFT的IP Core提供三種結構,分別為:

(1) 流水線,Streaming I/O結構:允許連續的數據處理;

(2) 基4,Burst I/O結構:提供數據導入/導出階段和處理階段。此結構擁有較小的結構,但轉換時間較長;

(3) 基2,Burst I/O結構:使用最少的邏輯資源,同Radix-4相同,提供兩階段的過程。其配置界面有3頁,第一頁如圖5-57所示,主要用于配置實現結構;第二頁配置數據位寬以及數據處理操作;第三頁配置數據緩存空間。

圖5-57 FFT IP core的用戶界面

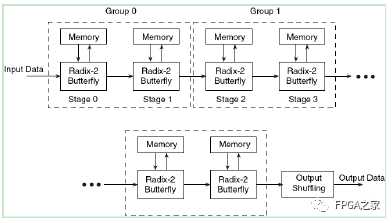

在實際硬件操作中,模塊的執行速度是很重要的參數,所以本文分析第一種結構,即流水線Streaming I/O結構,以進行連續的數據處理。在進行當前幀的N點數據時,可加載下一幀的N點數據,同時輸出前一幀的N點數據。此結構由多個基2的蝶形處理單元構成,每個單元都有自己的存儲單元來存儲輸入和中間處理的數據,其結構如圖5-58所示。

圖5-58 FFT模塊的流水線,Streaming I/O結構

FFT的計算單元具有豐富的控制信號,其詳細說明見下文。

XN_RE、XN_IM :輸入操作數,分別為實部和虛部,以2 的補碼輸入。在使用時應當確定其位寬。

START :FFT開始信號,高有效。當此信號變高時,開始輸入數據,隨后直接進行FFT 轉換操作和數據輸出。一個START脈沖,允許對一幀進行FFT 轉換。如果每N 個時鐘有一個START脈沖或者START始終為高,,則都可以連續進行FFT。如果在最初的START前,還沒有NFFT_WE,FWD_INV_WE,SCALE_SCH_WE信號,則START變高后就使用這些信號的默認值。由于此IP Core支持非連續的數據流,因此在任何時間輸入START,即可開始數據的加載。當加載N個數據結束后,就開始FFT轉換運算。

UNLOAD :對于Burst I/O結構,此信號將開始輸出處理的結果。對于流水線結構和比特逆序輸出的情況,此端口不是必要的。

NFFT :此端口只對實時可配置應用時有用。

NFFT_WE :此端口是NFFT 端口的使能信號。

FWD_INV :用以指示IP Core為FFT還是IFFT,其等于1時IP Core進行FFT運算,否則進行IFFT 運算。至于采用哪種轉換運算是可以逐幀變化的。這一端口給FFT的使用提供了很大的方便。

FWD_INV_WE :作為FWD_INV端口的使能信號。

SCALE_SCH:(1) 在IP Core設計時,如果選擇在計算過程中進行中間數據的縮減,那么此信號才可起作用;(2) 輸入的位寬等于2*ceil(NFFT/2),其中NFFT = log2(point size)。(3) 流水線結構中,將每個基2的蝶形處理單元視為一個階段,每個階段進行一次數據的縮減,縮減的比例以此輸入中對應階段的兩比特表示。(4) 每階段的兩比特數可以是3,2,1或0 :它們表示了數據所需要移動的比特數。

SCALE_SCH_WE :作為SCALE_SCH的使能信號。

SCLR :可選端口。

Reset :重置信號端口。Reset=1時,所有工作都停止且初始化。但內部的幀緩存保留其內容。

CE :可選端口。

CLK :輸入時鐘。

XK_RE,XK_IM :輸出數據總線,以2 的補碼輸出。SCALE_SCH_WE有效時,輸出位寬等于輸入;否則,輸出位寬= 輸入位寬+NFFT+1。

XN_INDEX :位寬等于log2(point size),輸入數據的下標。

XK_INDEX :位寬等于log2(point size),輸出數據的下標。

RFD :數據有效信號,高有效,在加載數據時為高電平。

BUSY :IP Core 工作狀態的指示信號,在計算FFT 轉換時為高電平。

DV :數據有效指示信號,當輸出端口存在有效數據時變高。

EDONE :高有效。在DONE 信號變高的前一個時鐘變為高電平。

DONE :高有效。在FFT 完成后變高,且只存在一個時鐘。在DONE 變高后,IP Core開始輸出計算結果。

BLK_EXP :當使用Burst I/O 結構時可用,若選擇流水線,則此端口無效

OVFLO :算法溢出指示。在數據輸出時,如每幀有溢出,此信號變高。在每幀開始處,此信號重置。

例5.7.1使用IP Core實例化一個16點、位寬為16位的FFT 模塊。

IP Core 直接生成的乘法器的Verilog 模塊接口為:

module fft16(sclr, fwd_inv_we, rfd, start, fwd_inv, dv, scale_sch_we, done, clk, busy, edone, scale_sch,xn_re, xk_im, xn_index, xk_re, xn_im, xk_index);

input sclr , fwd_inv_we, start, fwd_inv, scale_sch_we, clk;

input [3 : 0] scale_sch;

input [15 : 0] xn_re;

output rfd, dv, done, busy, edone;

output [15 : 0] xk_im;

output [3 : 0] xn_index;

output [15 : 0] xk_re;

input [15 : 0] xn_im;

output [3 : 0] xk_index;

……

endmodule

在使用時,直接調用multiply 模塊即可,如

module fft16(sclr, fwd_inv_we, rfd, start, fwd_inv, dv, scale_sch_we, done, clk, busy,

edone, scale_sch, xn_re, xk_im, xn_index, xk_re, xn_im, xk_index);

input sclr , fwd_inv_we, start, fwd_inv, scale_sch_we, clk;

input [3 : 0] scale_sch;

input [15 : 0] xn_re;

output rfd, dv, done, busy, edone;

output [15 : 0] xk_im;

output [3 : 0] xn_index;

output [15 : 0] xk_re;

input [15 : 0] xn_im;

output [3 : 0] xk_index;

fft fft1( // 調用FFT 的IPCore

.sclr(sclr), .fwd_inv_we(fwd_inv_we), .rfd(rfd), .start(start), .fwd_inv(fwd_inv),

.dv(dv), .scale_sch_we(scale_sch_we), .done(done), .clk(clk), .busy(busy),

.edone(edone), .scale_sch(scale_sch), .xn_re(xn_re), .xk_im(xk_im),

.xn_index(xn_index), .xk_re(xk_re), .xn_im(xn_im), .xk_index(xk_index));

endmodule

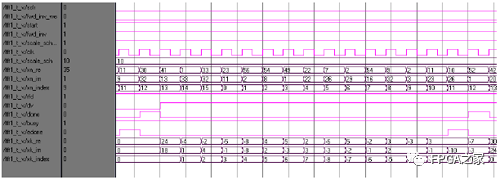

經過仿真測試得到的功能波形圖如圖5-59所示:

圖5-59 FFT的IP core仿真波形

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

EDA工具

+關注

關注

4文章

265瀏覽量

31717 -

FFT

+關注

關注

15文章

434瀏覽量

59315 -

RTL

+關注

關注

1文章

385瀏覽量

59710

原文標題:FPGA開發全攻略——IP核

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA設計的IP和算法應用綜述

FPGA設計的IP和算法應用綜述

評論