精工愛普生公司(TSE: 6724,“愛普生”)開發了一種新的晶體振蕩器差分輸出方案。新方案,寬幅低壓差分信號(WA-LVDS),可以靈活選擇最適合LSI所需的幅值水平的輸出。愛普生計劃在2025財年(從2025年4月開始)將WA-LVDS輸出晶體振蕩器商業化。

隨著數字化的進步,數據流量正在迅速增長,第五代移動通信系統(5G)、物聯網(IoT)和下一代通信系統將需要更快的傳輸速度和更高的容量來支持這些流量。在這種系統中,數據傳輸需要LVDS、LV-PECL和HCSL等通用差分輸出。每一種方案都有自己的特點,工程師們會為他們的特定系統選擇最好的方案。然而,近年來,通信設備對性能的要求越來越高,這意味著現在正在設計電路以接收通信設備中使用的lsi的最佳差分輸出。因此,通用差分輸出不能在越來越多的情況下使用。因此,對適合lsi的差分輸出的需求預計將在未來更加強勁。

現有的具有通用差分輸出的LVDS具有比LV-PECL和HCSL更低的電流消耗。然而,另一方面,它也具有較低的幅值,因此抗噪能力較差。為了解決這個問題,愛普生開發了WA-LVDS,這是一種具有可選擇幅度水平的差分輸出,可以靈活使用。WA-LVDS通過使其易于獲得高振幅而增加了抗噪性。它還提供比LV-PECL和HCSL更低的電流消耗。

作為晶體器件的領導者,愛普生將繼續提供滿足各種電子設備和社會基礎設施需求的晶體器件產品。

*:差分輸出是一種信號傳輸方法,其中數據傳輸為極性相反的兩條獨立線路之間的電壓差。差分輸出的優點是數據傳輸頻率高,抗噪能力強。

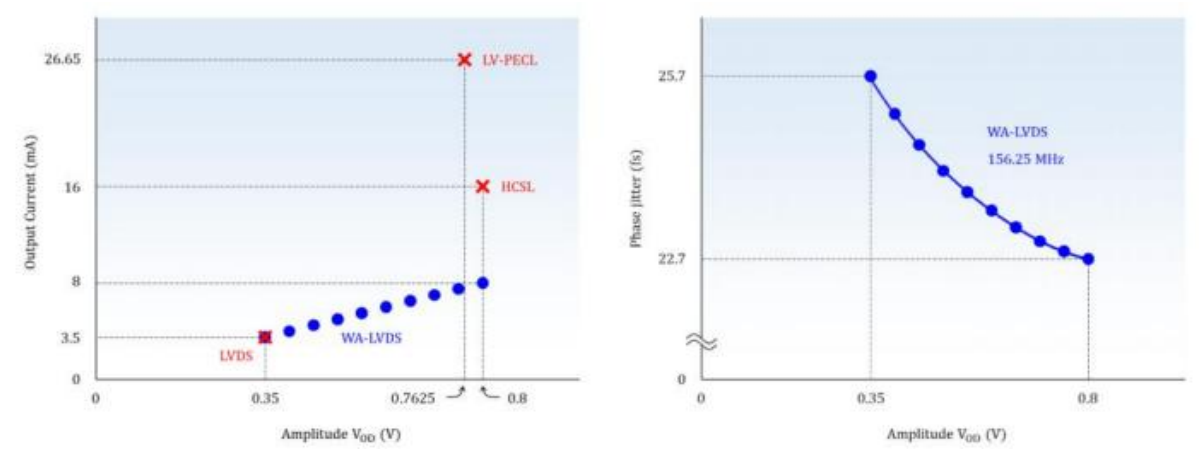

振幅、輸出電流和相位抖動*差分輸出量如圖1和圖2所示。LVDS、LVPECL和HCSL用紅色表示。WA-LVDS是藍色的。

LVDS的H和L水平對應于振幅的差值定義為0.35 V。雖然輸出電流較小,但振幅較低,導致LVDS的抗噪性低于LV-PECL和HCSL。另一方面,LV-PECL和HCSL的振幅較大,但消耗了大量的電流。WA-LVDS的振幅可以以較小的增量進行選擇,從與LVDS相同的水平到與LV-PECL和HCSL對應的水平。此外,WA-LVDS輸出電流保持在較低水平,導致低電流消耗。

圖2

隨著WA-LVDS振幅的增加,相位抖動減小,導致低噪聲的差分輸出。

圖1:振幅vs。差動器的輸出電流圖2:WA-LVDS相位抖動

相位抖動:時鐘周期的波動稱為抖動。相位抖動是對無抖動理想時鐘的邊緣偏差的度量,可以從相位噪聲特性計算出來。

-

lvds

+關注

關注

2文章

1036瀏覽量

65700 -

愛普生

+關注

關注

0文章

304瀏覽量

22120 -

晶體振蕩器

+關注

關注

9文章

616瀏覽量

29057

發布評論請先 登錄

相關推薦

LMK04821輸出幅度隨頻率改變,頻率越高,輸出幅度越小,是什么原因呢?有什么辦法可以增大時鐘幅度呢?

LMK時鐘family LVDS輸出交流耦合設計注意事項

愛普生開發用于大壩和河流泄洪閘設備監測的新型3軸振動傳感器M-A342VD10和M-A542VR10

愛普生開發用于姿態和振動控制的理想IMU

關于愛普生半導體

愛普生LVDS差分晶振MG7050VAN,X1M0004210003高頻振蕩器6G無線晶振

愛普生開發出全新X2A0002710002 XV7011BB陀螺儀傳感器用于高精設備行業

愛普生(EPSON)開發新IMU產品M-G370PDS改善姿態和震動控制

愛普生晶振發布RTC模塊晶振

愛普生為姿態和振動控制開發理想的IMU

愛普生開發新的三軸振動傳感器用于大壩和河流閘門設備監測

愛普生宣布開發出獨特的寬幅度LVDS輸出

愛普生宣布開發出獨特的寬幅度LVDS輸出

評論