隨著片上系統(SoC)設計領域的不斷發展,設計的復雜性與芯片技術的持續進步緊密交織,共同推動著電子設備未來的發展。

為滿足自動駕駛和5G網絡等先進應用對芯片的高要求,半導體晶圓廠紛紛采用復雜的層疊技術和多重光刻等技術,在越來越多的掩膜上實現更多晶體管的布局。這些大型SoC設計的開發過程在多個階段都面臨著挑戰,尤其是在版圖物理驗證這一關鍵階段,由于先進工藝節點(7納米、5納米、3納米等)以及掩模數量的增加使得這一挑戰尤為突出。這一驗證步驟是芯片設計至關重要的里程碑,是芯片流片路上最重要的環節之一。

版圖與原理圖一致性檢查(Layout-versus-Schematic,LVS)是SoC(系統級芯片)開發流程中的關鍵環節,其核心是確保芯片上的邏輯表示與物理實現相吻合。但隨著SoC設計日趨復雜和芯片技術的不斷進步,曾經被認為簡單的LVS如今面臨著重大挑戰。

在審視LVS在芯片開發中作用的變化時,我們將打破一個常規的誤解:即認為LVS僅是芯片開發過程中的一項固定步驟。相反,我們將探討新興LVS工具如何沖破傳統流程的限制,帶來創新的方法論。

應對物理驗證挑戰

現代SoC的開發涉及到多個方面,設計團隊需利用各種工具和方法來應對愈加復雜的設計、更短的設計周期和更多的驗證要求。借助LVS按時完成物理驗證可以有效防止計劃延誤,避免上市時間延長,從而保障芯片的市場競爭力。

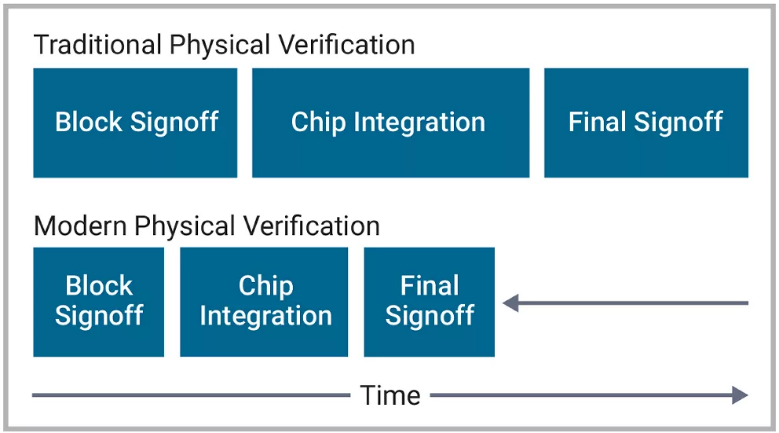

為了將物理驗證提前至設計流程的早期階段,有必要在SoC布線前的多個不同階段進行驗證。一旦SoC的主體部分組裝完畢,LVS檢查就可以與全芯片裝配工作并行啟動。現代LVS工具需能夠最初在宏觀/IP/模塊層面上運行,并迅速評估整個芯片設計的狀態,提供有價值且可操作的反饋,使開發者能夠及時解決問題。

▲加速SoC物理驗證簽核

在大規模電路設計的背景下,LVS流程耗時數十小時甚至數日都是常有的情況。根據設計的清晰度,通常涉及到多次迭代,包括調試錯誤、糾正設計以及重復進行LVS的過程。鑒于現代電路設計的復雜性,即使對于經驗豐富的開發者來說,管理這一反復的過程也證明是充滿挑戰且耗時的。

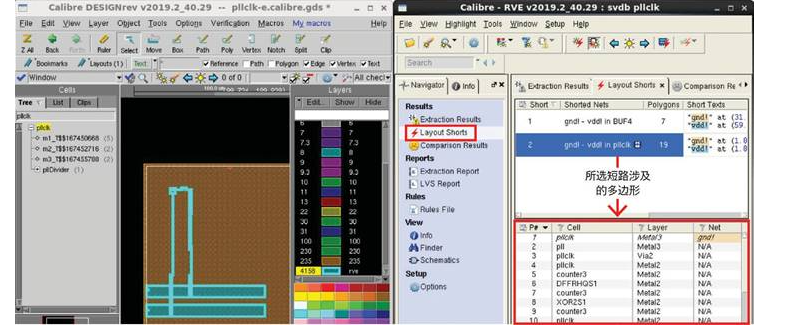

在芯片項目的最后階段,執行LVS、調試以及迭代的復雜性往往是導致進度延誤的主要原因。當LVS首次在整合了所有設計組件的布局上運行時,這一挑戰會變得更加嚴峻,因為這一階段可能會揭露之前合并過程中未曾顯現的眾多新問題。這些問題可能包括IP的挑戰、接口引腳對齊錯誤、頂層短路、集成錯誤等等。

創新型全芯片LVS檢查工具:加速驗證流程,提升設計效率

面對這些挑戰,新思科技推出了搭載Explorer LVS技術的創新型新思科技IC Validator。這款現代LVS工具可以在早期完整芯片LVS運行中快速識別問題的根本原因,為更高效、更可靠的驗證流程鋪平道路,從而支持數十億個晶體管的超大型芯片設計。

LVS可以在設計和驗證周期的任何階段使用,但效益最大化的時機是在完成全芯片集成后立即運行它,這時通常可以檢查出最意想不到的問題。在第一階段,工具啟動基于文本的短路檢測并剔除等效單元。第二階段進行連通性不匹配和開/短路檢測。此外,它還會標定等效單元以便提取,并進行黑盒測試對比。在最后階段,將進行全面的LVS檢查,提取所有層次和數據,執行全方位對比分析。

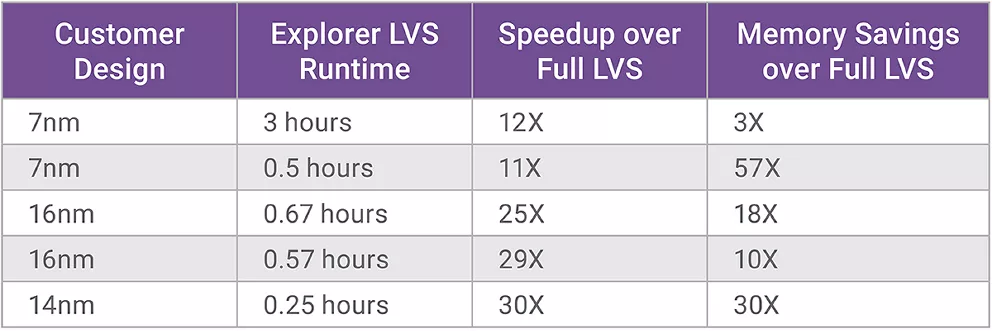

開發者可以利用摘要報告來評估全芯片設計的整體質量,確保設計已經準備好簽核,且所有錯誤已被排除。如果在簽核之前出現臨時更新,Explorer LVS能夠確保設計的完整性不受影響。與傳統工具相比,這個工具能幫助客戶以多達30倍速度加快運行,減少多達30倍內存用量。

▲Explorer LVS的實際性能表現

用現代化LVS工具,更早更自信地流片

隨著芯片技術的不斷進步和對更高性能電子設備的不懈追求,理解LVS不斷演變的角色,并將其盡可能地向設計流程的前端移動,已成為設計團隊的首要任務。盡早對全芯片進行LVS檢查,快速自動地定位根本原因,不僅能縮短產品上市時間,還能為創新留出更多空間。借助現代化的LVS工具,SoC開發者能夠在確信已經識別并解決了所有LVS問題的情況下,更早地自信地完成流片。

審核編輯:劉清

-

晶體管

+關注

關注

77文章

9634瀏覽量

137850 -

片上系統

+關注

關注

0文章

185瀏覽量

26779 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34870 -

LVS

+關注

關注

1文章

35瀏覽量

9922 -

自動駕駛

+關注

關注

783文章

13684瀏覽量

166150

原文標題:你的芯片驗證夠快夠準嗎?新一代全芯片LVS,runtime提速30倍

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于功能驗證、時序驗證、形式驗證、時序建模的論文

Mentor工具簡介Calibre物理驗證系列

芯片設計完整流程及工具

芯片設計流程及工具

數字芯片設計流程

用Hercules完成物理驗證的詳細流程

基于Cadence軟件DRACULA工具的LVS檢查

國產EDA驗證調試工具實現破局 助力芯片設計效率提升

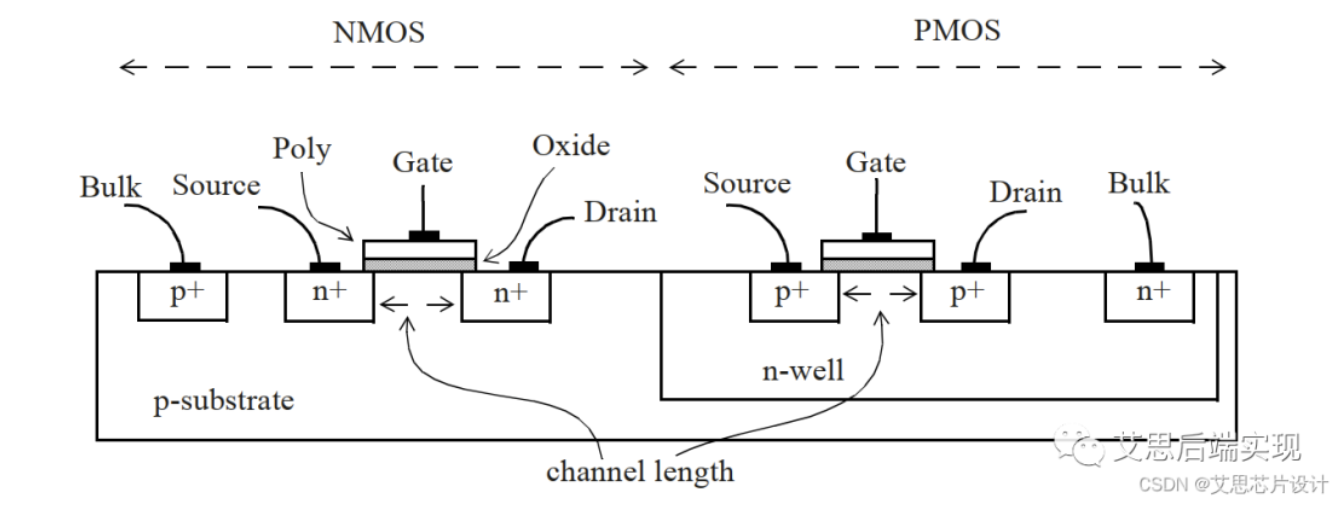

物理驗證LVS對bulk(體)的理解和處理技巧

芯華章發布國內首臺超百億門大容量硬件仿真系統 完備數字驗證全流程工具平臺

英諾達EnCitius? SVS新功能發布,加速芯片驗證流程

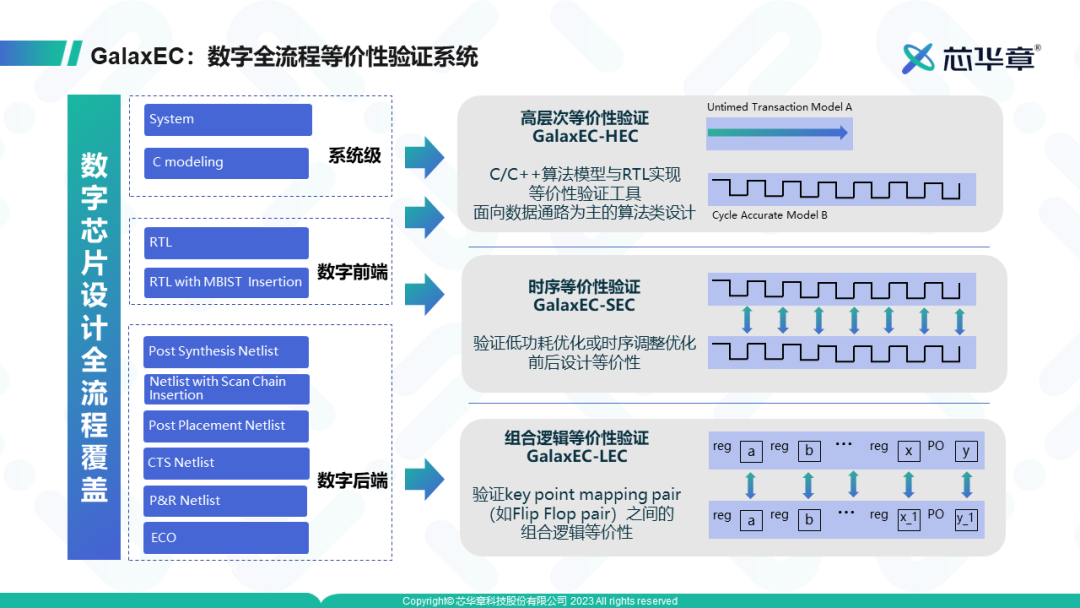

打通系統到后端,芯華章發布首款自研數字全流程等價性驗證工具

創新型全芯片LVS檢查工具:加速驗證流程,提升設計效率

創新型全芯片LVS檢查工具:加速驗證流程,提升設計效率

評論