FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。以下是FPGA原型驗證流程的詳細步驟:

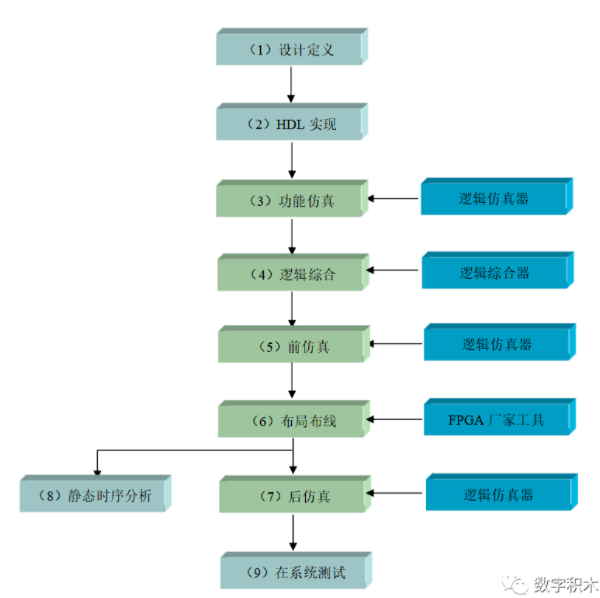

首先,進行FPGA設計。這包括使用專業的硬件描述語言(如Verilog或VHDL)將硬件原型的功能轉化為FPGA代碼。設計過程需要充分考慮硬件資源的利用、性能優化以及可維護性等因素。

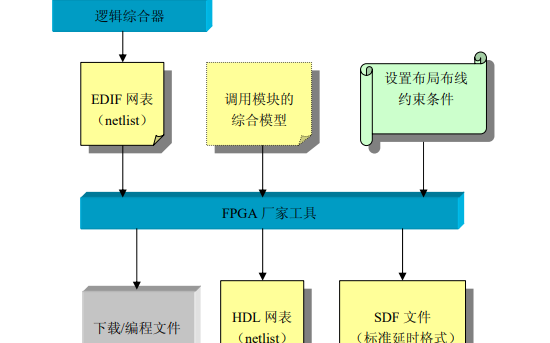

接著,將設計好的FPGA代碼加載到FPGA開發板或模擬器中。這通常涉及到使用特定的編程工具將代碼編譯并下載到FPGA芯片中。

隨后,進行功能驗證。驗證過程主要包括測試FPGA的各個功能模塊是否按照預期工作。這可以通過編寫測試程序、使用調試工具或構建測試平臺來完成。驗證人員需要設計一系列的測試用例,覆蓋FPGA設計的所有功能和邊界條件,以確保設計的完整性和正確性。

在驗證過程中,還需要關注FPGA與外部接口的通信和數據傳輸。這包括驗證FPGA與其他硬件組件(如傳感器、執行器等)的接口連接是否正確,數據傳輸是否穩定可靠。

此外,性能驗證也是FPGA原型驗證流程中的重要環節。驗證人員需要評估FPGA設計的性能表現,包括處理速度、資源利用率、功耗等指標。這有助于發現設計中可能存在的性能瓶頸或優化空間。

最后,進行問題定位和修復。如果在驗證過程中發現任何功能或性能問題,驗證人員需要定位問題的原因并進行修復。這可能涉及到修改FPGA代碼、調整硬件資源分配或優化接口設計等。

總的來說,FPGA原型驗證流程是一個復雜而嚴謹的過程,它確保了FPGA設計的正確性和功能性,為后續的硬件實現和應用部署提供了堅實的基礎。

-

FPGA

+關注

關注

1620文章

21507瀏覽量

598845 -

原型驗證

+關注

關注

0文章

21瀏覽量

10711 -

開發板

+關注

關注

25文章

4765瀏覽量

96139

發布評論請先 登錄

相關推薦

fpga原型驗證流程

fpga原型驗證流程

評論