優(yōu)秀網文分享,作者:百芯 EMA

今天給大家分享的是:混合PCB 布局技巧,包括:組件放置、電路板分層,接地等注意事項。

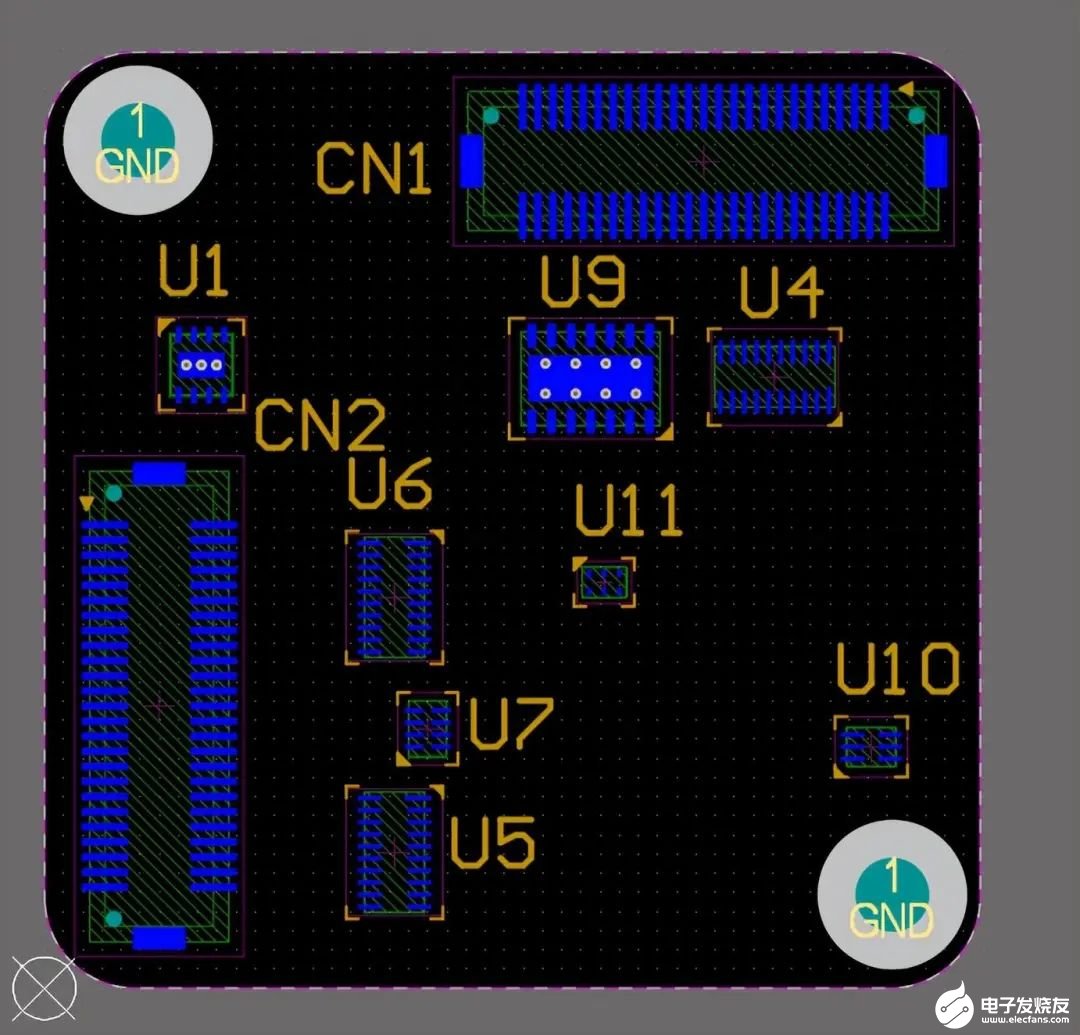

一、元器件放置

在元器件放置的時候要遵循原理圖的信號路徑,還需要為走線提供空間。除此之外,要遵循以下放置規(guī)則:

電源部分應緊湊地放置在一起,并適當?shù)娜ヱ顚崿F(xiàn)電源完整性

去耦電容應盡可能靠近各個器件放置

連接器應放置在板的邊緣

遵循高頻組件的原理圖流程

大型存儲設備和處理器(例如時鐘發(fā)生器和控制器)應放置在電路板的中心

元器件放置

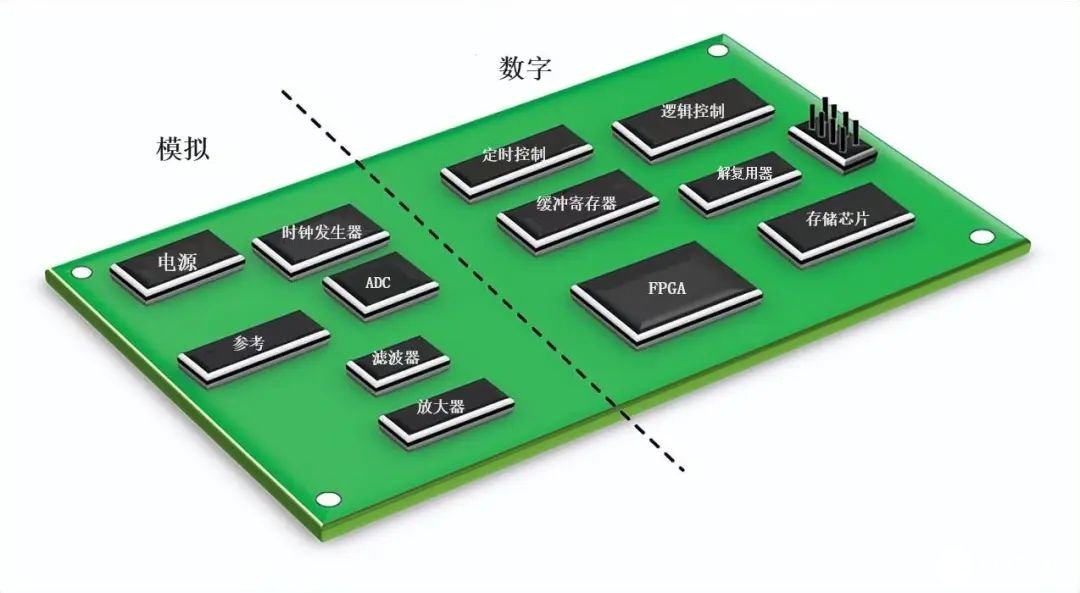

二、模擬和數(shù)字模塊分離

為了最大限度地減少模擬和數(shù)字信號的公共返回路徑,要將模擬和數(shù)字模塊分開,防止模擬信號與數(shù)字信號混合。

模擬和數(shù)字電路分離

上圖顯示了模擬和數(shù)字電路分離的一個示例。在劃分模擬部分和數(shù)字部分時,應牢記以下幾點:

建議在模擬平面安裝精密的模擬元件,例如放大器和基準電壓源。另一側/數(shù)字平面必須用于噪聲數(shù)字組件,例如邏輯控制和定時塊。

系統(tǒng)中的模數(shù)轉換器 (ADC) 或數(shù)模轉換器 (DAC) 是混合信號且具有低數(shù)字電流,其處理方式與模擬組件在模擬系統(tǒng)中的處理方式類似。

對于具有大量高電流 ADC 和 DAC 的設計,建議將模擬電源和數(shù)字電源分開。換句話說,DVDD應該連接到數(shù)字部分,而AVCC必須連接到模擬部分。

微處理器和微控制器產生的空間和熱量可能很大。為了改善散熱,這些組件必須放置在電路板的中心,并且必須靠近它們要連接的電路塊。

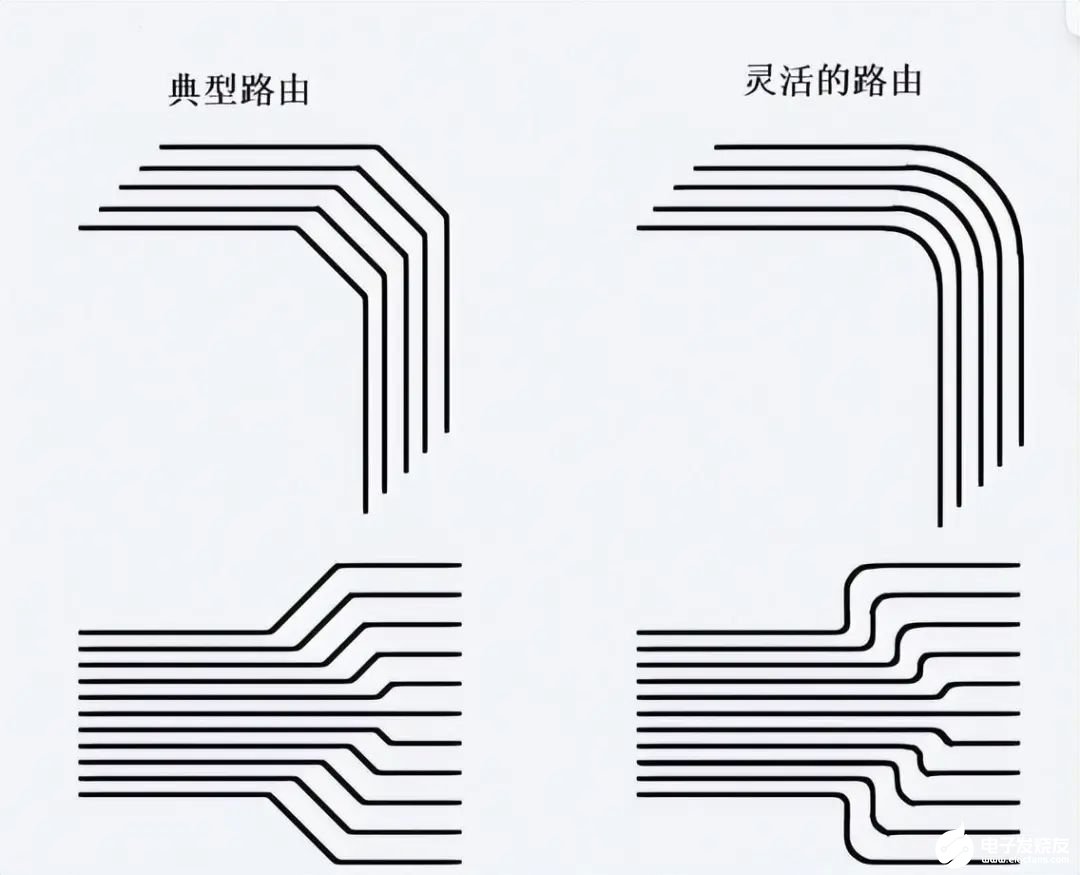

三、跟蹤路由

將所有組件正確放置在最佳位置并建立適當?shù)慕拥仄矫婧螅蠖鄶?shù)路線自然會遵循正確的路徑。但是,在跟蹤路由時應牢記以下準則:

信號路徑應盡可能直接且短

具有高速信號路徑的層應有一個與其相鄰的接地層,以確保正確的返回信號

高速電路特別敏感,需要遵循原理圖中布置的信號路徑

通過使用短、直接和寬的走線來減少電源布線中的電感

在布線走線和過孔時不要創(chuàng)建天線

電源布線應該短、緊湊并且應該有寬走線

布線需要保持數(shù)字和模擬電路元件之間的隔離

接地很重要,特別是對于連接數(shù)字和模擬分區(qū)區(qū)域的走線

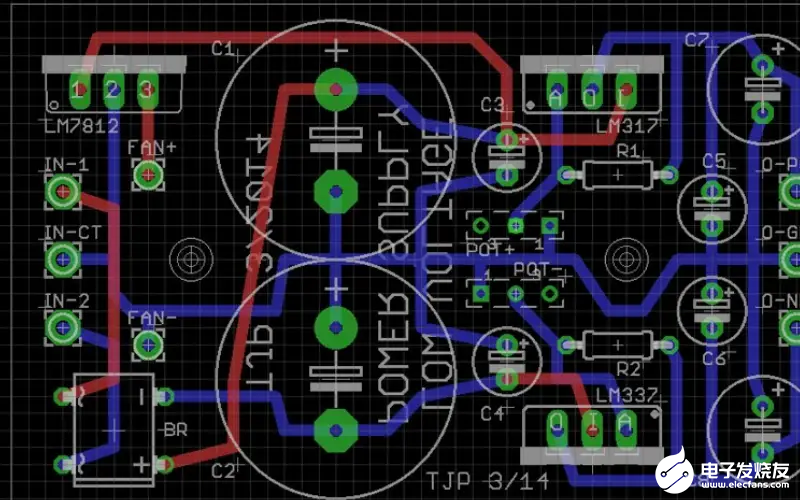

四、電源模塊

電源是電路的重要組成部分,需要小心處理。一般來說,電源模塊必須靠近其供電的組件,同時與電路的其余部分隔離。

當復雜系統(tǒng)中的設備具有許多電源引腳時,可以為模擬和數(shù)字部分使用專用電源模塊,以防止噪聲數(shù)字干擾。

為了減少電感并防止電流限制,電源線應短而直,并使用寬走線。

電源模塊

五、解耦

為了滿足系統(tǒng)所需的性能,工程師必須考慮的關鍵因素之一是電源抑制比 (PSRR)。設備的性能最終由 PSRR 決定,PSRR 評估設備對電源變化的敏感度。

為了保持理想的 PSRR,需要防止高頻能量進入器件。為此,使用電解電容和陶瓷電容的組合,可以有效地將器件電源與高阻抗接地層隔離。

有效去耦是為了在電路運行時有一個低噪聲環(huán)境。基本規(guī)則是提供盡可能最短的路徑,使電流更容易返回。

下面為一些通用解耦方法:

低電感陶瓷電容用于降低高頻噪聲,而電解電容則通過充當瞬態(tài)電流的電荷庫來降低電源上的低頻噪聲。此外,鐵氧體磁珠是可選的,但可以增強高頻噪聲的隔離和去耦。

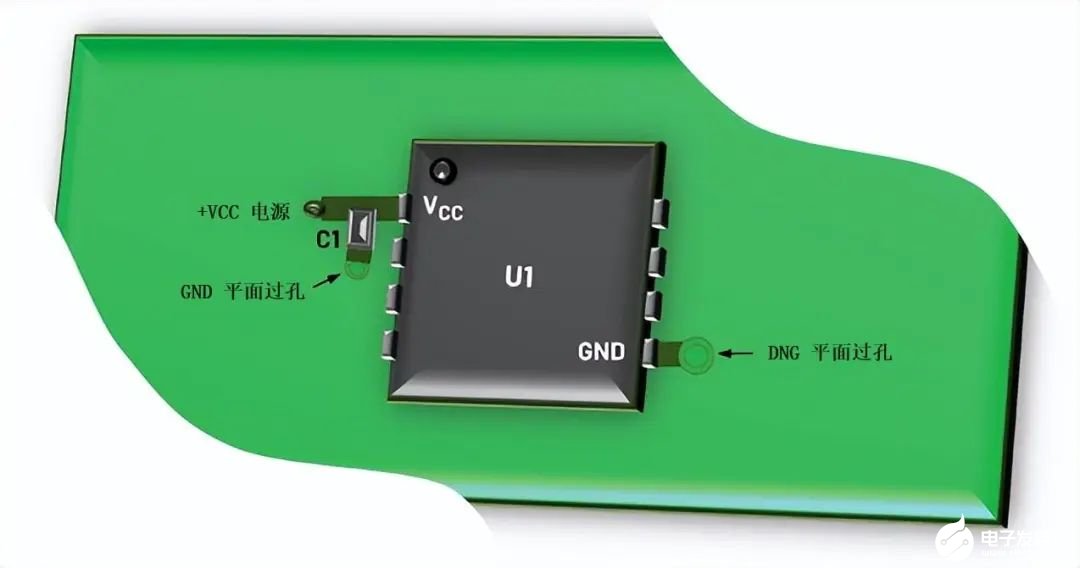

去耦電容需要盡可能靠近器件的電源引腳放置。為了減少額外的串聯(lián)電感,應使用過孔或短線將這些電容連接到低阻抗接地層的大部分。

器件的電源引腳應盡可能靠近器件。應使用較小的電容(通常為 0.01F 至 0.1F),這種配置避免了當多個輸出同時切換時設備以不穩(wěn)定的方式運行。電解電容與設備電源引腳之間的距離不應超過一英寸(平均10F至100F)。

可以使用靠近器件 GND 引腳的過孔將去耦電容T形連接到接地層,以簡化結構而不是構建走線。

具體的可以看下圖:

電源引腳的去耦技術

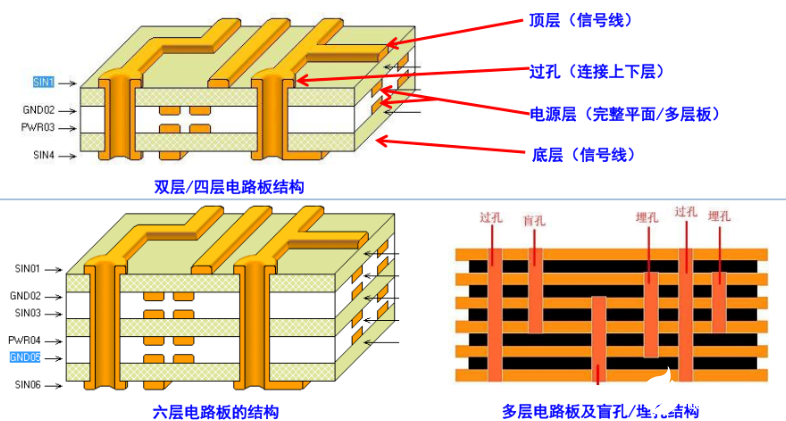

六、PCB 分層

在PCB布線之前,要考慮好 PCB 的疊層,不然會影響系統(tǒng)設計允許的返回路徑。

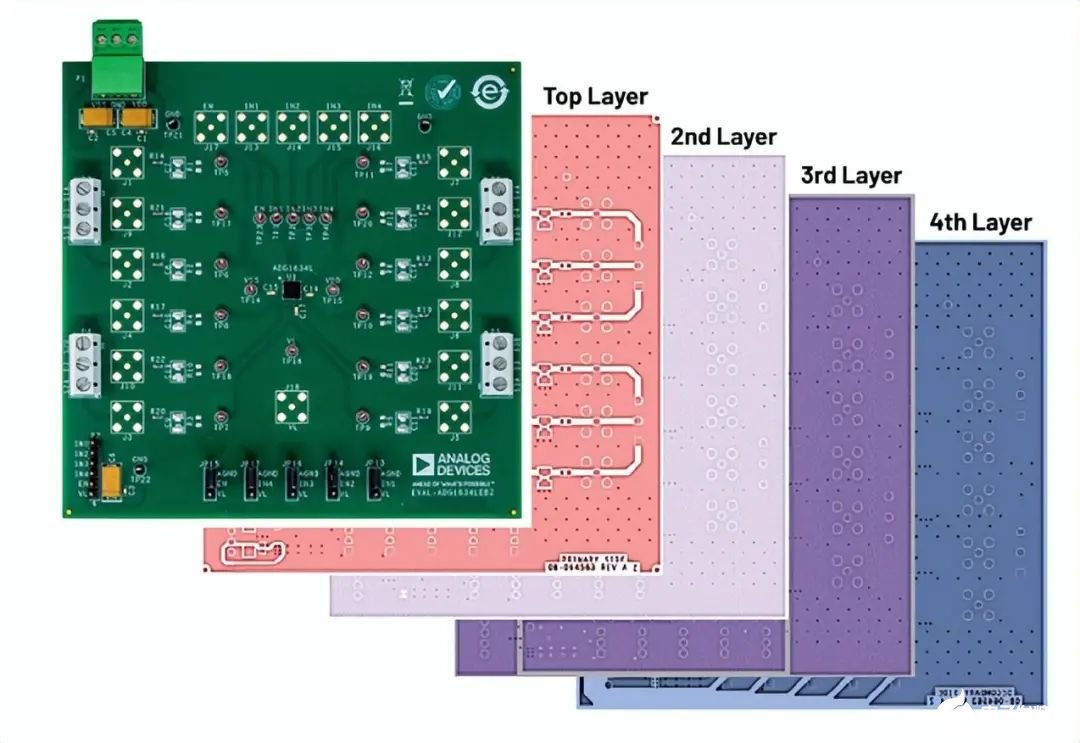

4 層 PCB 示例

上圖 顯示了電路板各層的直觀表示。下圖詳細介紹了典型 PCB 的設置:

典型 PCB圖層

高性能數(shù)據(jù)收集系統(tǒng)通常應包含四層或更多層。輔助信號通常用在底層,而數(shù)字/模擬信號通常用在頂層。通過充當阻抗控制信號的參考層,第二層(也稱為接地層)可降低 IR 壓降并保護頂層的數(shù)字信號。電源層位于第三層。

由于它們提供了額外的層間電容,電源層和接地層必須彼此靠近,以便電源在高頻下解耦。

優(yōu)秀網文分享,作者:百芯 EMA

七、PCB 銅電阻

銅的電阻在混合信號 PCB 布局中也很重要,銅走線可以形成良好的互連和接地層。

大多數(shù) PCB 使用 1 oz 銅,但高功率部分可能使用 2 或 3 oz銅。25℃時銅的電阻率為1.724X10 -6 Ω/cm。

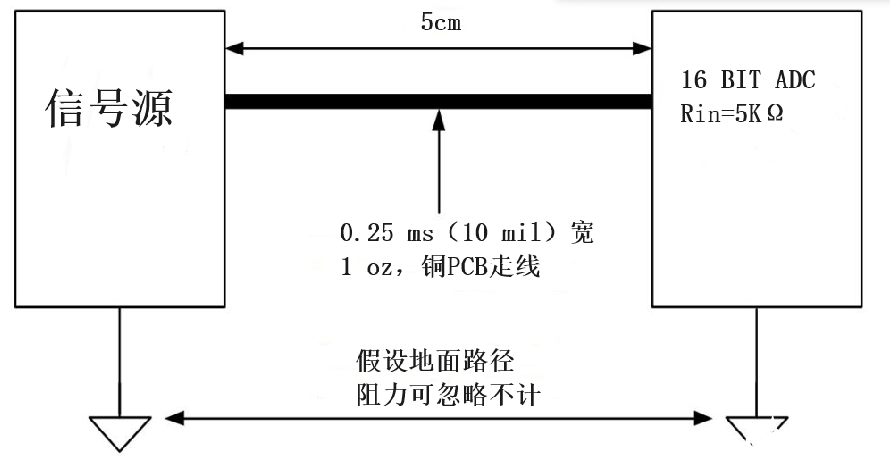

常見的1盎司銅箔厚度為0.036 mm(0.0014in),電阻為0.48 mΩ/平方。例如,PCB 上常用的 0.25 mm(10 mil)寬走線的電阻/長度約為 19 mΩ/cm(48 mΩin)。

PCB 走線電阻可能是混合信號 IC 的誤差源。對于具有 5 kΩ 輸入電阻的 16 位 ADC,通過 5 cm 0.25 mm寬的 1 oz銅驅動,軌道電阻為 0.1 Ω,并與 5 kΩ 負載形成分壓器,產生 0.1 的誤差/5 k(約 0.0019%),高于 16 位的 1 LSB (0.0015%),如下所示:

PCB 走線電阻是混合信號 PCB 中的一個重要因素

在實際應用中可能更嚴重,因為這忽略了返回路徑和 25 °C 時銅的 0.4%/°C 溫度系數(shù)。在處理低阻抗精密電路時,銅的電阻對于成功的設計至關重要。

八、接地

1、單接地層

最好的辦法是對具有單個低數(shù)字電流 ADC 或 DAC 的混合信號系統(tǒng)使用單個實心接地層。

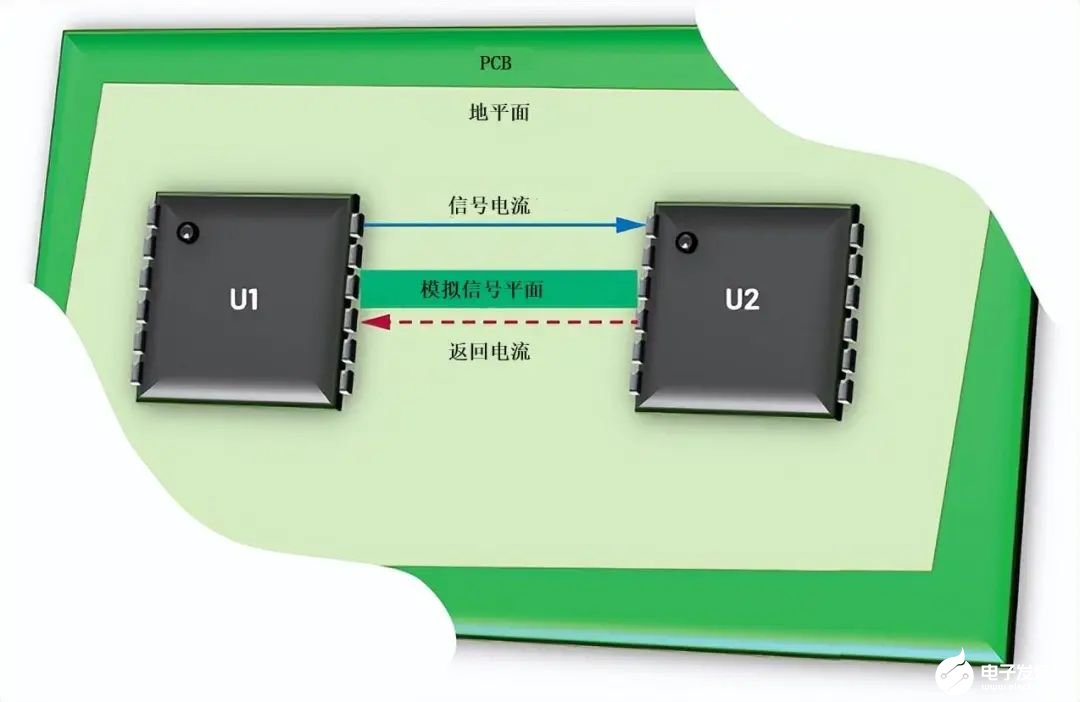

為了理解單個接地層的重要性,這里需要分析返回電流。術語“返回電流”描述了完成電路環(huán)路并流回地的電流。整個 PCB 布局中必須遵循每個返回路徑,以避免混合信號干擾。

使用實心接地層的系統(tǒng)的返回電流

上圖的簡單電路說明了單個實心接地層相對于多個接地層的優(yōu)勢。存在與信號電流相等但相反的返回電流。當返回電流返回接地層中的源時,該返回電流將采用電阻最小的路徑。

電阻最小的路線(通常是設備接地參考之間的直線)將跟隨低頻傳輸?shù)姆祷仉娏鳌H欢徊糠址祷仉娏鲗L試沿著信號通道返回以進行更高頻率的傳輸。這是因為沿該通道的輸出和返回電流之間產生的阻抗較低且環(huán)路較小。

2、獨立的模擬地和數(shù)字地

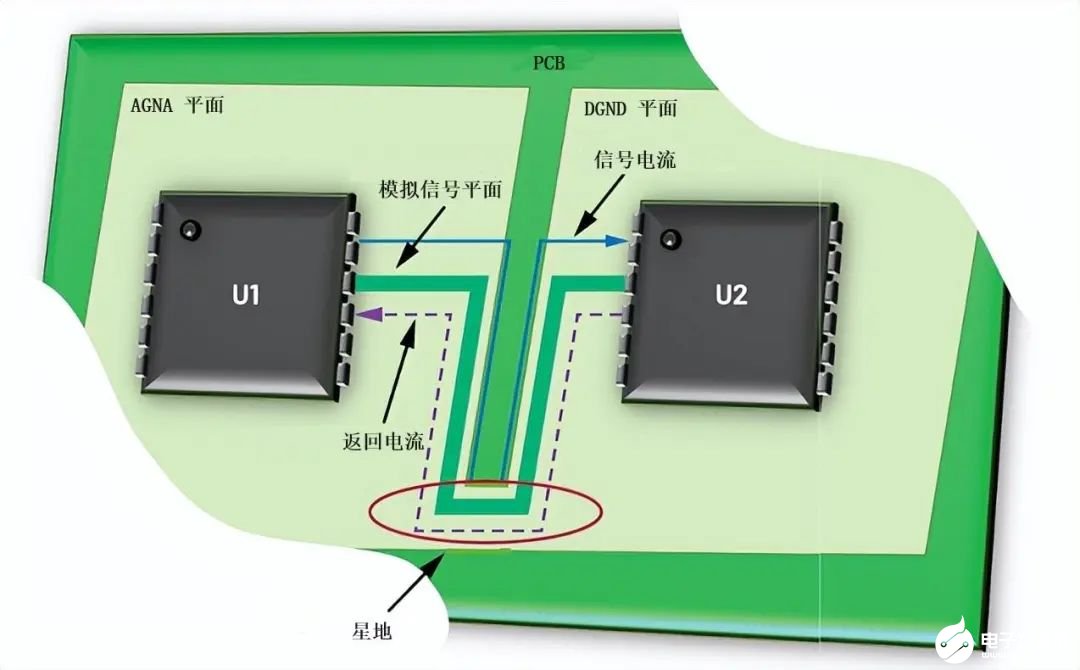

另一種典型的策略是將接地層分為兩半:模擬接地層和數(shù)字接地層。這適用于具有大量混合信號組件和高數(shù)字電流要求的更復雜的系統(tǒng)。下圖顯示了具有劃分接地層的系統(tǒng)的圖示。

使用分離接地層的系統(tǒng)的返回電流

消除接地層斷裂并允許返回電流采取更直接的路徑,通過星形接地結流回,是為具有單獨接地層的系統(tǒng)實現(xiàn)整體接地的最簡單方法。在混合信號布局中,模擬和數(shù)字接地層的交叉點稱為星形接地。

星形接地可以連接到常見系統(tǒng)中模擬和數(shù)字接地層之間的典型薄連續(xù)連接。對于更復雜的系統(tǒng),通常通過將跳線分流到接地連接來執(zhí)行星形接地。

由于星形接地沒有電流,因此不需要高載流接頭和跳線分流器。星形接地的主要功能是保證兩個接地的參考電平相同。

另一方面,由于星形接地還在一個位置連接兩個接地,因此具有 AGND 和 DGND 引腳的混合信號器件可以連接到各自的接地層。這將精密的模擬電路與高噪聲數(shù)字電流分開,這些電流通過數(shù)字電源,一直到達數(shù)字接地層,然后返回數(shù)字電源。

多層 PCB 必須實現(xiàn) AGND 和 DGND 平面的完全隔離。

九、電磁干擾屏蔽

在解決了接地反彈、串擾、電源噪聲和其他干擾之后,電路扔可能遭受電磁干擾或 EMI。這可能會導致各種問題,例如:

無線通信的干擾

通訊中斷

傳感器數(shù)據(jù)損壞

部件故障

軟件錯誤和故障

處理 EMI 的有效方法之一是使用足夠量的金屬屏蔽。優(yōu)選地,屏蔽應形成法拉第籠,從所有六個側面和接地層覆蓋電路。

盡管使用屏蔽可以阻止大部分傳入的 EMI,還必須解決熱冷卻問題,并允許信號輸入和輸出。

優(yōu)秀網文分享,作者:百芯 EMA

來源地址:

https://www.toutiao.com/article/7280802445142409787/

如果看到這里,請點贊、收藏、分享三連!

限時免費掃碼進群,交流更多行業(yè)技術

審核編輯 黃宇

-

pcb

+關注

關注

4292文章

22761瀏覽量

393134 -

模擬

+關注

關注

7文章

1416瀏覽量

83821 -

電源模塊

+關注

關注

32文章

1632瀏覽量

92293 -

數(shù)字信號

+關注

關注

2文章

918瀏覽量

47427 -

布局

+關注

關注

5文章

238瀏覽量

24944

發(fā)布評論請先 登錄

相關推薦

pcb設計中布局的要點是什么

關于PCB布局布線技巧的104的問題

pcb布局的基本原則

PCB高級設計系列講座教案

PCB布局規(guī)則與技巧分享

關于PCB布局和布線的設計技巧

PCB設計如何在實操中規(guī)范的布局

9種 混合PCB 布局技巧總結,圖文結合+實例

9種 混合PCB 布局技巧總結,圖文結合+實例

評論