10M/100M/1000M自協(xié)商基理

10M/100M/1000M自協(xié)商,主要協(xié)商的內(nèi)容為“速度雙工”、“流控”和“主從”三大類,下面先介紹10M/100M/1000M自協(xié)商的BasePage和NextPage的bits分配,然后就這三大類內(nèi)容進(jìn)行闡述。

10M/100M/1000M自協(xié)商交互方式

1000BASE-T PHY(無EEE能力時(shí))按順尋地不間斷地交換一個(gè)自動(dòng)協(xié)商基本頁、一個(gè)1000BASE-T格式的下一頁,和兩個(gè)1000BASE-T未格式化的下一頁;1000BASE-T PHY(有EEE能力時(shí))按順尋地不間斷地交換一個(gè)自動(dòng)協(xié)商基本頁、一個(gè)1000BASE-T格式的下一頁,兩個(gè)1000BASE-T未格式化的下一頁,一個(gè)1000BASE-T格式的下一頁,和一個(gè)1000BASE-T未格式化的下一頁;

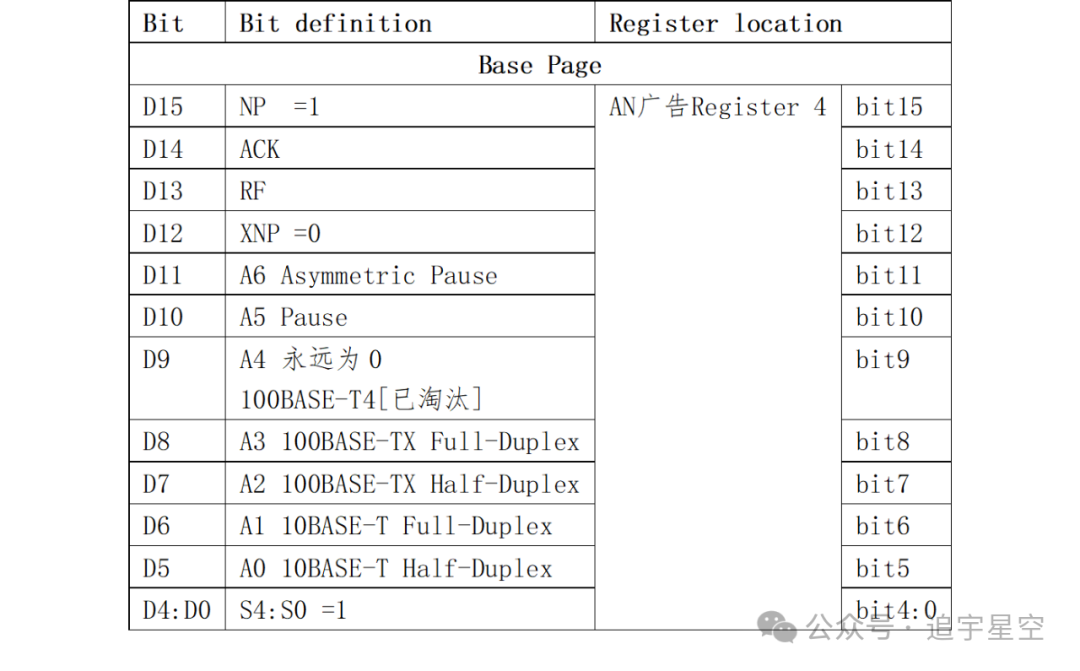

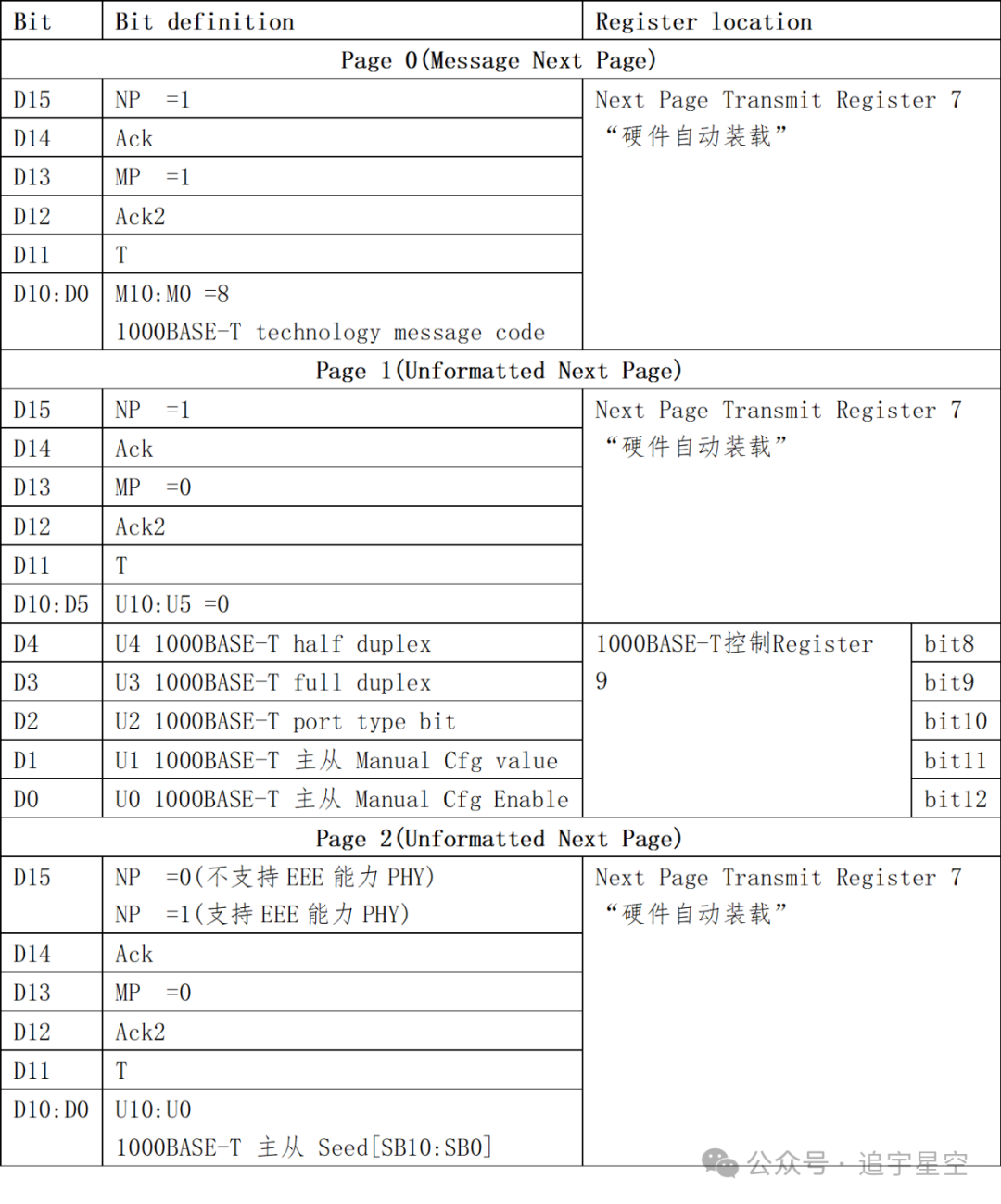

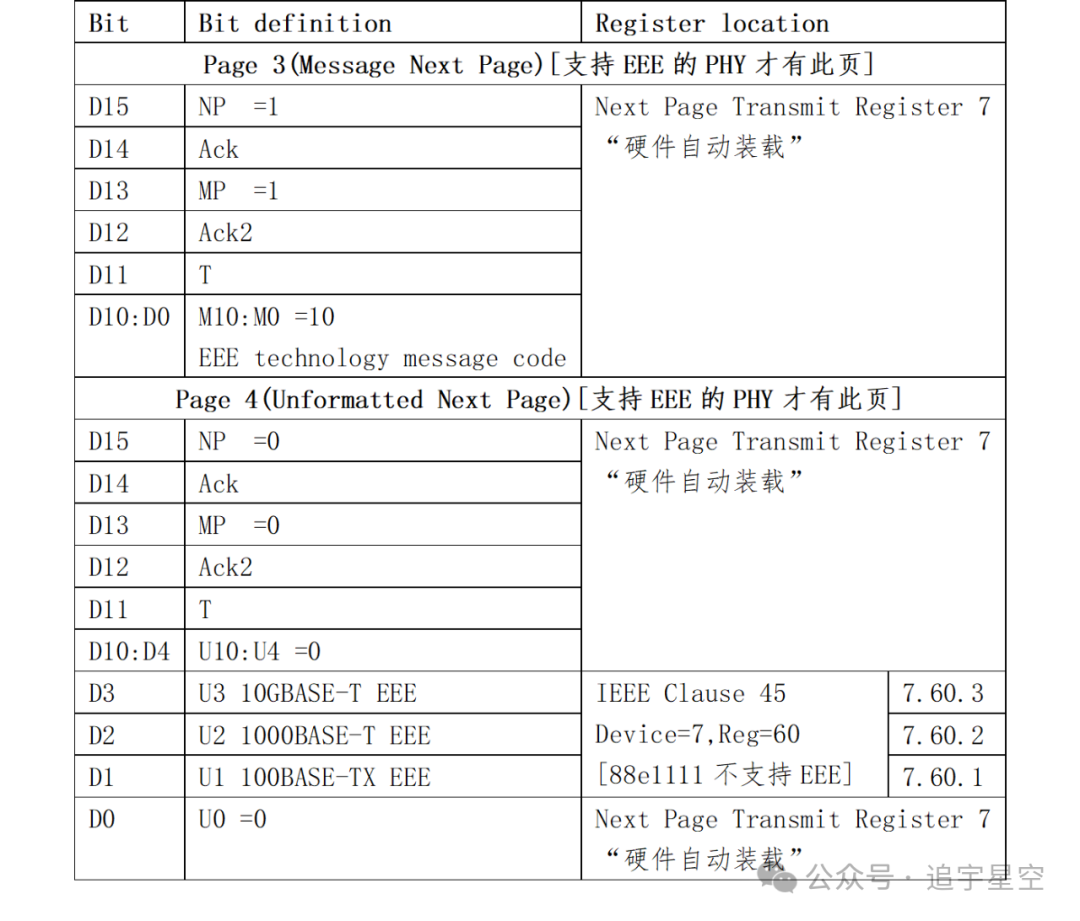

1000BASE-T BasePage和NextPage編碼格式分別如下圖:

速度雙工協(xié)商

速度雙工協(xié)商主要靠設(shè)置“本地廣告能力寄存器Auto-NegotiationAdvertisement Register Register 4”的bit9:5和“本地控制寄存器1000BASE-T Control Register Page 0, Register 9”的bit9:8實(shí)現(xiàn)的。下面為描述問題方便,把Reg 9.bit9:8+Reg 4.bit9:5合并為T[11:5].本端和遠(yuǎn)端選擇彼此都有的能力(T[11:5]中的置1的相關(guān)bit)中優(yōu)先級(jí)高的那種能力作為本端PHY和遠(yuǎn)端PHY的實(shí)際工作的速度雙工狀態(tài)。

PHY能力優(yōu)先級(jí)由高到低排序如下:

1000BASE-Tfull duplex

1000BASE-T half duplex[沒有芯片支持]

100BASE-T2 full duplex[已淘汰]

100BASE-TX full duplex

100BASE-T2[已淘汰]

100BASE-T4[已淘汰]

100BASE-TX half duplex

10BASE-T full duplex

10BASE-T half duplex

下面分為“本端遠(yuǎn)端均為千兆PHY”和“一端為千兆PHY,另一端均為百兆PHY”兩種情況討論。

“本端遠(yuǎn)端均為千兆PHY”:

例子1:本端PHY的T[11:5]=2b1001111;雙絞線另一側(cè)的遠(yuǎn)端PHY的T[11:5]=2b0000101。此時(shí)他倆的彼此能力的交集為PHY的T[11:5]=2b0000101,即雙絞線鏈路雙方都支持的PHY能力為T[5]=1(10BASE-T half duplex)和T[7]=1(100BASE-TX half duplex),并且因?yàn)閮?yōu)先級(jí)順序?yàn)?00BASE-TX half duplex>10BASE-T half duplex,故此時(shí)本端和遠(yuǎn)端速度雙工自協(xié)商的結(jié)果為“100BASE-TX half duplex”;

例子2:本端PHY的T[11:5]=2b1001111;雙絞線另一側(cè)的遠(yuǎn)端PHY的T[11:5]=2b1001010。此時(shí)他倆的彼此能力的交集為PHY的T[11:5]=2b1001010,即雙絞線鏈路雙方都支持的PHY能力為T[6]=1(10BASE-T full duplex)、 T[8]=1(100BASE-TX full duplex)和T[11]=1(1000BASE-T full duplex),并且因?yàn)閮?yōu)先級(jí)順序?yàn)?000BASE-Tfull duplex >100BASE-TX full duplex>10BASE-T full duplex,故此時(shí)本端和遠(yuǎn)端速度雙工自協(xié)商的結(jié)果為“1000BASE-T full duplex”;

例子3:本端PHY的T[11:5]=2b1000000;雙絞線另一側(cè)的遠(yuǎn)端PHY的T[11:5]=2b0001111。此時(shí)他倆的彼此能力的交集為PHY的T[11:5]=2b0000000,即雙絞線鏈路雙方?jīng)]有PHY能力交集,故此時(shí)本端和遠(yuǎn)端永遠(yuǎn)無法建立正確鏈接。

寫到這里,可能有小伙伴感覺到疑惑,既然88e1111 PHY的“本地控制寄存器1000BASE-T Control Register Page 0, Register 9”的bit8(1000BASE-T half duplex)可設(shè)置為1,為什么說芯片均不支持1000BASE-T half duplex呢?筆者曾經(jīng)實(shí)踐多款不同廠家的PHY(broadcom,marvell,vitesse,realtek,micrel等),發(fā)現(xiàn)即使本端和遠(yuǎn)端的該能力bit均置1,但是實(shí)測(cè)效果是1000BASE-Thalf duplex模式實(shí)際并未生效,為避免產(chǎn)生不必要的混淆,建議驅(qū)動(dòng)工程師將此bit永遠(yuǎn)初始化0。其實(shí)芯片廠家普遍選擇不實(shí)現(xiàn)1000BASE-T half duplex是合乎情理的。我們知道以太網(wǎng)PHY半雙工的技術(shù)需求主要是20年前,因?yàn)楫?dāng)年LAN主要是基于集線器組網(wǎng)(集線器基于總線廣播模式而非地址表交換模式),并且當(dāng)年的計(jì)算機(jī)的CPU能力普遍孱弱,硬件無環(huán)境無法支持全雙工的應(yīng)用。

而在進(jìn)入1000BASE-T時(shí)代(大概是2007年)后,集線器已經(jīng)被性能優(yōu)越的交換機(jī)(基于SRAM地址表架構(gòu)的交換機(jī)天生支持全雙工能力)完全取代,同時(shí)計(jì)算機(jī)的CPU的處理性能極大飛躍,故此時(shí)此刻半雙工的需求不復(fù)存在。所有廠家就沒有花額外的成本去支持1000BASE-T half duplex必要。(還有另外一個(gè)原因,理論上如果支持基于CSMA/CD的1000BASE-T半雙工200米的沖突域的需求,以太網(wǎng)的最小幀長(zhǎng)要從64Byte提高到512Byte,這樣的變動(dòng)的歷史代價(jià)太大)。

“一端為千兆PHY,另一端均為百兆PHY”:

千兆PHY通過“LinkPartner Ability Register - Base Page, Copper Page 0, Register 5”的bit15獲知雙絞線的另一端為百兆PHY(bit15 NextPage=0),故千兆PHY也只支持BasePage發(fā)送(此時(shí)NextPage永遠(yuǎn)不對(duì)外發(fā)送)。那當(dāng)前的情況就完全等同于10M/100M自協(xié)商了,該部分在“10M/100M自協(xié)商基理”章節(jié)已闡述過,故這里就不再贅述了。

流控協(xié)商

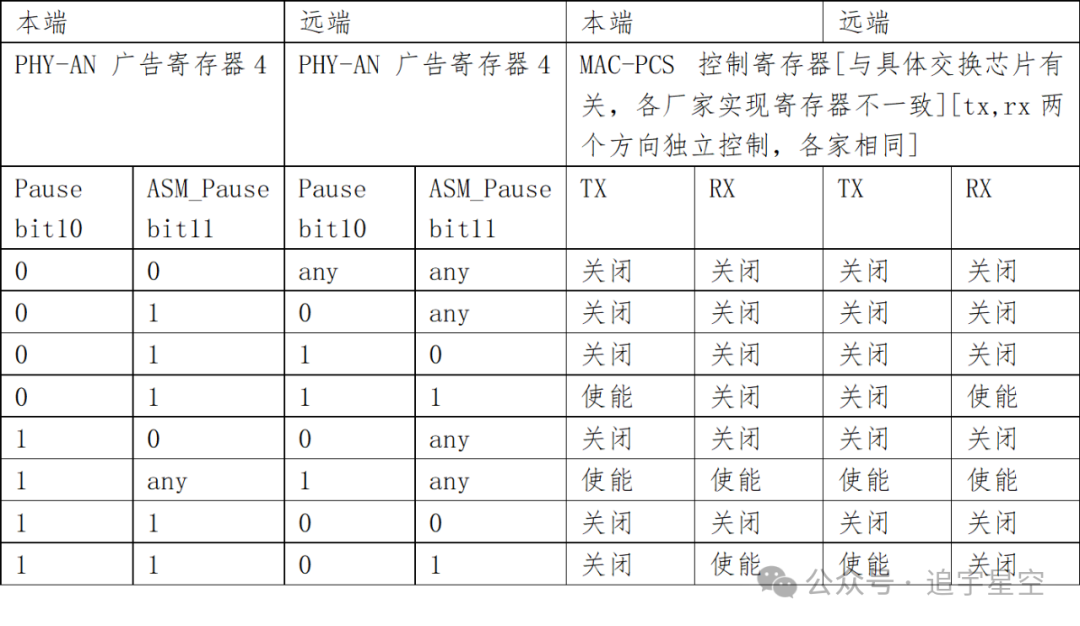

流控主要靠設(shè)置“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit11:10實(shí)現(xiàn)的。軟件通過本端和遠(yuǎn)端的bit11:10的各種組合進(jìn)行對(duì)本端MAC的tx和rx方向的802.3流控進(jìn)行設(shè)置,具體規(guī)則如下表:

“MAC-PCS控制寄存器”需要軟件根據(jù)“PHY-AN廣告寄存器”和“PHY-AN LP廣告狀態(tài)寄存器”的內(nèi)容進(jìn)行動(dòng)態(tài)更新配置,交換芯片硬件并不會(huì)自動(dòng)聯(lián)動(dòng)。 流控設(shè)置之所以有上表的規(guī)則要求,是需要保證雙絞線鏈路雙方的流控狀態(tài)匹配(雙方都“tx 使能rx使能”,雙方都“tx關(guān)閉rx關(guān)閉”和一方“tx關(guān)閉rx使能”另一方“tx使能rx關(guān)閉”)。如果出現(xiàn)雙絞線鏈路雙方流控失配,在鏈路擁塞時(shí)不但不能享受流控的優(yōu)點(diǎn),反而會(huì)引起鏈路中出現(xiàn)大量Pause流控幀使已經(jīng)擁塞的鏈路更加擁塞。

主從協(xié)商

在1000BASE-T模式中,鏈路的兩端執(zhí)行環(huán)路定時(shí)(loop timing)。鏈接的一端協(xié)商配置為主設(shè)備,另一個(gè)協(xié)商配置為從設(shè)備。主設(shè)備發(fā)送和接收時(shí)鐘鎖定在本地晶振輸入。從設(shè)備發(fā)送和接收時(shí)鐘被鎖定到傳入的接收數(shù)據(jù)流。環(huán)路定時(shí)(loop timing)通過確保發(fā)射機(jī)和接收機(jī)在鏈路的每一端都以相同的頻率工作。

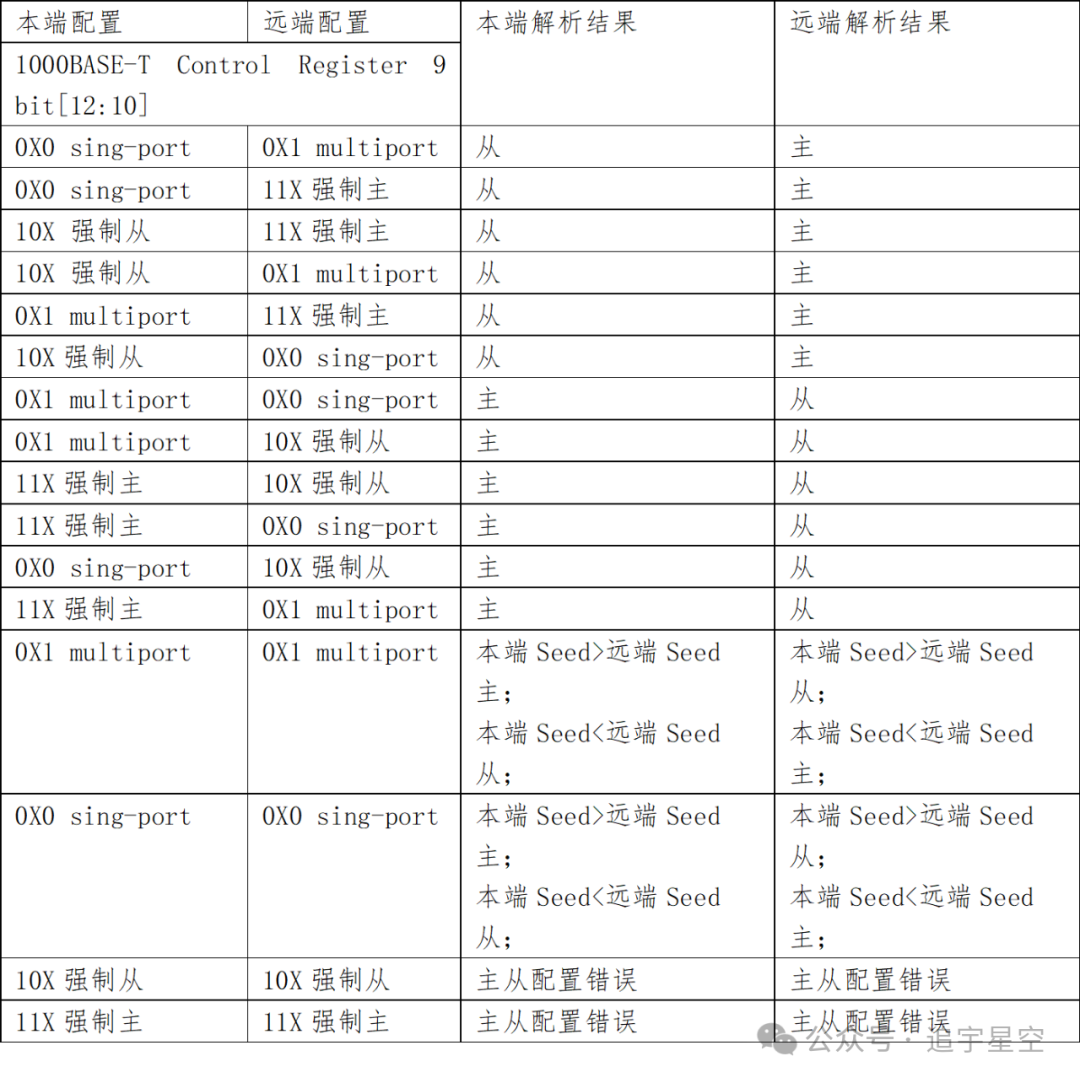

主從協(xié)商主要靠設(shè)置 “本地控制寄存器1000BASE-T ControlRegister Page 0, Register 9”的bit12:10實(shí)現(xiàn)的。具體規(guī)則如下表:

網(wǎng)絡(luò)管理員因避免出現(xiàn)上述表格的最后兩種情況,一旦出現(xiàn)此情況10M/100M/1000M自協(xié)商將永遠(yuǎn)無法完成,故此時(shí)本端和遠(yuǎn)端永遠(yuǎn)無法建立正確鏈接。 好的小伙伴們,這期10M/100M/1000M自協(xié)商就講完啦,下一課會(huì)開始“10M/100M/1000M/2.5G/5G/10G/25G/40G自協(xié)商”相關(guān)內(nèi)容。

審核編輯:劉清

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5288瀏覽量

169653 -

集線器

+關(guān)注

關(guān)注

0文章

376瀏覽量

39333 -

雙絞線

+關(guān)注

關(guān)注

2文章

225瀏覽量

23590 -

PHY

+關(guān)注

關(guān)注

2文章

296瀏覽量

51553 -

控制寄存器

+關(guān)注

關(guān)注

0文章

34瀏覽量

11461

原文標(biāo)題:以太網(wǎng)自協(xié)商機(jī)制--雙絞線自協(xié)商(四)

文章出處:【微信號(hào):FPGA開源工坊,微信公眾號(hào):FPGA開源工坊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

以太網(wǎng)自協(xié)商機(jī)制-雙絞線自協(xié)商案例設(shè)計(jì)(三)

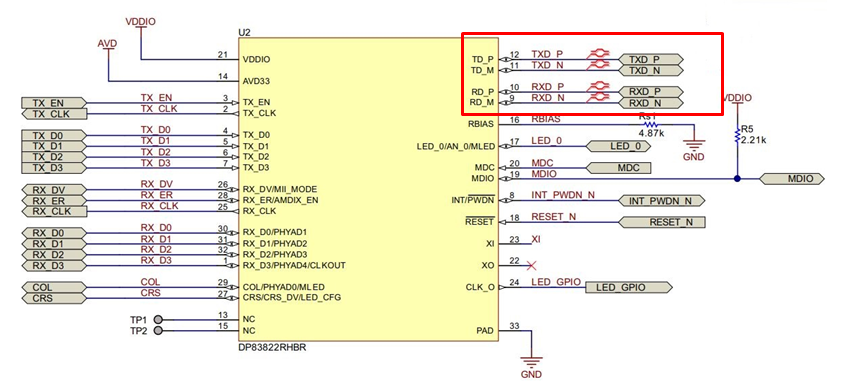

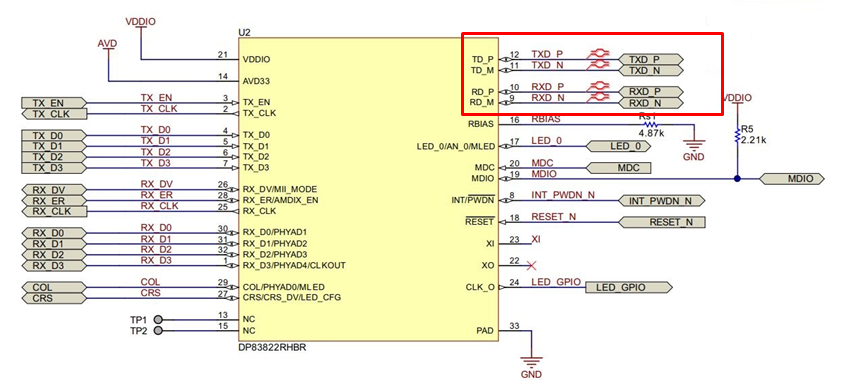

DP83822I工業(yè)以太網(wǎng)PHY自協(xié)商功能與其Strap電阻配置

為什么以太網(wǎng)+柔性板與電腦無法協(xié)商為100M?

基于DP83822I工業(yè)以太網(wǎng)PHY自協(xié)商功能與其Strap電阻配置

FPGA光纖以太網(wǎng)自協(xié)商的設(shè)計(jì)

基于語義網(wǎng)技術(shù)的SLA協(xié)商機(jī)制

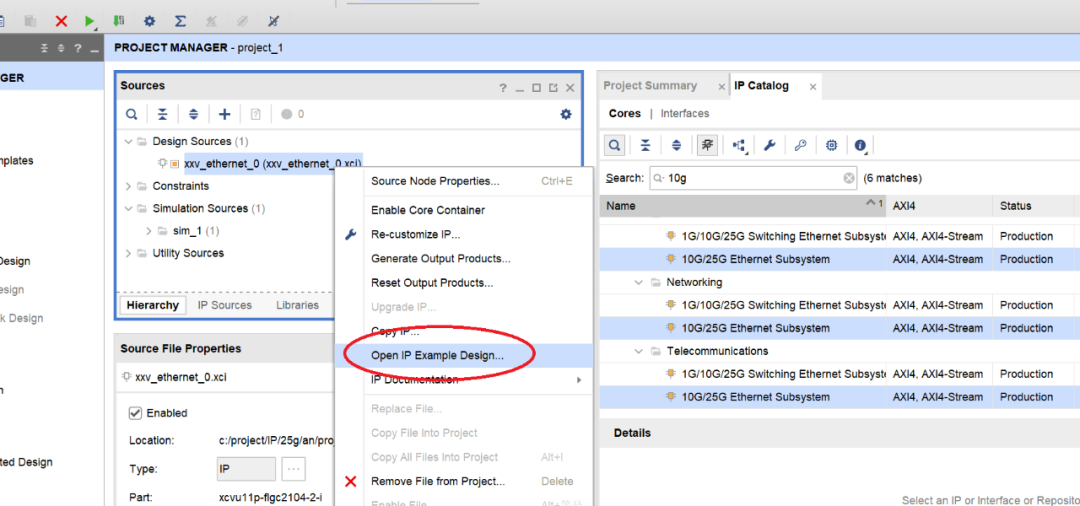

如何調(diào)試10G/25G以太網(wǎng)IP自協(xié)商/Link Training

10G/25G以太網(wǎng)IP自協(xié)商調(diào)試方案

以太網(wǎng)網(wǎng)口自協(xié)商功能現(xiàn)象

DP83822I工業(yè)以太網(wǎng)PHY自協(xié)商功能與其Strap電阻配置

DP83822I工業(yè)以太網(wǎng)PHY自協(xié)商功能與其Strap電阻配置

一文解析以太網(wǎng)自動(dòng)協(xié)商技術(shù)

基于IEEE Clause 28雙絞線的以太網(wǎng)自協(xié)商機(jī)制

基于IEEE Clause 28雙絞線的以太網(wǎng)自協(xié)商機(jī)制解析(一)

以太網(wǎng)自協(xié)商機(jī)制—雙絞線自協(xié)商案例(四)

以太網(wǎng)自協(xié)商機(jī)制—雙絞線自協(xié)商案例(四)

評(píng)論