1. 簡介

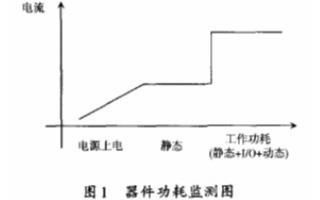

CMOS電路功耗主要由動態功耗和靜態功耗組成,動態功耗又分為開關功耗、短路功耗兩部分

2. 靜態功耗

靜態功耗也稱為待機功耗,包含有電路中晶體管的漏電流所導致的功耗

3. 動態功耗

3.1 開關功耗

動態功耗包括:開關功耗或稱為反轉功耗、短路功耗或者稱為內部功耗;

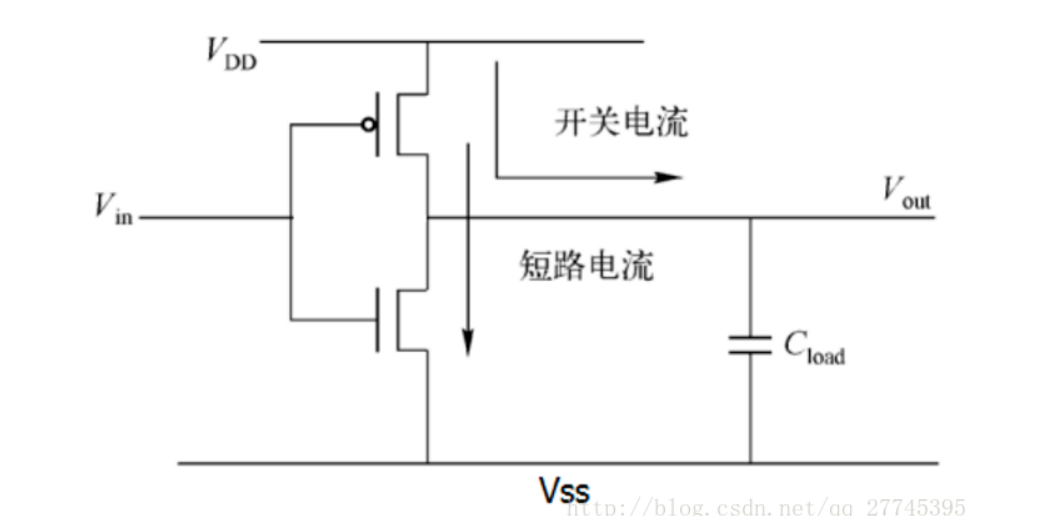

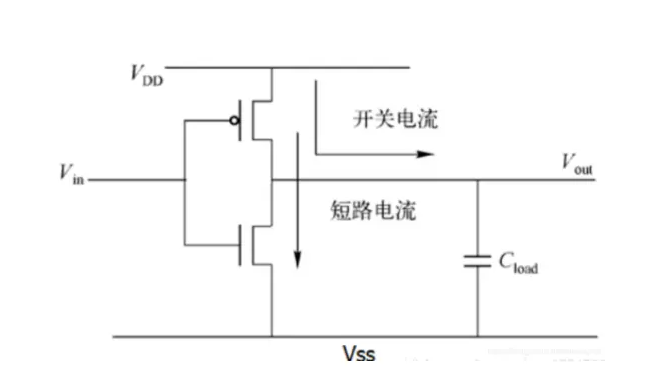

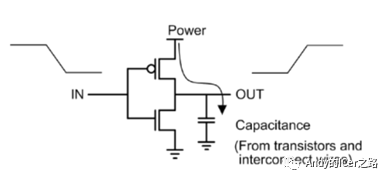

開關功耗:電路在開關過程中對輸出節點的負載電容充放電所消耗的功耗。比如對于下面的CMOS非門中:

當Vin=0時,PMOS管導通,NMOS管截止;VDD對負載電容Cl進行充電;

當Vin=1時,PMOS管截止,NMOS管導通;VDD對負載電容Cl進行放電;

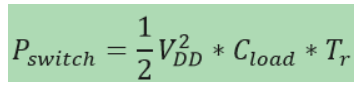

這樣開關的變化,電源的充放電,形成了開關功耗,開關功耗的計算公式如下, 并且通過這個式子我們可以只要有時鐘,或者信號跳變,就存在開關功耗,也就是動態功耗

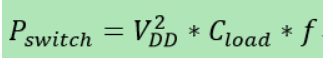

在上式中,VDD為供電電壓,Cload為后級電路等效的電容負載大小,Tr為輸入信號的翻轉率,也有另外一種寫法,f為時鐘頻率,一個周期信號翻轉兩次,所以這里沒有 1/2;

它與電路的工作頻率成正比,與負載電容成正比,與電壓的平方成正比。

3.2 短路功耗

由于輸入電壓波形并不是理想的階躍輸入信號,有一定的上升時間和下降時間,在輸入波形上升下降的過程中,在某個電壓輸入范圍內,NMOS和PMOS管都導通,這時就會出現電源到地的直流導通電流,這就是開關過程中的短路功耗。

短路功耗產生的條件一樣是需要信號產生跳變。

3. 靜態功耗

在CMOS電路中,靜態功耗主要是漏電流引起的功耗

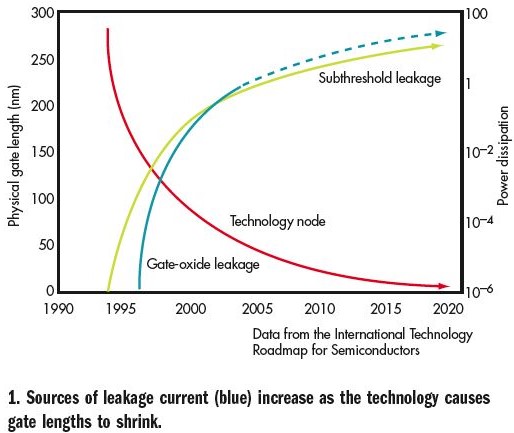

對于常規cmos電路,在穩態時不存在直流導通電流,理想情況下靜態功耗為0,但是由于泄露電流的存在,使得cmos電路的靜態功耗并不為0。一般情況下,漏電流主要是指柵極泄漏電流和亞閾值電流, CMOS泄露電流主要包括:

PN結反向電流I1(PN-junction Reverse Current)

源極和漏極之間的亞閾值漏電流I2(Sub-threshold Current)

柵極漏電流,包括柵極和漏極之間的感應漏電流I3(Gate Induced Drain Leakage)

柵極和襯底之間的隧道漏電流I4(Gate Tunneling)

柵極泄漏功耗:在柵極上加信號后(即柵壓),從柵到襯底之間存在電容,因此在柵襯之間就會存在有電流,由此就會存在功耗。

亞閾值電流:使柵極電壓低于導通閾值,仍會產生從FET漏極到源極的泄漏電流。此電流稱為亞閾值泄漏電流。要降低亞閾值電流,可以使用高閾值的器件,還可以通過襯底偏置進行增加閾值電壓,這些屬于低功耗設計。

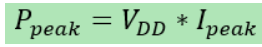

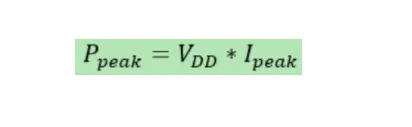

靜態功耗的計算公式如下,Ipeak為泄漏電流:

4. 低功耗設計

4.1 RTL級

1.并行結構:并行結構一定程度可以減低某一區域的頻率,從而可能降低功耗。

2.流水結構:“路徑長度縮短為原始路徑長度的1 /M。這樣,一個時鐘周期內充/放電電容變為C/M。如果在加入流水線之后,時鐘速度不變,則在一個周期內,只需要對C/M進行充/放電,而不是原來對C進行充/放電。因此,在相同的速度要求下,可以采用較低的電源電壓來驅動系統。”

3.優化編碼:通過數據編碼來降低開關活動,例如用格雷碼取代二進制。

4.操作數隔離:“操作數隔離的原理就是:如果在某一段時間內,數據通路的輸出是無用的,則將它的輸入置成個固定值,這樣,數據通路部分沒有翻轉,功耗就會降低。”

4.2 門級電路

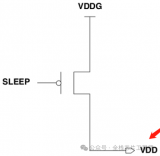

1.門控時鐘技術:芯片工作時,很大一部分功耗是由于時鐘網絡的翻轉消耗的,控技術基本原理就是通過關閉芯片上暫時用不到的功能和它的時鐘,從而實現節省電流消耗的目的,門控時鐘對翻轉功耗和內部功耗的抑制作用最強,是低功耗設計中的一種最有效的方法。

2.多電壓供電

3.多閾值電壓

根據多閾值電壓單元的特點,為了滿足時序的要求,關鍵路徑中使用低閾值電壓的單元(low Vt cells),以減少單元門的延遲,改善路徑的時序。而為了減少靜態功耗,在非關鍵路徑中使用高閾值電壓的單元(high Vt cells),以降低靜態功耗。因此,使用多閾值電壓的工藝庫,我們可以設計出低靜態功耗和高性能的設計。

4.動態電壓調節

5.動態頻率調節

審核編輯:劉清

-

NMOS

+關注

關注

3文章

291瀏覽量

34298 -

靜態功耗

+關注

關注

0文章

17瀏覽量

8927 -

CMOS電路

+關注

關注

0文章

49瀏覽量

11499 -

VDD

+關注

關注

1文章

311瀏覽量

33122 -

電容充放電

+關注

關注

0文章

94瀏覽量

5829

原文標題:靜態功耗和動態功耗

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

靜態和動態功耗的定義

cmos動態功耗公式,cmos動態功耗和哪些電路參數有關

淺析CMOS電路的靜態功耗和動態功耗

淺析CMOS電路的靜態功耗和動態功耗

評論