2024年國際集成電路展覽會暨研討會(IIC)在上海圓滿落幕,本屆展會和研討會吸引了眾多國內外Fabless、EDA/IP廠商參加。英諾達憑借在EDA領域的突出創新成果,榮獲由AspenCore頒發的“2024中國IC設計成就獎之年度創新EDA公司”獎項。

英諾達副總經理熊文受邀出席本屆IC領袖峰會,并發表了題為《靜態驗證EDA工具助力大規模芯片設計的創新突破》的主題演講,分享了英諾達在靜態驗證領域的最新技術成果,深入探討了靜態驗證技術如何助力大規模芯片設計實現“設計左移”。

“設計左移”避免Debug成本指數級增長

過去幾十年,SoC芯片的設計規模越來越龐大,為了實現更多的功能,芯片的復雜性也急劇增加。通常,一片SoC可能包含數十億個邏輯門以及數百萬個連接、若干個IP和存儲器,以及多個電源域和時鐘域。這給驗證工作帶來了不小的挑戰,這些復雜連接的正確性對于SoC芯片的功能至關重要,若出現問題,會導致SoC芯片功能異常,甚至無法工作。

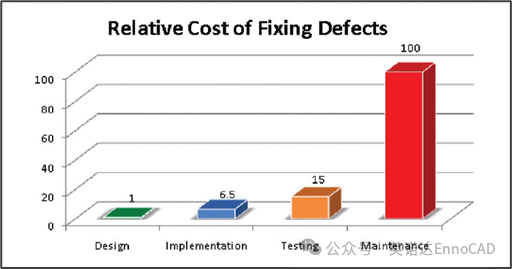

英諾達的副總經理熊文在演講中指出,像SoC這種大規模芯片在Sign-off階段發現、修復bug的成本很高,會需要多輪debug和驗證的迭代,甚至影響到產品上市的時間。IBM統計在實現階段修復一個漏洞或錯誤的成本是設計階段的6.5倍,而到了測試階段,這一成本更是激增至15倍。

不同設計階段修復缺陷的成本呈指數級增長(Source: IBM)

所以“設計左移”就是指將設計流程后期執行的任務提前到更早的階段進行,從而可以在早期發現并糾正關鍵bug,加快產品迭代的速度,這種策略不僅可以節省時間和資源,還可以提高產品質量和芯片的良率。而隨著軟件的重要性越來越高,另外一種形式的“設計左移”就是盡早讓軟件在硬件上運行進行調試。

為了應對“設計左移”的需求和趨勢,設計廠商聯同EDA廠商一起,不斷在設計流程和方法學上進行創新和優化。靜態驗證是目前業界普遍使用的方法,在設計中通過配合動態仿真驗證和形式化驗證,可以提高驗證的覆蓋率,幫助設計師在設計開發的早期更快地發現和診斷設計缺陷,從而縮短設計驗證所需的時間,簡化SoC設計的整體開發周期,降低芯片開發的成本。

靜態驗證在低功耗設計中的應用

英諾達深耕數字中端EDA工具領域,以低功耗系列工具為突破口,縱深布局靜態驗證技術,橫向拓展相關產品線,致力于為芯片設計提供全面的靜態驗證解決方案,目前已經發布了EnFortius凝鋒低功耗系列和EnAltius昂屹靜態檢查系列EDA工具。

以低功耗設計為例,靜態驗證是如何在該領域中應用的呢?功耗一直以來是芯片設計的重要考量因素,也是導致流片失敗的主要原因之一。面對日益嚴峻的功耗挑戰,設計團隊需要先進方法學和工具的支持,在設計全流程中進行低功耗設計。

低功耗設計面臨著多重挑戰:

電路復雜度提高:為了降低功耗,芯片設計往往使用多電壓域,這使得電源管理和設計更加復雜。

UPF標準版本太多:電源管理需要使用UPF標準進行描述,但大多主流工具難以支持該標準的所有版本。

早期電源分析困難:在沒有物理器件的情況下,設計早期難以進行準確的電源估算和分析。

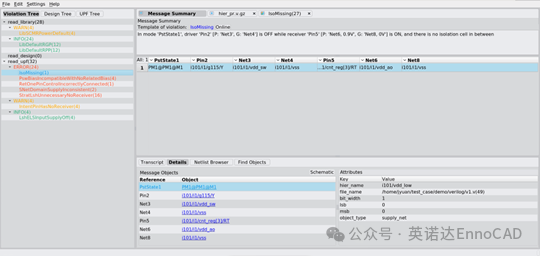

英諾達EnFortius低功耗設計靜態驗證工具(LPC)基于先進的功耗設計方法學,幫助IC設計師從RTL到GDS全流程進行低功耗設計管理,確保UPF和功耗設計意圖的正確性和一致性。這款工具不僅可以快速準確地查錯,還可以幫助用戶快速定位問題根源。

GUI界面簡化了查錯過程

在功耗分析方面,為了幫助設計團隊更早掌握功耗水平,及早對功耗進行優化,英諾達EnFortiusRTL級功耗分析工具(RPA)采用自主研發的綜合引擎和物理線網模型,大幅提高功耗估算的準確性,幫助設計團隊從RTL階段開始捕捉功耗趨勢,甄別功耗熱點。

熊文在演講中表示:“靜態驗證作為一種有效的低功耗設計方法,可以從系統設計、RTL設計到物理實現的全階段進行功耗分析和優化。通過靜態驗證方法,設計團隊能夠盡早發現和修復功耗相關問題,避免流片后功耗超標的風險。實踐證明,越早進行功耗分析和優化,效果越好。因此,設計團隊應積極采用靜態驗證等先進方法,在設計早期就開始進行功耗管理,以確保芯片設計成功。”

? ?

? ?

審核編輯:劉清

-

集成電路

+關注

關注

5382文章

11396瀏覽量

360945 -

EDA工具

+關注

關注

4文章

265瀏覽量

31717 -

芯片設計

+關注

關注

15文章

1005瀏覽量

54819 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34875 -

靜態驗證

+關注

關注

0文章

6瀏覽量

5982

原文標題:靜態驗證EDA工具助力大規模芯片設計的創新突破

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

泰克科技榮獲2024全球電子成就獎之年度創新產品獎

Cadence榮獲2024全球電子成就獎之年度EDA/IP/軟件產品獎

引領RISC-V核心技術,賽昉科技榮膺AspenCore“年度技術突破IP公司”獎項

燦瑞科技榮獲2024年度中國IC設計成就獎之“年度創新IC設計公司”

川土微榮獲“2024中國IC設計成就獎之年度杰出市場表現獎-汽車電子”

Imagination榮獲2024中國IC設計成就獎“年度產業杰出貢獻IP公司”

英諾達榮獲“2024中國IC設計成就獎之年度創新EDA公司”獎項

英諾達榮獲“2024中國IC設計成就獎之年度創新EDA公司”獎項

評論