這是一種驅使人們自愿構建自己的CPU的癢。我們開始思考我們理解中的空白,這個空白潛伏在邏輯門和觸發器如何單獨工作以及機器代碼如何控制完全組裝的處理器之間。在硬連線電路開始隨著軟件不斷變化的曲調跳舞的神奇區域中究竟發生了什么?

事實證明,這種癢折磨著足夠多的人,以至于有商業套件供想要將 CPU 組裝在一起以看到(或聽到)它的制造商使用,并且網絡上充斥著自制的 4 位和 8 位 CPU,其架構是 1970 年代工程師所熟悉的。我應該知道——我自己做了一個。但后來我開始懷疑:我能不能用一些最新技術來構建自己的CPU?我可以設計自己的完全兼容的 32 位 RISC-V 中央處理器嗎?

RISC-V 是一個開源架構,大約有 11 年的歷史,現在開始在由 x86 和 ARM CPU 架構主導的世界中取得進展。羅伯特·巴魯克(Robert Baruch)的工作提醒了我RISC-V的可能性,他大約兩年前開始了一個類似的項目,但尚未完成他的處理器,部分原因是他必須不斷重新設計他早期構建的組件,以滿足不斷發展的設計需求。

RISC-V 設計的模塊化特性使我能夠將 Pineapple One 構建為一堆可單獨測試的 10 x 10 厘米 PCB,這些 PCB 具有不同的功能(順時針方向,從左上角開始):VGA 驅動器;公羊;傳輸層;移;阿魯;寄存器文件;控制單元;程序計數器;只讀存儲器。詹姆斯·普羅沃斯特

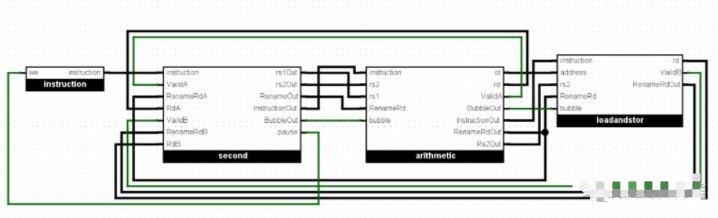

取而代之的是,我首先在邏輯電路仿真器Logisim Evolution中構建了我的完整設計,我將其命名為Pineapple One。在查閱了官方 RISC-V 手冊以及 David Patterson 和 John Hennessy 的著作《計算機組織與設計,RISC-V 版》(Elsevier,2017 年)的第一版,并將 Logisim 推向了極限,我在六個月內對 Pineapple One 進行了工作模擬,滿足了基本 RISC-V CPU 的要求。

在實現 RISC-V 架構時,我驚訝地發現,與我早期自制 CPU 中使用的傳統復雜指令集相比,該架構的意義要大得多。冗余被消除,處理器的寄存器(存儲 CPU 工作內存的暫存器)更加靈活。另一大優勢是RISC-V是一個有據可查的模塊化設計,所以我知道每個模塊必須做什么。我的目標是以我自己的方式設計每個模塊,但要確保它的性能符合 RISC-V 標準。(這決定了我的 CPU 是 32 位的,因為根據定義,RISC-V 指令至少那么長。

從物理上講,菠蘿一號分布在垂直堆疊的八個方形印刷電路板上,這些電路板的邊長約為10厘米,外加一個處理VGA顯示接口的卡。它使用了 230 多個集成電路,主要來自 74HCT 系列邏輯芯片。我最大的挑戰是實現桶形移位器,這種電路可以圍繞寄存器中的位以可控的量進行移位。我首先嘗試了一種需要 80 多個組件的快速實現,但盡我所能,我無法讓它適合我的 PCB。因此,我采用了一種低組件方法,基本上暫停了 CPU 其余部分的運行,直到我的變速桿完成啟動。由于菠蘿一號的走線很長,與單芯片CPU相比,我還很難管理寄生電容和阻抗,這意味著要調試一些非常奇怪的行為。

忠誠shopping_cart刪除

詹姆斯·普羅沃斯特(James Provost):雖然有規定指令的長度范圍在16位和理論上無限的數量之間,但這里是RISC-V指令的四種核心類型的固定32位格式。一些指令將操作碼與其他功能字段相結合來定義行為,而另一些指令則允許將多個源寄存器與所謂的即時數據相結合,并將結果放置在目標寄存器中。

我使用Arduino微控制器測試了每塊板,以模擬計算機其余部分的輸入,并監控輸出的正確性。我用3D打印了一個漂亮的外殼來容納整堆PCB和輸入/輸出連接器,這樣就可以將鍵盤和VGA顯示器直接連接到Pineapple One上。有 4 個通用 I/O 端口 — 2 個 8 位輸入和 2 個輸出。

我的朋友 Jan Vykydal 幫助我設置了一個符合 RISC-V 的編譯器才能正常工作,所以我用 C 語言編寫了一些系統軟件和演示程序。編譯器生成機器代碼,我使用一個 Python 腳本來獲取代碼并將其閃存到 CPU 的內存中。盡管 Pineapple One 的運行頻率僅為 500 千赫茲,但這仍然足夠快,可以實時玩像 Snake 這樣的簡單電腦游戲,而且 512 KB 的程序內存和 512 kB 的 RAM 已經足夠了。

最終,我想稍微升級一下處理器,以便它可以運行更復雜的程序。我還想添加更多擴展板,例如聲卡。您可以在 Hackaday 上找到原理圖和物料清單,但最終將其作為套件提供給其他有興趣了解當代 CPU 設計的人會很棒。

審核編輯 黃宇

-

芯片

+關注

關注

454文章

50460瀏覽量

421968 -

cpu

+關注

關注

68文章

10829瀏覽量

211183 -

RISC-V

+關注

關注

44文章

2233瀏覽量

46045

發布評論請先 登錄

相關推薦

64位RISC-V CPU發展現狀和未來前景

RISC-V 生態架構淺析

科普RISC-V生態架構(認識RISC-V)

瑞薩基于RISC-V核心架構的預編程ASSP器件

ARM與RISC-V架構的區別是什么?

RISC-V,正在擺脫低端

兩大架構RISC-V 和 ARM 的各種關系

聚焦RISC-V架構,避免主流CPU架構制約

為什么我們提升了RISC-V的會員等級

芯來科技CEO彭劍英:RISC-V構建自主可控CPU繁榮生態

TenstorrentInc首席CPU構架師 練維漢:助力數字化升級的RISC-V AI 高性能CPU

從頭開始構建 RISC-V CPU使用分立邏輯芯片,通過最熱門的新架構構建功能驚人的 CPU

從頭開始構建 RISC-V CPU使用分立邏輯芯片,通過最熱門的新架構構建功能驚人的 CPU

評論