近年來,芯片的發展進程始終嚴格遵守著“摩爾定律”,并有條不紊地進行著,直到14nm制造工藝的芯片在英特爾的實驗室中被研制成功,業界開始有了擔憂。

據摩爾定律所說,集成在同一芯片上的晶體管數量大約每兩年增加一倍,同時相同大小的芯片將具有雙倍的性能。一旦達到14nm的制程,將極其接近硅晶體的理論極限數字(大約為9nm到11nm)。

盡管英特爾依然樂觀地預測將于2015年之前推出8nm制程工藝的芯片,但人們還是懷疑14nm可能將成為硅芯片尺寸的最終盡頭。

納米級芯片速度放緩

我們相信,尋找這一答案恐怕還要從芯片的發展歷史說起,早在上世紀八九十年代,無論是英特爾、IBM 還是TMSC(臺積電)宣布他們的晶體管產品跨越至下一個納米級,或者其芯片的晶圓工廠進入到微米級梯隊,都足以稱為是令業界震驚的大事件。比如1985年,英特爾的80386處理器采用了1微米制造工藝;2004年底,微米尺寸被徹底拋棄,采用90nm的Winchester AMD 64和Prescott Pentium 4成為了當時業界的新標。

不過在最近,硅芯片的工藝制程速度被不斷放緩。現階段的數碼設備所使用的處理器、傳感器以及內存芯片基本都是基于45nm或60nm,因為除了英特爾以外,幾乎沒有哪家的硅芯片產品或技術能夠達到32nm,更別提22nm了。

傳統制造工藝遭遇瓶頸

原因在于,芯片在制造過程中通常會采用的自上而下、逐層制造的方法已經出現了技術瓶頸,即使在通過最新的原子層沉積技術,將芯片工藝進一步帶入22nm、16甚至14nm,以及硅晶體管的“三維”結構后,恐怕就再也沒路可走了。

我們知道,原子的體積非常小,例如,一個氫原子大約只是0.1nm,銫原子的體積在0.3nm左右,而硅芯片上的原子大概在0.2nm左右。如此,可以正確理解為,22或16nm的硅芯片上可以聚集幾百個原子,但這并不是某一個晶體管的大小,它實際上是一種離散芯片元件距離的有效措施而已。在22nm芯片中,這種制造工藝目前只被英特爾一家所掌握,并且其相關的芯片產品Ivy Bridge也即將面向市場其中的高-K介電層只有0.5nm厚,相當于2到3個原子的厚度。

然而問題在于,世界上沒有一種制造技術是完美的。當我們因為某個不適合的原子而影響了整個芯片時,它將不再可能創造出性能可靠且具備成本效益的優質電路。

突破口可能是“補充技術”

那么,究竟應該如何突破14nm的技術瓶頸,也許惟一的選擇應該是改變現有芯片的制造方式,現在研究人員每年都花費大量的時間和金錢在已有的逐層蝕刻技術領域,但這并不是解決問題的方向。

未來幾年的應對措施應該聚焦在那些臨時補充技術上,例如IBM的“silicon glue”以及Invensas的chip-stacking技術等,這些技術既可以降低能耗,提高單芯片性能,又可以將更多晶體管匯聚到同一晶圓片上其技術關鍵在于,減少柵極漏電來控制功耗,以及在單晶片上構建更多數量的元件。

好在英特爾最近公布的14nm路線圖已經回應了我們對于突破14nm技術瓶頸的種種揣測,也是英特爾的答案是石墨芯片、光子或量子計算機,或是轉向了移動計算。不過,無論采用哪種技術,都不用太過擔心如果說永無止境的硅芯片制造工藝教會了人們什么,那就是未來的電腦一定會變得更快、更便宜和更有效。

-

制造工藝

+關注

關注

2文章

175瀏覽量

19730 -

硅芯片

+關注

關注

0文章

90瀏覽量

16948 -

硅芯片尺寸

+關注

關注

0文章

1瀏覽量

6452 -

硅工藝

+關注

關注

0文章

3瀏覽量

7071

發布評論請先 登錄

相關推薦

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰

臺積電產能爆棚:3nm與5nm工藝供不應求

銳成芯微推出基于8nm工藝的PVT Sensor IP

所謂的7nm芯片上沒有一個圖形是7nm的

4nm!小米 SoC芯片曝光!

光模塊850nm和1310nm能共用嗎

2024年全球與中國7nm智能座艙芯片行業總體規模、主要企業國內外市場占有率及排名

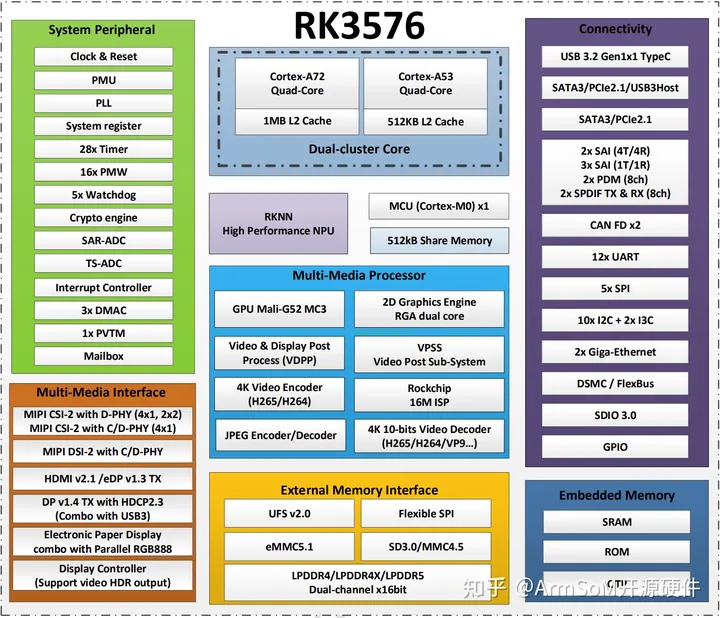

瑞芯微第二代8nm高性能AIOT平臺 RK3576 詳細介紹

超詳細!瑞芯微第二代8nm高性能AIOT平臺 RK3576 參數介紹

硅芯片尺寸的盡頭之爭:14nm or 8nm?

硅芯片尺寸的盡頭之爭:14nm or 8nm?

評論