電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))對(duì)于任何一個(gè)芯片大廠而言,在ISA的選擇上都是相當(dāng)謹(jǐn)慎的。ISA不僅決定了芯片開發(fā)的難易程度,也決定了與之綁定的軟件和開發(fā)生態(tài),甚至可能會(huì)影響到市場(chǎng)面臨的競爭。然而在這個(gè)重要的選擇上,我們卻發(fā)現(xiàn)不少大廠開始發(fā)力RISC-V。

瑞薩:授權(quán)到自研

瑞薩作為MCU大廠之一,尤其是在汽車領(lǐng)域,經(jīng)過多年的積累與開發(fā),旗下已經(jīng)有了多條MCU產(chǎn)品線。在32位MCU上,有基于自研CISC內(nèi)核的RX系列,也有基于Arm Cortex-M架構(gòu)的RA系列。即便如此,瑞薩還是決心開拓第三條產(chǎn)品線,而且是基于RISC-V架構(gòu)。

其實(shí)瑞薩很早就開始RISC-V相關(guān)的布局了,比如2021年推出的汽車控制域管理MCU RH850/U2B,就集成了來自NSI-TEXE開發(fā)的MIMD加速器核心,基于RISCV架構(gòu)的DR1000C。

DR1000C不僅取得了ISO 26262 ASIL D級(jí)別的認(rèn)證,憑借其并行處理器的特性,可以幫助MCU卸載一些繁重的計(jì)算工作,比如模型預(yù)測(cè)控制、AI推理以及傳感器數(shù)據(jù)處理等等,不僅適合工業(yè)自動(dòng)化設(shè)備,也很適合用于汽車MCU中輔助雷達(dá)或其他傳感器的融合計(jì)算。

除此之外,瑞薩也與晶心科技達(dá)成合作,繼續(xù)推出了用于特定市場(chǎng)的RISC-V產(chǎn)品,比如集成了RISC-V核心的ASSP和MPU產(chǎn)品,包括基于RISC-V的電機(jī)控制ASSP MCU,以及64位的RZ/Five,前者主要用于工業(yè)控制、人機(jī)交互等場(chǎng)景,而后者則主要用于網(wǎng)關(guān)控制。

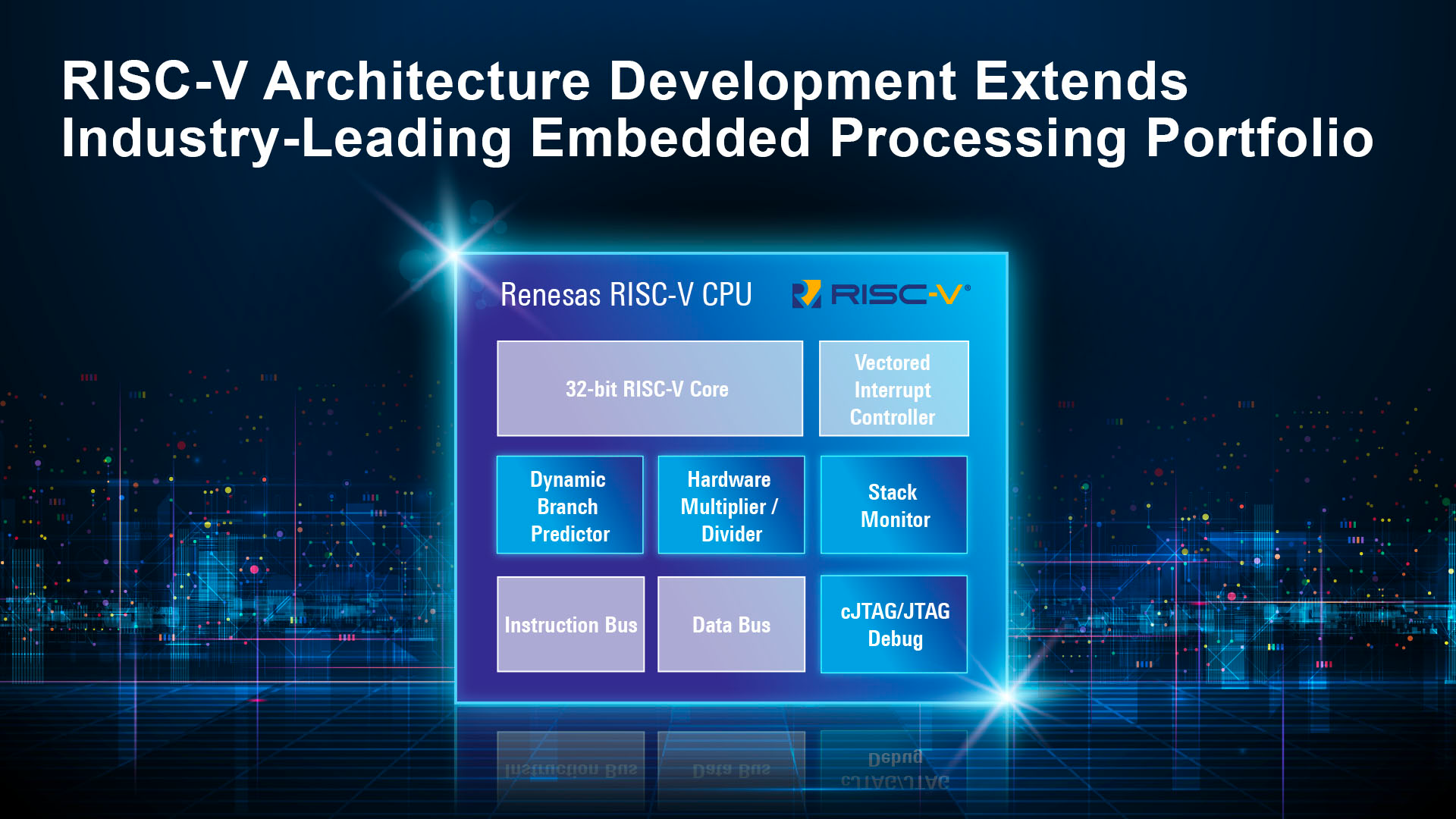

在RISC-V上,瑞薩不僅選擇了授權(quán)第三方內(nèi)核,也有了自研內(nèi)核的野心,為其通用MCU再度開辟一條可選產(chǎn)品線。2023年11月30日,瑞薩宣布推出第一代32位RISC-V CPU內(nèi)核,計(jì)劃面向物聯(lián)網(wǎng)、消費(fèi)電子、醫(yī)療保健和工業(yè)系統(tǒng)打造一個(gè)全新的開放靈活平臺(tái),也作為其已有RX系列和RA系列的補(bǔ)充。

瑞薩自研RISC-V內(nèi)核 / 瑞薩

作為其首個(gè)自研RISC-V內(nèi)核,其CoreMark/MHz達(dá)到了3.27,要低于此前用到的晶心科技N22核心,也低于其自研的RXv1核心。由此看來其首個(gè)自研RISC-V核心的規(guī)模并不高,主要用于超低功耗的MCU設(shè)計(jì)。

近日,瑞薩也發(fā)布了基于該自研內(nèi)核打造的首個(gè)通用32位RISC-V MCU,R9A02G021,正是一款超低功耗的48MHz MCU產(chǎn)品。R9A02G021集成了128KB代碼閃存,4KB數(shù)據(jù)閃存,以及16KB的SRAM和豐富的IO。在開發(fā)工具上,瑞薩的e2 studio依然為R9A02G021提供了IDE支持,除此之外,IAR和SEGGER也迅速跟進(jìn)了對(duì)這一MCU的開發(fā)支持。

即便有了新的RISC-V內(nèi)核,并不代表瑞薩會(huì)放棄其他產(chǎn)品線的后續(xù)開發(fā),從其路線圖規(guī)劃上可以看出,無論是RL78、RX、RA系列,瑞薩都有產(chǎn)品擴(kuò)充和增強(qiáng)的計(jì)劃,以實(shí)現(xiàn)更高的性能和集成度,并加入一定的AI/ML功能。與此同時(shí),瑞薩或許也會(huì)在未來開發(fā)更高規(guī)格的RISC-V內(nèi)核,用在更高性能的RISC-V MCU設(shè)計(jì)上。

高通:率先發(fā)力可穿戴和汽車

高通作為Arm陣營的堅(jiān)定擁護(hù)者,這些年也在慢慢向RISC-V傾斜一部分開發(fā)資源。在2022的RISC-V全球峰會(huì)上,高通高管宣布,早在2019發(fā)布的驍龍865 SoC中,高通就已經(jīng)將RISC-V用到了微控制器的設(shè)計(jì)中,并已經(jīng)出貨了上億個(gè)RISC-V核心,盡管高通并未透露后續(xù)的驍龍手機(jī)SoC是否繼續(xù)沿用這一設(shè)計(jì),但已經(jīng)足以說明這家手機(jī)芯片大廠對(duì)于RISC-V的重視了。

去年一則與RISC-V相關(guān)的新聞相信不少人都已經(jīng)看過了,那就是高通聯(lián)合博世、英飛凌、恩智浦、Nordic幾家大廠,共同成立了一家名為Quintauris的RISC-V初創(chuàng)企業(yè)。該公司的目標(biāo)是通過支持下一代硬件開發(fā)來推動(dòng)RISC-V在全球的普及,也就是加速RISC-V架構(gòu)產(chǎn)品的商業(yè)化,提供參考架構(gòu)。據(jù)其官網(wǎng)描述,這家公司的初期重點(diǎn)放在了汽車應(yīng)用上,也就是說未來高通很可能會(huì)根據(jù)這一參考架構(gòu),推出對(duì)應(yīng)的RISC-V汽車芯片產(chǎn)品。

在聯(lián)合成立RISC-V公司的消息發(fā)布后不久,高通又聯(lián)合谷歌共同宣布,雙方將加強(qiáng)合作,基于RISC-V架構(gòu)開發(fā)下一代Snapdragon Wear平臺(tái),從而為谷歌的下一代Wear OS解決方案提供支持,而且高通明確表示,他們將在全球范圍內(nèi)推行RISC-V的可穿戴解決方案。不過,RISC-V在這一新的Snapdragon Wear可穿戴硬件平臺(tái)以什么定位出現(xiàn),我們尚不清楚。

從過去的可穿戴芯片來看,高通主要采用性能中等的Arm內(nèi)核來打造相關(guān)的SoC。比如從Wear1100到Wear 3100,其都是基于Arm Cortex-A7來設(shè)計(jì)CPU部分的。直到2020年推出的Wear4100+,才開始使用4核A53 CPU加協(xié)處理器的設(shè)計(jì)。

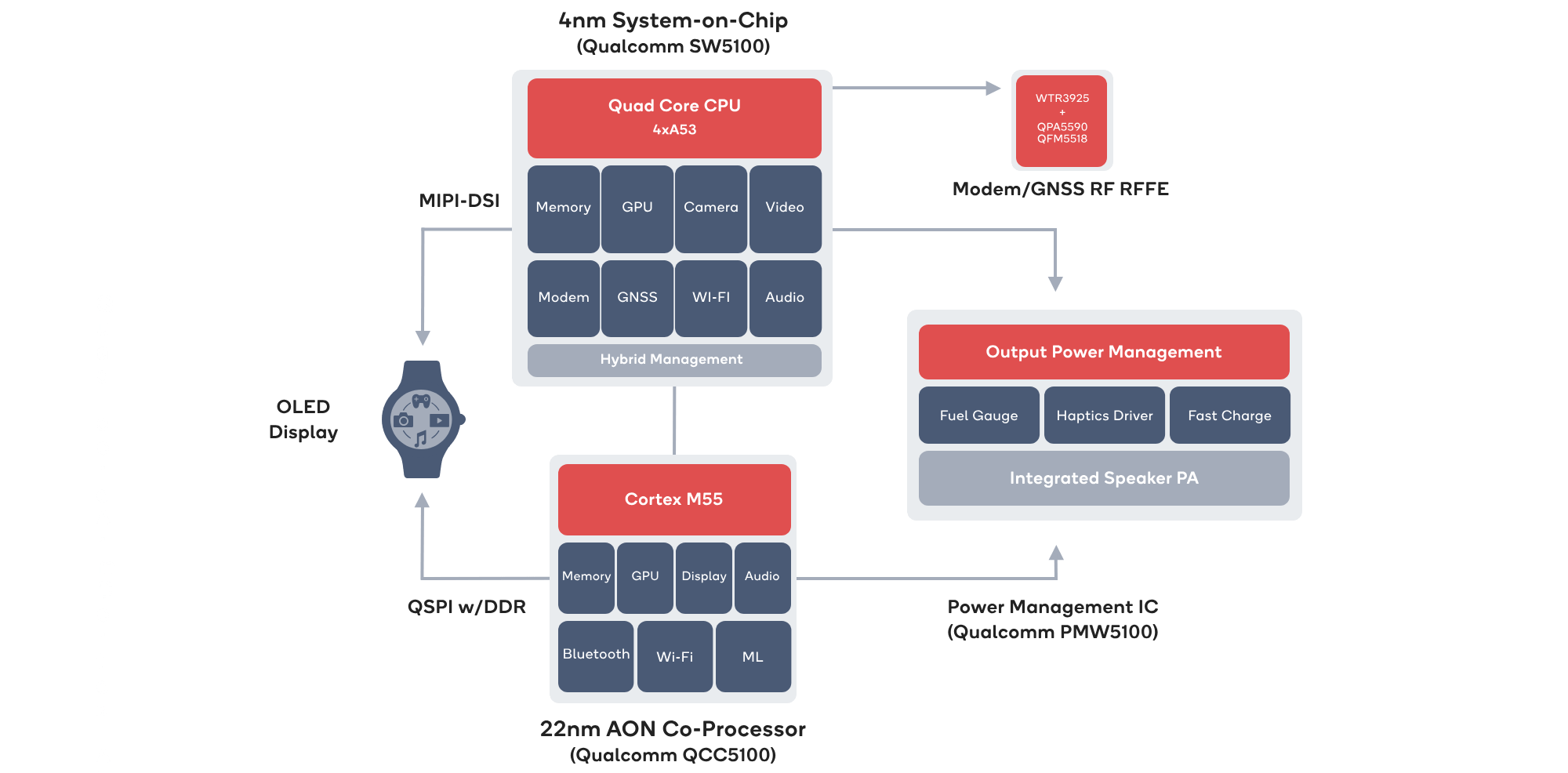

Snapdragon W5+ Gen1可穿戴硬件平臺(tái) / 高通

在最新的W5+ Gen1平臺(tái)中,高通依然沿用了4核A53加協(xié)處理器的設(shè)計(jì),只不過主CPU工藝從12nm換成了4nm,而協(xié)處理器也從QCC1110(Cortex-M0)換成了QCC5100(Cortex-M55)。依照高通的說法,其協(xié)處理器主要是用來支持谷歌Wear OS、ASOP和RTOS,而且其只需要用到22nm的成熟工藝。

在高通與谷歌的聯(lián)合公告中,也明確表示新平臺(tái)主要用于支持Wear OS,這樣看來高通新的RISC-V硬件既有可能作為主CPU,也有可能作為協(xié)處理器。無論如何,兩家公司都已經(jīng)加入了RISC-V的軟件生態(tài)系統(tǒng)(RISE)中,無論是哪種設(shè)計(jì)方案,都會(huì)給RISC-V在可穿戴領(lǐng)域的軟件開發(fā)帶來新的突破。

MIPS:主打高性能處理器

曾幾何時(shí),MIPS也是市場(chǎng)主流的RISC處理器架構(gòu),甚至有望比肩Arm、x86,就連國內(nèi)的龍芯在發(fā)展LoongArch架構(gòu)之前,用的也是MIPS架構(gòu)。MIPS以設(shè)計(jì)具有多流水線、多流水線和支持虛擬化的處理器聞名,甚至目前不少ADAS系統(tǒng)都還運(yùn)行在MIPS處理器上。

然而在成功推出了幾代32位和64位RISC處理器之后,MIPS并沒有超越x86,反而被崛起的Arm掩蓋了光芒。MIPS在這期間甚至嘗試過開源方案,但依舊陷入了無人問津的境地。因此2021年3月,MIPS宣布終止了MIPS架構(gòu)的開發(fā),同時(shí)公司整個(gè)轉(zhuǎn)向RISC-V架構(gòu)。

盡管在收購和轉(zhuǎn)型中,MIPS經(jīng)歷了各種波折,但手上還是留有一些微架構(gòu)專利,也有豐富的處理器設(shè)計(jì)與開發(fā)經(jīng)驗(yàn),對(duì)于同為RISC的RISC-V來說,MIPS本身還是存在不小的優(yōu)勢(shì)。

2022年,MIPS推出了其全新開發(fā)的RISC-V處理器系列,eVocore,目前只有P8700和I8500兩大多處理器IP核。其中P8700針對(duì)數(shù)據(jù)中心的高性能計(jì)算場(chǎng)景設(shè)計(jì),P8700采用了少見16級(jí)流水線設(shè)計(jì),加上多發(fā)射亂序執(zhí)行和多線程,而且可拓展性可以使其支持到512個(gè)內(nèi)核。MIPS表示其單線程性能遠(yuǎn)超市面上現(xiàn)有的其他RISC-V CPU IP,但并沒有提供具體的跑分參數(shù)。

除了P8700這類高性能通用CPU核心外,MIPS近期的動(dòng)向表明其也在發(fā)力AI計(jì)算。比如MIPS在今年迎來了新的首席架構(gòu)師Brad Burgess,此前他在SiFive參與了P870處理器的亂序矢量單元設(shè)計(jì)。此外,他們也在美國開設(shè)了新的研發(fā)中心,計(jì)劃與當(dāng)?shù)卮髮W(xué)合作,開發(fā)汽車、數(shù)據(jù)中心和嵌入式市場(chǎng)的AI計(jì)算創(chuàng)新方案。

寫在最后

可以看到,對(duì)于絕大多數(shù)大廠而言,RISC-V都是一個(gè)愈發(fā)可行的產(chǎn)品設(shè)計(jì)方向。這也充分說明了RISC-V的開放性,以及更加成熟的軟硬件開發(fā)環(huán)境,和更低的設(shè)計(jì)風(fēng)險(xiǎn)。盡管多數(shù)廠商目前依然抱著嘗試的心態(tài),但隨著RISC-V生態(tài)的持續(xù)壯大,相信會(huì)有更多的大廠投入RISC-V的懷抱。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

RISC

+關(guān)注

關(guān)注

6文章

461瀏覽量

83653 -

RISC架構(gòu)

+關(guān)注

關(guān)注

0文章

5瀏覽量

5361 -

RISC-V

+關(guān)注

關(guān)注

44文章

2228瀏覽量

46025

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

RISC-V內(nèi)核是如何與FPGA內(nèi)核進(jìn)行資源共享的?

我們知道RISC-V內(nèi)核支持的精簡指令集,F(xiàn)PGA又是要求性能相對(duì)比較高的模塊,這兩者在同一個(gè)產(chǎn)品中可否共存?若能,兩者的資源又是通過哪些接口進(jìn)行傳輸共享的呢?

發(fā)表于 10-27 17:05

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

加入RISC-VAdvocate行列!我們正在尋找來自世界各地的RISC-V愛好者,通過全球推廣和參與,成為支持RISC-V進(jìn)步的關(guān)鍵參與者。作為一名RISC-VAdvocate,您將

萬物智聯(lián)時(shí)代,RISC-V與AI的融合之路該如何走?

人工智能與機(jī)器學(xué)習(xí)專委會(huì)主席謝濤發(fā)表了《萬物智聯(lián)時(shí)代RISC-V+AI之路》演講,分析了RISC-V與AI技術(shù)的結(jié)合及其發(fā)展路徑探索。他在發(fā)言中,盡管國產(chǎn)AI芯片在硬件

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

沁恒在歷屆峰會(huì)上分享RISC-V在MCU領(lǐng)域的創(chuàng)新成果,和大家共同見證了本土RISC-V產(chǎn)業(yè)的成長。早在第一屆RISC-V中國峰會(huì)上,沁恒就公開了青稞RISC-V系列量產(chǎn)芯片的關(guān)鍵技術(shù)

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

01 老朋友伴您走過每一屆峰會(huì)

沁恒在歷屆峰會(huì)上分享RISC-V在MCU領(lǐng)域的創(chuàng)新成果,和大家共同見證了本土RISC-V產(chǎn)業(yè)的成長。早在第一屆RISC-V中國峰會(huì)上,沁恒就公開了青稞RISC-

發(fā)表于 08-30 17:37

2024 RISC-V 中國峰會(huì):華秋電子助力RISC-V生態(tài)!

第四屆RISC-V中國峰會(huì)(RISC-V Summit China 2024)于8月21日至23日在杭州盛大召開,成為RISC-V領(lǐng)域的一次重要盛會(huì)

2024 RISC-V 中國峰會(huì):華秋電子助力RISC-V生態(tài)!

第四屆RISC-V中國峰會(huì)(RISC-V Summit China 2024)于8月21日至23日在杭州盛大召開,成為RISC-V領(lǐng)域的一次重要盛會(huì)。峰會(huì)匯聚了RISC-V國際基金會(huì)的

發(fā)表于 08-26 16:46

risc-v的發(fā)展歷史

RISC-V的發(fā)展歷史可以追溯到2006年左右,當(dāng)時(shí)David Patterson和其他研究者開始探索創(chuàng)建一個(gè)開放和可擴(kuò)展的指令集架構(gòu)(ISA)。以下是RISC-V發(fā)展的主要里程碑:

一、起源與初步

發(fā)表于 07-29 17:20

rIsc-v的缺的是什么?

RISC-V作為一種開源的指令集架構(gòu)(ISA),自其誕生以來就受到廣泛關(guān)注和應(yīng)用,但它也存在一些不足之處。以下是RISC-V架構(gòu)目前存在的主要缺點(diǎn):

1. 性能問題

相對(duì)于專用ISA的性能差距:盡管

發(fā)表于 07-29 17:18

RISC-V的MCU與ARM對(duì)比

開發(fā)者提供了豐富的資源和支持,降低了開發(fā)難度和成本。

成本

RISC-V :由于RISC-V是開源的,因此使用RISC-V的MCU可以顯著降低芯片設(shè)計(jì)和制造的費(fèi)用。此外,

發(fā)表于 05-27 15:58

RISC-V有哪些優(yōu)點(diǎn)和缺點(diǎn)

RISC-V作為一種開源的指令集架構(gòu)(ISA),具有一系列顯著的優(yōu)點(diǎn)和潛在的缺點(diǎn)。以下是RISC-V的主要優(yōu)點(diǎn)和缺點(diǎn)概述:

優(yōu)點(diǎn):

開源與開放性:RISC-V是開源的,這意味著任何人都可以獲取、修改

發(fā)表于 04-28 09:03

解鎖RISC-V技術(shù)力量丨曹英杰:RISC-V與大模型探索

4月12日,第二期“大家來談芯|解鎖RISC-V技術(shù)力量”在上海臨港新片區(qū)頂科永久會(huì)址舉辦,本期沙龍聚焦RISC-V技術(shù),圍繞AI時(shí)代的RISC-V市場(chǎng)機(jī)會(huì)、RISC-V在汽車領(lǐng)域的應(yīng)

什么是RISC-V?RISC-V的關(guān)鍵技術(shù)

RISC-V不僅僅是一個(gè)流行語;它建立在堅(jiān)實(shí)的技術(shù)基礎(chǔ)之上,使其有別于其他指令集架構(gòu) (ISA)。RISC-V的核心是基于精簡指令集計(jì)算(RISC)原則,強(qiáng)調(diào)效率和性能。

發(fā)表于 03-26 09:34

?3413次閱讀

什么是RISC-V

siFive搞RISC-V

賽昉搞RISC-V

香山搞RISC-V

到底什么是RISC-V?

先不問有什么用,RISC-V目前的能力來說,工

發(fā)表于 02-02 10:41

從授權(quán)到自研內(nèi)核,汽車MCU大廠倒戈RISC-V?

電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))隨著芯片IP行業(yè)的日新月異的局勢(shì),不少芯片大廠都對(duì)新的設(shè)計(jì)架構(gòu)躍躍欲試。比如汽車MCU大廠瑞薩就在近日宣布,將趕在競爭對(duì)手之前,推出第一代自研的32位RISC-V

設(shè)計(jì)資源傾斜,大廠們的RISC-V之路

設(shè)計(jì)資源傾斜,大廠們的RISC-V之路

評(píng)論