一、高斯白噪聲

高斯噪聲:是一種隨機噪聲,其時域內的信號幅度的統計規律服從高斯分布。

白噪聲:信號的功率譜在整個頻域內為常數的噪聲。

帶限白噪聲:帶寬限制在一定范圍內的高斯白噪聲。

二、產生方法

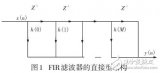

傳統的高斯白噪聲的產生是將多個m序列通過D/A轉換器,然后通過濾波器得到,比較繁瑣。本項目將通過線性反饋移位寄存器和FIR濾波器完成。

首先通過matlab中wgn函數生成高斯白噪聲,并將生成的噪聲數據存入到rom中,然后通過LFSR產生m序列偽隨機碼作為rom地址對噪聲數據進行讀取增加其隨機性,最后將輸出的隨機噪聲通過FIR濾波器得到帶限白噪聲。

三、線性反饋移位寄存器(LFSR)

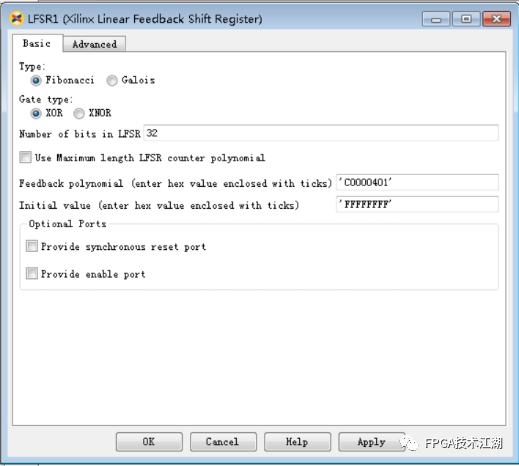

偽隨機碼的性能指標直接影響產生白噪聲的隨機性。本設計采用xilinx提供的LFSR IP核來實現。

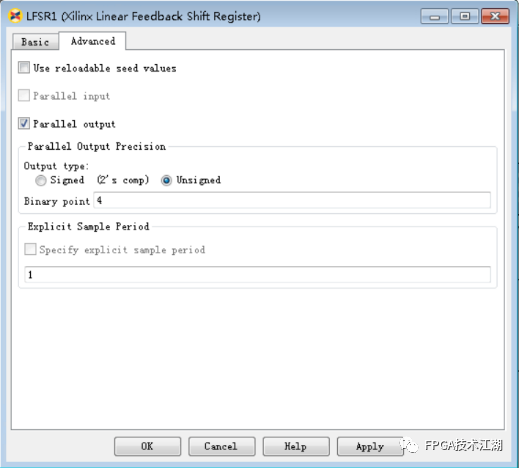

LFSR可以通過如圖方式進行配置,可選擇輸出的數據類型、位寬、小數位等。

本設計選擇數據類型為UFIX_32_4,然后再通過convert對其進行截位,得到UFIX_10_0的數據輸出作為ROM地址,再一次提高了隨機性。

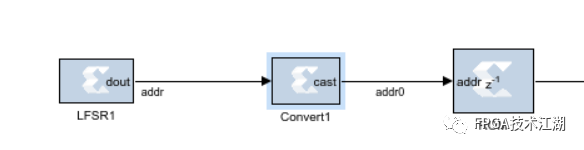

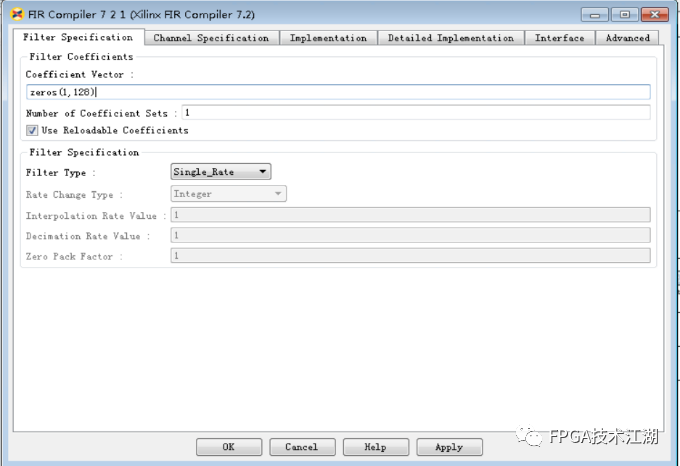

四、FIR濾波器系數重載

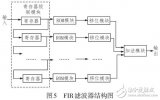

該部分濾波器的設計選擇Use Reloadable Coefficients模式,接收系統發送的濾波器系數,產生可變帶寬的帶限噪聲信號。

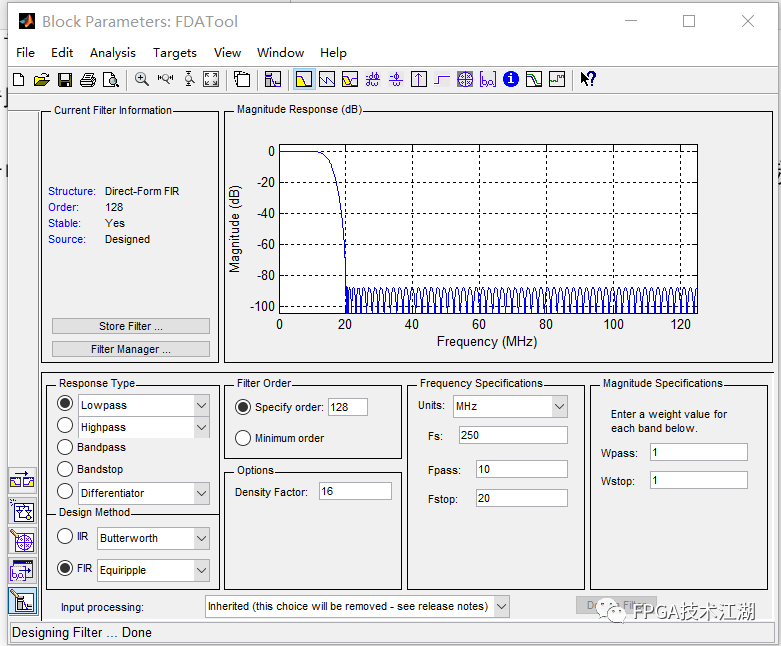

使用可重新加載的濾波器系數時,需將內部系數設置成相同長度的0,然后借助FDATools設計并導出濾波器系數。

本設計中低通FIR濾波器使用等波紋法設計、128階,250M采樣率、通帶頻率10M、截止頻率20M。

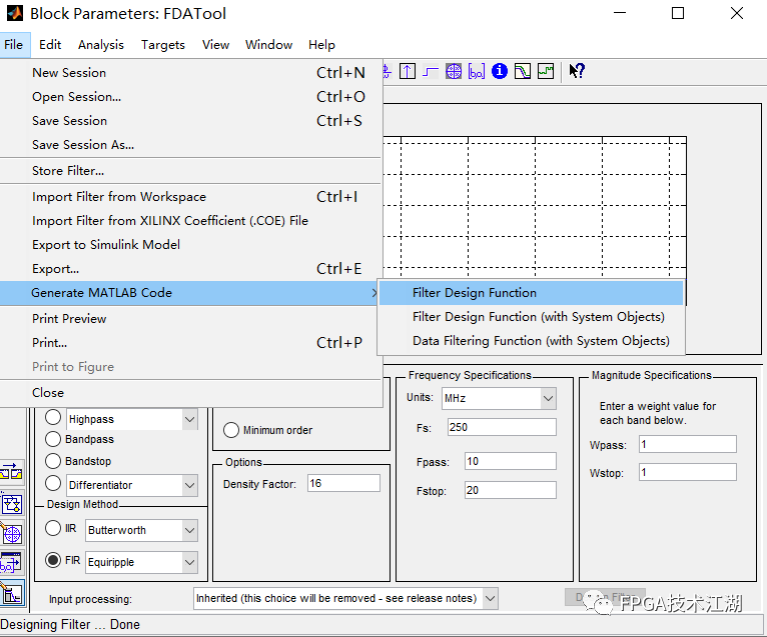

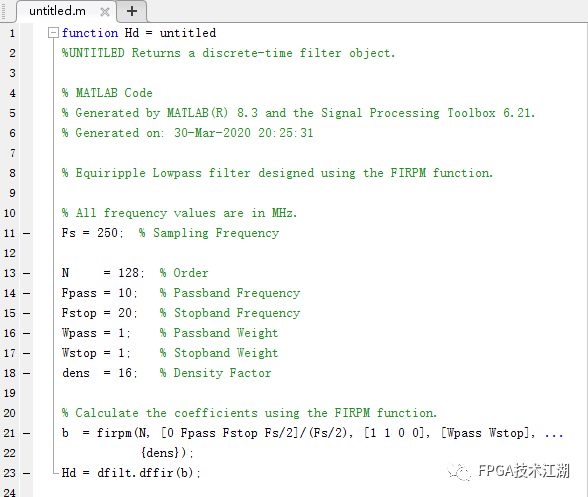

設計完成后可通過下圖操作將系數生成.m文件,然后就可以作為重載系數輸入到濾波器中了。

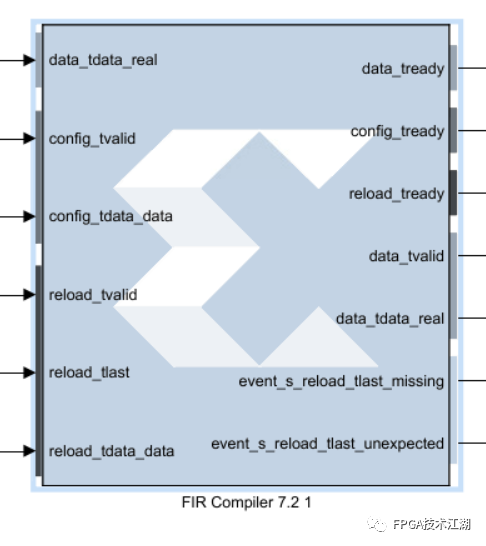

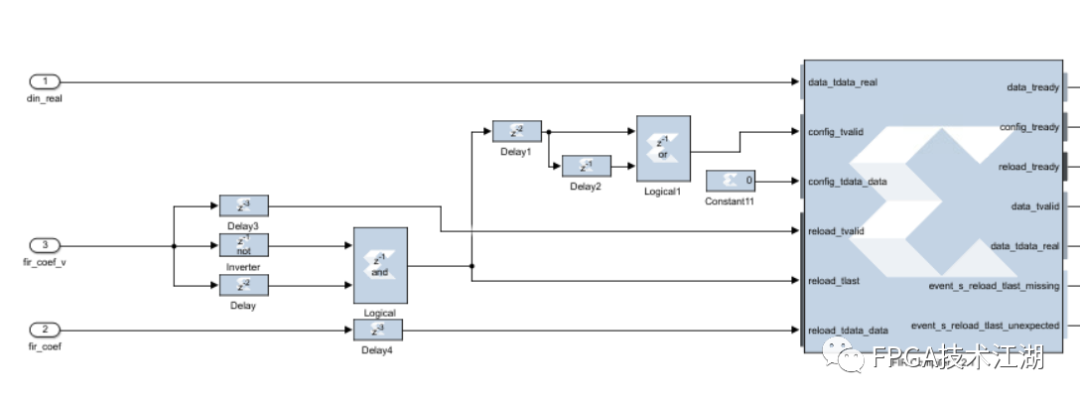

濾波器設置成系數重載模式時,需控制的接口如下圖;

其中data_tdata_real即為輸入的數據,reload_tdata_data為輸入的系數。

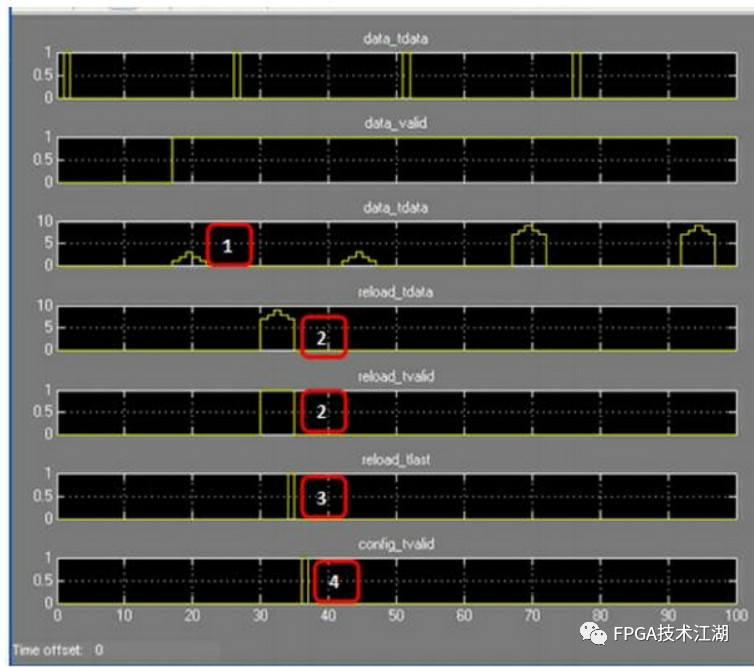

其接口時序圖如下圖所示:

按照時序要求配置FIR濾波器:

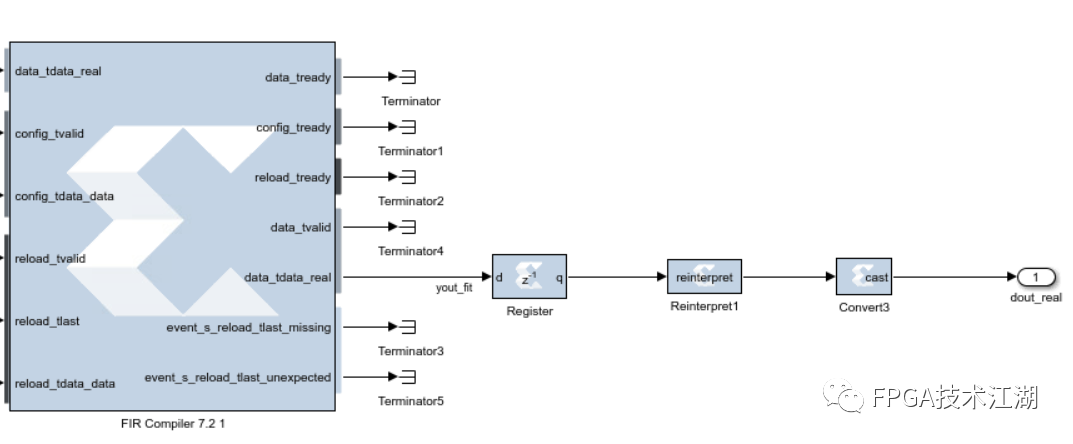

然后對輸出數據的位寬和類型進行調整得到結果。

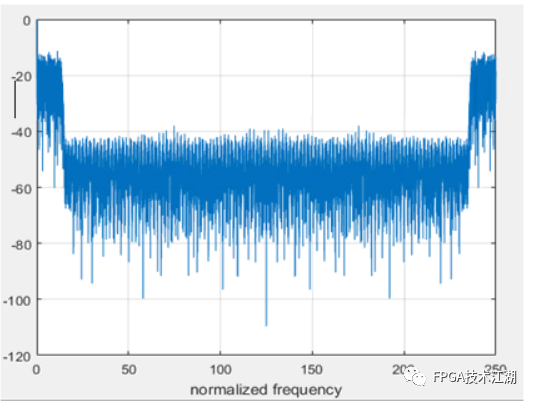

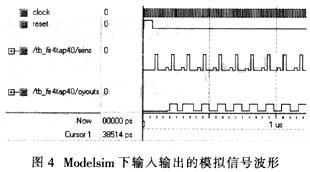

最后得到的帶寬為10M的帶限白噪聲:

審核編輯:劉清

-

matlab

+關注

關注

182文章

2963瀏覽量

230192 -

ROM

+關注

關注

4文章

562瀏覽量

85679 -

移位寄存器

+關注

關注

2文章

258瀏覽量

22238 -

fir濾波器

+關注

關注

1文章

95瀏覽量

19027 -

高斯白噪聲

+關注

關注

0文章

6瀏覽量

7734

原文標題:往期精選:基于FIR濾波器的帶限白噪聲的設計

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用FPGA構建的數字濾波器設計方案

FIR濾波器FAQ原理簡述

基于FPGA的FIR濾波器設計與實現

基于MATLAB與QUARTUS II的FIR濾波器該怎么設計?

fir濾波器的設計和實現

FIR并行濾波器設計

高效FIR濾波器的設計與仿真-基于FPGA

采用DSPBuilder的FIR濾波器的方案實現

基于優化神經網絡的FIR濾波器的設計方案

FIR數字濾波器設計方案

FIR濾波器的FPGA設計與實現

基于FIR濾波器的帶限白噪聲的設計方案實現

基于FIR濾波器的帶限白噪聲的設計方案實現

評論