理解PCIe配置對性能的影響

PCIe用途

當PCIe 應用于網卡和主機間通信時,網絡適配器需要與 CPU 和內存(以及其他模塊)進行通信。這意味著為了處理網絡流量,應該對通過 PCIe 進行通信的不同設備進行良好配置。將網絡適配器連接到 PCIe 時,它會自動協商網絡適配器和 CPU 之間支持的最大功能。

PCIe 屬性

任何 PCI 設備都加載了某些屬性。其中一些屬性對性能至關重要。設備的 PCIe 屬性是通過系統和設備能力之間的協商來設置的。這導致兩者都可以支持被選擇的最高值。下面,您可以找到相關 PCIe 屬性的說明、如何驗證它們以及它們對性能的影響。

PCIe 寬度

PCIe 寬度決定了設備可并行用于通信的 PCIe 通道數。寬度標記為 xA,其中 A 是通道數(例如,x8 表示 8 通道)。具體支持多少通道取決于廠商的設備和它們的型號。為了驗證 PCIe 寬度,可以使用命令 lspci。

在本例中,我們在 PCI 04.00.0 地址上安裝了 Mellanox 適配器。

# lspci -s 04:00.0 -vvv | grep Width LnkCap: Port #0, Speed 8GT/s, Width x8, ASPM not supported, Exit Latency L0s unlimited, L1 unlimited LnkSta: Speed 8GT/s, Width x8, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

如您所見,PCIe 報告了已通信的設備功能(在 LnkCap 下),以及它們的當前狀態(在 LnkSta 下),這是實際的 PCIe 設備屬性。

PCIe 速度

確定可能的 PCIe 事務數。速度以 GT/s 為單位,代表“每秒十億次交易”。與 PCIe 寬度一起確定了最大 PCIe 帶寬(速度 * 寬度)。為了驗證 PCIe 速度,可以使用命令 lspci。

# lspci -s 04:00.0 -vvv | grep Speed LnkCap: Port #0, Speed 8GT/s, Width x8, ASPM not supported, Exit Latency L0s unlimited, L1 unlimited LnkSta: Speed 8GT/s, Width x8, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt

與寬度參數類似,設備能力和狀態都會被報告。

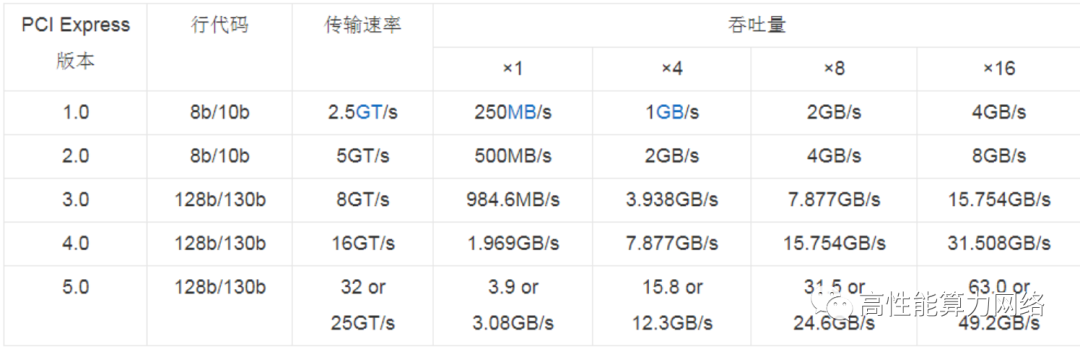

PCIe 速度被標識為“代”,其中 2.5GT/s 稱為“gen1”,5GT/s 稱為“gen2”,8GT/s 稱為“gen3”,16GT/s 稱為“gen4”.

注意:除了支持的速度之外,各代之間的主要區別在于數據包的編碼開銷。對于第 1 代和第 2 代,在 PCIe 上發送的每個數據包都有 20% 的 PCIe 標頭開銷。這在第 3 代中得到了改進,其中開銷減少到 1.5% (2/130)。有關更多詳細信息,請參閱下面的實際 PCIe 帶寬計算。

PCIe Max Payload Size

PCIe Max Payload Size 確定 PCIe 數據包或 PCIe MTU 的最大大小(類似于網絡協議)。這意味著較大的 PCIe 事務被分解為 PCIe MTU 大小的數據包。此參數僅由系統設置,取決于芯片組架構(例如 x86_64、Power8、ARM 等)。您可以使用命令 lspci(在 DevCtl 下指定)查看 PCIe Max Payload Size。

lspci -s 04:00.0 -vvv | grep DevCtl: -C 2 DevCap: MaxPayload 512 bytes, PhantFunc 0, Latency L0s unlimited, L1 unlimited ExtTag+ AttnBtn- AttnInd- PwrInd- RBE+ FLReset+ DevCtl: Report errors: Correctable- Non-Fatal+ Fatal+ Unsupported- RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop+ FLReset- MaxPayload 256 bytes, MaxReadReq 4096 bytes

PCIe Max Read Request

PCIe Max Read Request 確定允許的最大 PCIe 讀取請求。由于必須為傳入響應準備緩沖區,PCIe 設備通常會跟蹤待處理的讀取請求的數量。PCIe 最大讀取請求的大小可能會影響待處理請求的數量(當使用大于 PCIe MTU 的數據獲取時)。同樣,使用命令 lspci 來查詢 Max Read Request 值。

# lspci -s 04:00.0 -vvv | grep MaxReadReq MaxPayload 256 bytes, MaxReadReq 4096 bytes

與此處討論的其他參數相反,可以在運行時使用命令 setpci 更改 PCIe Max Read Request:首先,查詢該值以避免覆蓋其他屬性:

# setpci -s 04:00.0 68.w 5936

第一個數字是 PCIe Max Read Request。設置選Max Read Request:

# setpci -s 04:00.0 68.w=2936

該值應使用命令 lspci 更新:

# lspci -s 04:00.0 -vvv | grep MaxReadReq MaxPayload 256 bytes, MaxReadReq 512 bytes

可接受的值為:0 -128B、1 - 256B、2 - 512B、3 - 1024B、4 - 2048B 和 5 - 4096B。

計算 PCIe 帶寬限制

如前所述,PCIe 功能可能會影響網絡適配器的性能。最好了解 PCIe 引入的帶寬限制。下面是理論計算和幾個例子。

最大可能的 PCIe 帶寬是通過乘以 PCIe 寬度和速度來計算的。從這個數字中,我們減少了大約 1Gb/s 的糾錯協議和 PCIe 標頭開銷。開銷由 PCIe 編碼(有關詳細信息,請參閱 PCIe 速度)和 PCIe MTU 確定:

最大 PCIe 帶寬 = 速度 * 寬度 * (1 - 編碼) - 1Gb/s。

例如,具有 x8 寬度的第 3 代 PCIe 設備將被限制為:

最大 PCIe 帶寬 = 8G * 8 * (1 - 2/130) - 1G = 64G * 0.985 - 1G = ~62Gb/s。

另一個示例 - 具有 x16 寬度的第 2 代 PCIe 設備將被限制為:

最大 PCIe 帶寬 = 5G * 16 * (1 - 1/5) - 1G = 80G * 0.8 - 1G = ~63Gb/s。

注意:PCIe 事務包括網絡數據包有效負載和標頭,因此在計算網絡流量的 PCIe 限制時需要考慮它們。

PCIe Max Read Request 和 Max Payload Size 可能會由于 PCIe 整體增加和相同負載的待處理事務而導致事務速率限制。

審核編輯:黃飛

-

cpu

+關注

關注

68文章

10824瀏覽量

211135 -

內存

+關注

關注

8文章

2998瀏覽量

73881 -

PCIe

+關注

關注

15文章

1217瀏覽量

82436 -

網絡適配器

+關注

關注

0文章

41瀏覽量

11539

原文標題:性能調優之PCIe配置

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

最新可用隔離元件的性能提升如何幫助替代架構在不影響安全性的前提下提升系統性能

PCIe配置優化:提升系統性能的關鍵步驟

PCIe配置優化:提升系統性能的關鍵步驟

評論