耀創(chuàng)科技U-Creative|Cadence Channel Partner在幫助客戶解答PSpice軟件使用問題超過15年,客戶經(jīng)常會(huì)提到仿真收斂性問題,因此,通過發(fā)表此文詳解PSpice中的收斂性問題及其與之相關(guān)因素,希望對(duì)各位有所幫助,文章如有未詳盡表述清楚的地方,請(qǐng)指正。

在PSpice中進(jìn)行電路仿真時(shí),常會(huì)遇到仿真不收斂的問題(簡(jiǎn)稱收斂性問題)。當(dāng)電路中包含晶體管等非線性器件,在進(jìn)行bias point、DC sweep和瞬態(tài)分析時(shí),PSpice軟件內(nèi)部使用Newton-Raphson算法進(jìn)行迭代計(jì)算來(lái)解一組非線性方程。在個(gè)別情況下, PSpice 軟件采用上述算法未能得到非線性方程的解,使得仿真不能進(jìn)行下去,這就是“收斂性問題”。

本文將介紹收斂性問題的原因,并針對(duì)性地提供解決方法。

首先,電路收斂需要滿足以下條件:

1. 非線性方程存在有解:確保電路設(shè)計(jì)是正確無(wú)誤的,以保證非線性方程存在有解。

2. 方程必須是“連續(xù)的”:確保電路模型在所有分析點(diǎn)上都是連續(xù)且可導(dǎo)的。

3. 對(duì)方程能進(jìn)行求導(dǎo)計(jì)算:保證所使用的模型是可以進(jìn)行求導(dǎo)計(jì)算的。

4. 迭代采用的初始解與最終解的偏離不應(yīng)過大:提供一個(gè)合理的初始解,避免初始解與最終解相差過大。

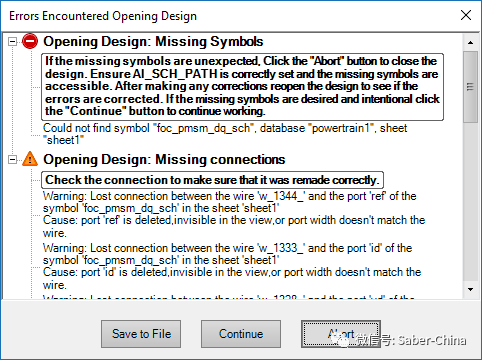

如果在PSpice仿真設(shè)計(jì)過程中遇到收斂性問題,程序會(huì)產(chǎn)生一個(gè)輸出文件,其中包含了錯(cuò)誤提示和最后嘗試的節(jié)點(diǎn)電壓信息。查看輸出文件可以分析收斂性問題的具體原因,并采取相應(yīng)的解決措施。

格式如下:

起始提示:ERROR--convergence problem……)

和最后的記錄(Last node voltages tried were……)

關(guān)于“數(shù)值范圍及精度”

PSpice中還存在數(shù)值范圍和精度問題:

1.PSpice中電壓和電流的數(shù)值范圍分別為+/-1e10 volts和+/-1e10 amps,

2. PSpice中導(dǎo)數(shù)的范圍為1e14。

3. PSpice中數(shù)值采用雙精度,可以達(dá)到15位有效數(shù)字。

如果數(shù)值超出允許范圍,將會(huì)導(dǎo)致收斂性問題。

例1:當(dāng)一個(gè)1MV的電壓源加在一個(gè)阻值為1微歐姆的電阻兩端時(shí),電流將達(dá)到1e12安培,超出了+/- 1e10安培的電流值范圍,從而導(dǎo)致電路不收斂的問題。

例2:對(duì)于下面模擬情況,電壓直接加在二極管兩端,沒有串聯(lián)電阻,將導(dǎo)致不收斂的問題。

V1 1, 0 5v

D1 1, 0 DMOD

.MODEL DMOD(IS=1e-16)

關(guān)于”導(dǎo)數(shù)”

PSpice內(nèi)部的器件方程包括一些求導(dǎo)式,例如計(jì)算小信號(hào)電導(dǎo)、跨導(dǎo)及增益。如果器件模型方程和導(dǎo)數(shù)出現(xiàn)不連續(xù)情況,將導(dǎo)致下述問題:

在不連續(xù)點(diǎn)處將不能正常計(jì)算出導(dǎo)數(shù)值。

第n次迭代中計(jì)算的“電導(dǎo)值” 將不能成為下一次迭代的合適“初值”。

此外,對(duì)于電路拓?fù)潢P(guān)系、元器件模型和初始解等方面也需要注意,以保證電路的收斂性。

電路拓?fù)潢P(guān)系:

1、檢查電路連接關(guān)系是否正確

2、避免單位差錯(cuò)。例如將1MEGAOHMS 誤寫為1M

3、電路中存在浮置節(jié)點(diǎn),不能保證足夠的直流通路。

4、描述受控源的時(shí)要使用現(xiàn)實(shí)可能的增益值,模型參數(shù)值也應(yīng)合理。

5、避免使用邏輯元件。如果必須使用邏輯元件,應(yīng)該給相應(yīng)的節(jié)點(diǎn)設(shè)置一個(gè)與實(shí)際值一致的初值。

設(shè)置值不應(yīng)為0。

元器件模型:

1、對(duì)半導(dǎo)體器件,要保證模型參數(shù)值是現(xiàn)實(shí)可能的,并確保計(jì)算出的電壓和電流值在+/- 1e10的范圍內(nèi)。

2、當(dāng)電源電壓接近零時(shí),受控源應(yīng)該“斷開”。

3、對(duì)p-n器件,要注意串聯(lián)電阻設(shè)置值不應(yīng)為0。

初始解:

1、為了保證Newton-Raphson迭代的收斂,初始解與最終解的差距不應(yīng)過大

2、功率電子電路可以允許電壓/電流有較大的容差,如果電流超過幾安培,可以將ABSTOL值設(shè)置為1u。

3、如果ABSTOL設(shè)置值超過1u將導(dǎo)致收斂性問題。除非電路中的電流達(dá)到“千安培”。

4、并非任何情況下只要放寬容差均可以保證收斂,例如,將容差選項(xiàng)RELTOL設(shè)置值大于1.0仍然會(huì)出現(xiàn)收斂性問題。

5、將GMIN值設(shè)置為1n和10n之間通常會(huì)解決收斂性問題。

PSpice對(duì)電路進(jìn)行模擬時(shí),最關(guān)鍵的問題是首先要計(jì)算直流工作點(diǎn)。PSpice首先按照電源的實(shí)際電壓值計(jì)算工作點(diǎn),通常均能得到確定解。如果出現(xiàn)不收斂的問題, PSpice隨即將電源的電壓值幾乎降為0 (.001%)使所有非線性元器件均處于截止?fàn)顟B(tài)。

以上是關(guān)于收斂性問題及其解決方案的介紹。通過了解收斂性問題的原因和相關(guān)因素,我們可以更好地應(yīng)對(duì)PSpice中的設(shè)計(jì)挑戰(zhàn),并成功進(jìn)行電路仿真分析。

結(jié)論

Cadence PSpice是一款功能強(qiáng)大的電路仿真軟件,它結(jié)合了業(yè)界領(lǐng)先的模擬、模數(shù)混合信號(hào)以及分析工具,為電路仿真提供了一個(gè)完整的解決方案。內(nèi)置各種強(qiáng)大的電路圖繪制功能,可用于電子線路、電路和信號(hào)與系統(tǒng)等可以實(shí)現(xiàn)交流分析、直流工作點(diǎn)分析、直流掃描分析和轉(zhuǎn)移函數(shù)分析等多種功能,還可以用于電子線路、電路、信號(hào)的仿真分析和電路驗(yàn)證。

簡(jiǎn)單來(lái)說,PSpice的優(yōu)點(diǎn)就是:易學(xué)易用、簡(jiǎn)單直觀,適用于任何的電路設(shè)計(jì)工程師。

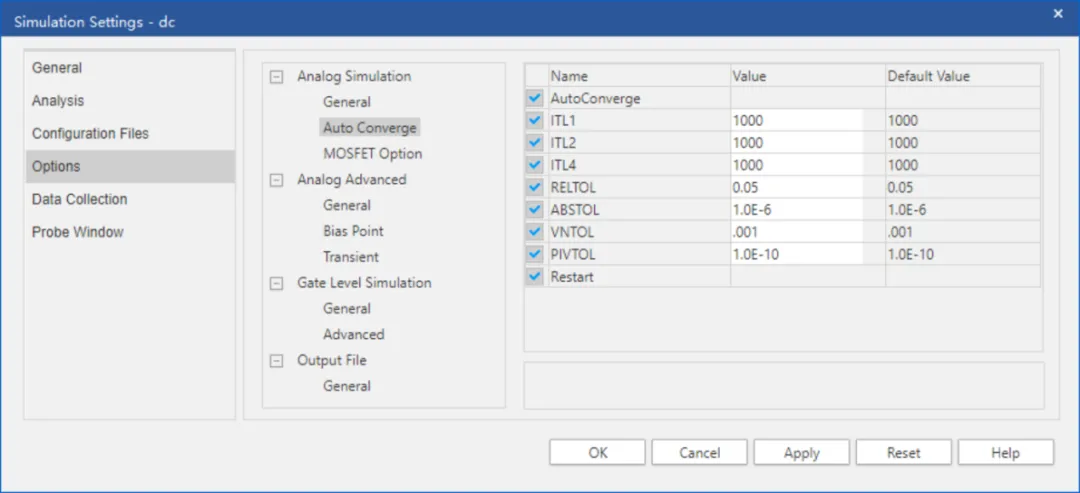

并且PSpice提供了Auto Converge(自動(dòng)收斂)工具,自動(dòng)調(diào)節(jié)仿真參數(shù)的值,使得電路的計(jì)算可以收斂。

-

電壓

+關(guān)注

關(guān)注

45文章

5567瀏覽量

115604 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

電路仿真

+關(guān)注

關(guān)注

36文章

207瀏覽量

95661

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Saber中如何更好地提高仿真的收斂性(一)

PSpice論文一---PSpice仿真中收斂問題的研究

Pspice收斂問題

決定仿真精度的主要因素

B值獨(dú)立同分布隨機(jī)變?cè)蛄芯赝耆?b class='flag-5'>收斂性

B值同分布鞅隨機(jī)列矩完全收斂性的注記

基于量子粒子群算法的收斂性研究

如何解決Saber中收斂性問題

板級(jí)模擬電路仿真收斂性技術(shù)研究

警示傳播算法收斂的充分條件

關(guān)系模型的進(jìn)化算法收斂性對(duì)比的詳細(xì)資料說明

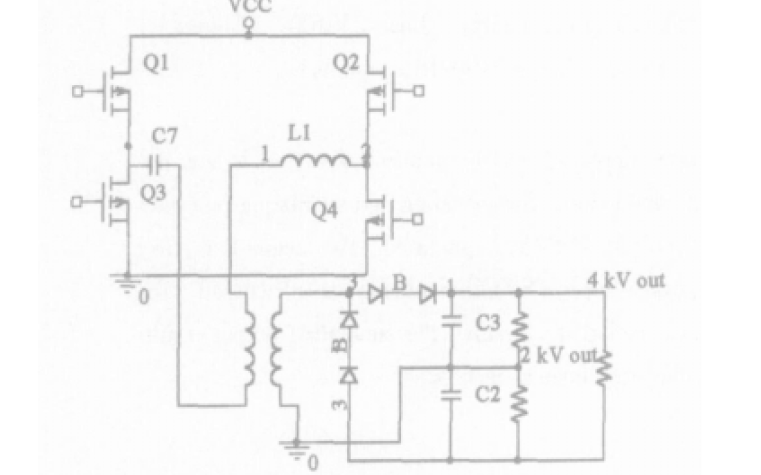

高壓大功率開關(guān)電源的PSPICE計(jì)算機(jī)輔助設(shè)計(jì)的實(shí)例說明

Saber Pspice simulink電源仿真軟件的區(qū)別

一文解讀GNSS信號(hào)對(duì)網(wǎng)絡(luò)中授時(shí)應(yīng)用的益處

一文解讀PSpice中的收斂性問題及其相關(guān)因素

一文解讀PSpice中的收斂性問題及其相關(guān)因素

評(píng)論