電子發燒友網報道(文/周凱揚)隨著信息安全受到的重視程度越來越高,不少國家和組織都推出了對應的法律和標準來規范芯片在個人數據隱私上的安全性。比如在汽車行業有ISO 21434,物聯網領域有ISO/IEC 27400:2022等。然而對于不同的芯片架構而言,實現安全的方式往往也不盡相同,比如Arm和RISC-V。

Arm TrustZone技術

經過多年的發展,Arm的TrustZone技術已經被應用在數十億顆應用處理器上,可以說這一安全設計保護著我們身邊各類設備的代碼和資料。因為該技術將硬件強制隔離技術集成在CPU中,所以為各大Arm處理器提供了系統級的高效安全方案,并利用該技術打造TEE(可信執行環境)。

通過TrustZone,可將SoC上的軟硬件資源分為安全和非安全兩個分區,需要保密的安全操作在安全分區執行,而一些OS、應用程序等操作則在非安全分區執行。在處理器的設計上,每個物理處理器核心都被分為一個安全核和非安全核兩個虛擬核。

得益于這一硬件隔離機制,Arm處理器可以將生物信息等敏感信息存儲在TrustZone內,比如指紋信息等,通過軟件管理程序來管理隔離分區。對于可信執行環境而言,需要滿足三個目標,包括數據保密性、數據完整性和代碼完整性。

RISC-V PMP技術

傳統的RISC-V處理器并沒有提供像Arm TrustZone這樣的隔離技術,但還是為開發者提供了安全拓展的能力,可以使用PMP、IOPMP等方式進一步加強RISC-V處理器對物理內存的保護。

PMP作為一種內存保護機制,可以用于M模式和S/U模式下的內存訪問,但只有M模式下才有權限配置PMP。通過至多16個CSR寄存器,可以配置至多16個Zone的內存訪問權限。如此一來,在操作系統中,PMP可以實現不同進程之間的內存隔離,避免一個進程訪問另一個進程的敏感數據。相比起Arm TrustZone的兩個分區,其軟件安全方案要更加靈活。

然而,PM只是對于CPU核心存取的一個保護機制,通常一個硬件平臺內,總線上還存在其他的I/O Agent,比如DSP/GPU、DMA、NIC等。攻擊者通過控制某個I/O Agent的軟件或者固件,可以避開PMP來竊取數據。

所以為了解決這個安全威脅,RISC-V需要通過增加IOPMP來完成對內存訪問的保護,不同的主設備與總線之間都需要增加一個IOPMP。IOPMP可以像PMP一樣定義訪問權限,檢查讀寫傳輸是否符合訪問規則。

寫在最后

業內對于處理器信息安全設計的探索,從來沒有止步過。得益于RISC-V架構的拓展性,不少廠商也都推出了自己的安全設計解決方案,此外也有單獨的硬件IP模塊,也有OpenTtitan、OP-TEE這樣的開源項目提供統一的芯片安全設計參考。未來隨著AI計算、量子計算的普及,芯片信息安全注定會面臨更大的挑戰,即便是現有的設計方案也要做好迭代的準備。

-

ARM

+關注

關注

134文章

8967瀏覽量

365036 -

信息安全

+關注

關注

5文章

641瀏覽量

38827 -

ISA

+關注

關注

0文章

53瀏覽量

43694 -

RISC-V

+關注

關注

44文章

2141瀏覽量

45711

發布評論請先 登錄

相關推薦

紫光同芯推出開放式架構安全芯片E450R

RISC--V架構的特點

交換芯片架構是什么意思 交換芯片架構怎么工作

fpga芯片架構介紹

專家訪談 | 汽車信息安全強標即將落地,企業該如何應對?(汽車安全①:信息安全)

【RISC-V開放架構設計之道|閱讀體驗】+ 閱讀深體驗

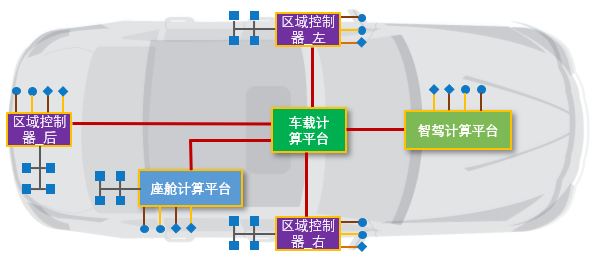

域架構下的功能安全思考

芯片信息安全,不同ISA架構的實現思路

芯片信息安全,不同ISA架構的實現思路

評論