09

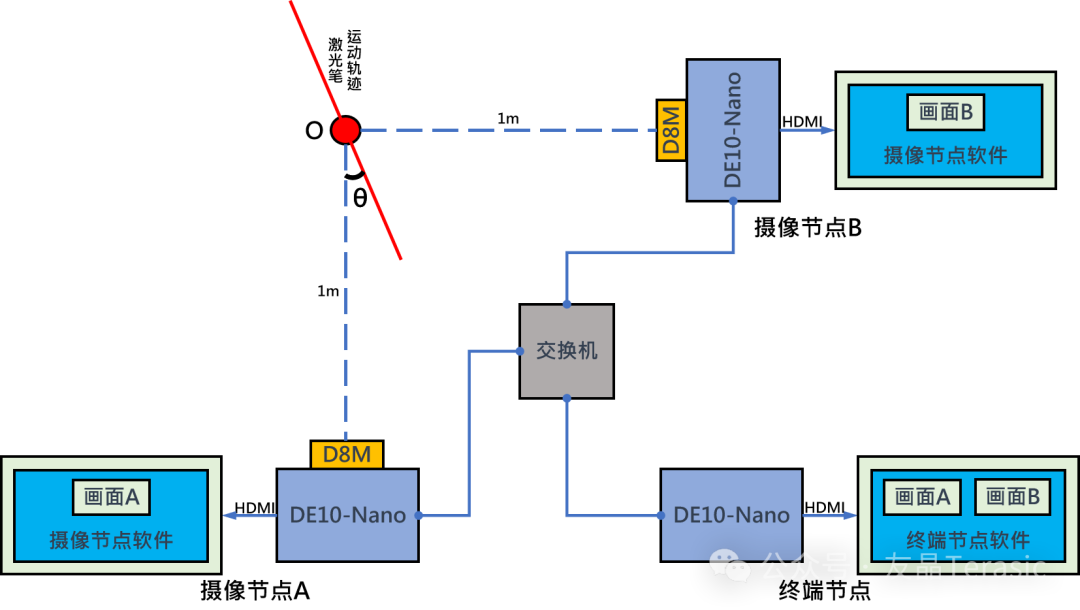

前面介紹了系統的硬件框圖如下:

硬件基本分為三塊,兩個攝像節點,一個終端節點。

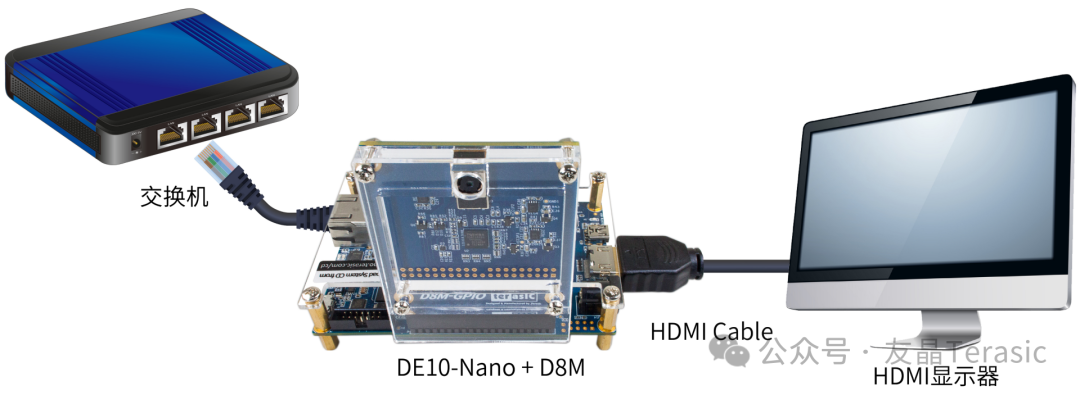

1. 攝像節點硬件

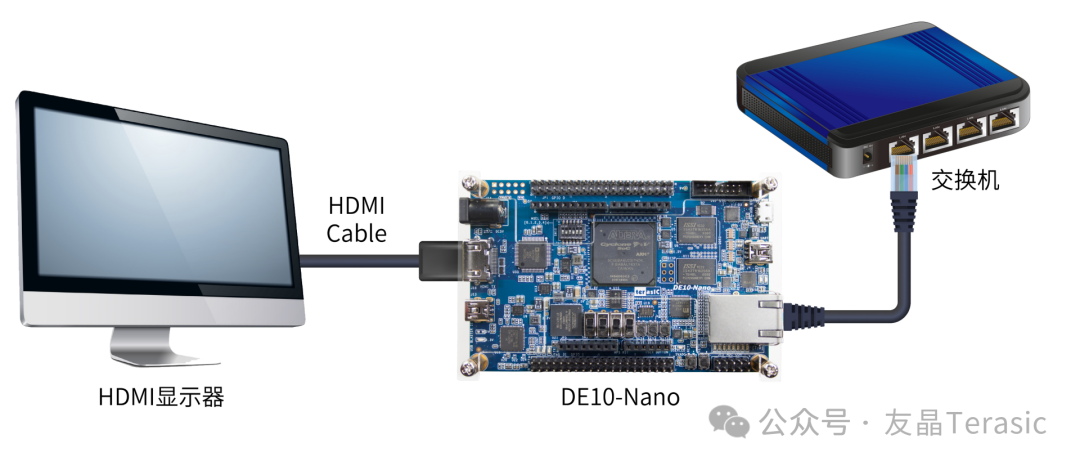

攝像節點由一個DE10-Nano開發板和一個D8M攝像頭實現,DE10-Nano開發板的HDMI接口外接HDMI顯示器來顯示拍攝到的視頻。

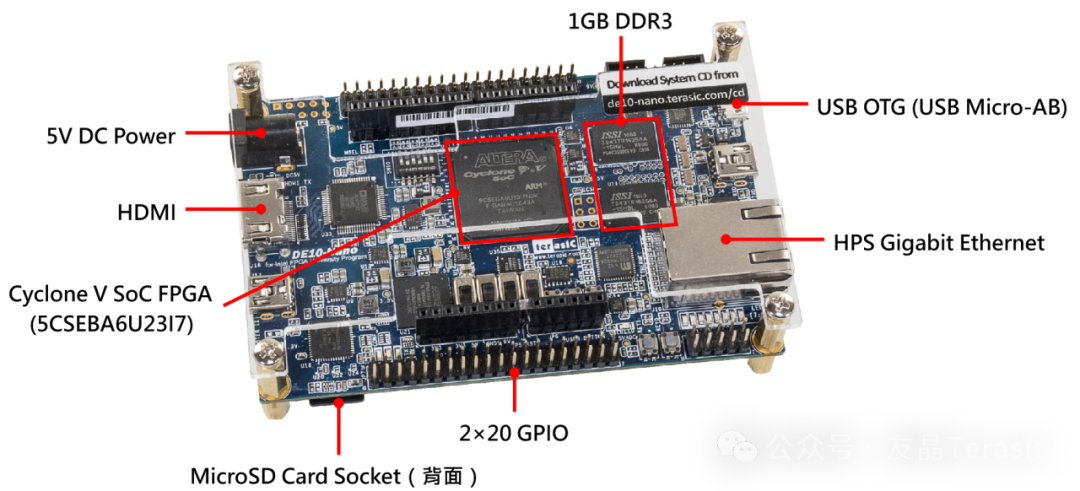

DE10-Nano開發板硬件

DE10-Nano開發板基于Cyclone V SoC FPGA,擁有110K邏輯單元和ARM Cortex A9雙核處理器,其FPGA資源可用于算法加速。

FPGA端包含HDMI接口,可連接HDMI顯示器顯示視頻;2×20的GPIO接口,可連接GPIO接口的子卡。

HPS端包含1GB容量的DDR3內存;USB OTG接口,支持USB攝像頭、鼠標、鍵盤等硬件;千兆以太網口,可實現網絡傳輸。

MicroSD卡插槽,可以插入燒寫了鏡像的SD卡,運行Linux系統。

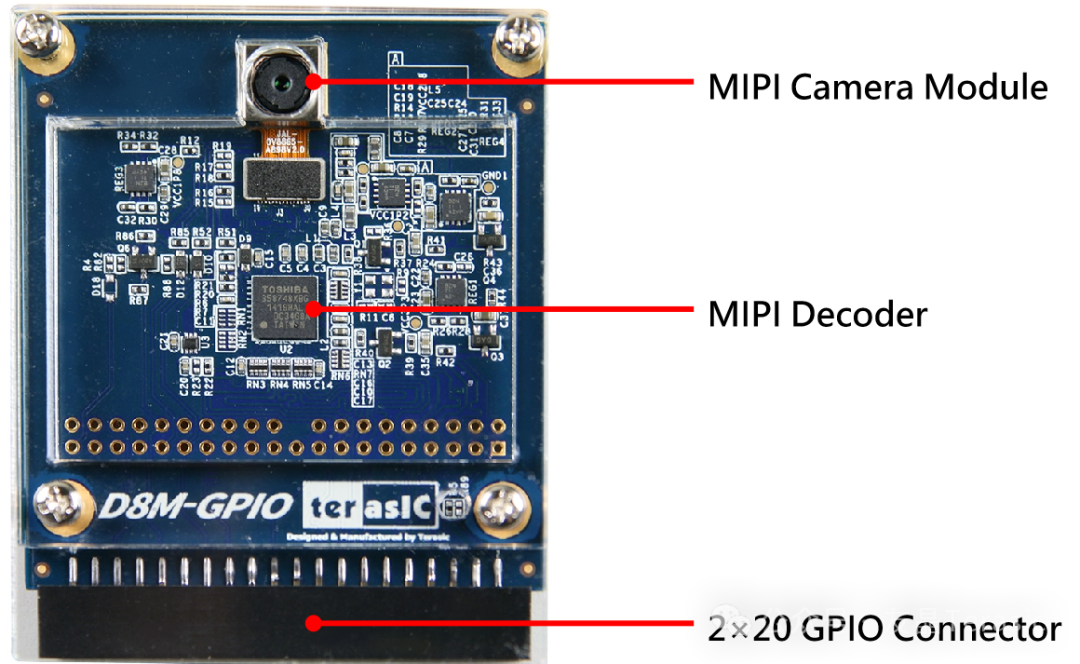

D8M攝像模塊硬件

D8M-GPIO是 一個2×20 pin GPIO接口的八百萬像素攝像頭子卡,包含MIPI Camera Module和MIPI Decoder。(Mobile Industry Processor Interface簡稱MIPI。)

MIPI Camera module拍攝視頻后輸出MIPI視頻信號數據包,通過MIPI decoder轉換成拜耳陣列(bayer pattern,10-bits parallel),最終由2x20 pin GPIO接口輸出。

2. 終端節點硬件

終端節點由一個DE10-Nano開發板實現,并外接HDMI顯示器來顯示攝像節點傳輸過來的視頻以及測量結果。并用聲光提示模塊發出聲光提示信息。

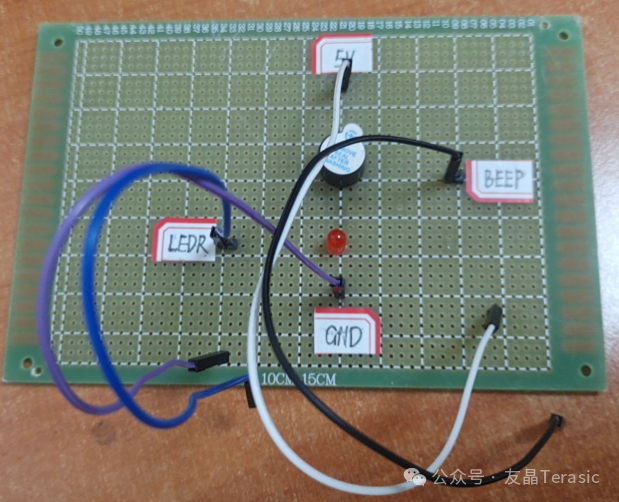

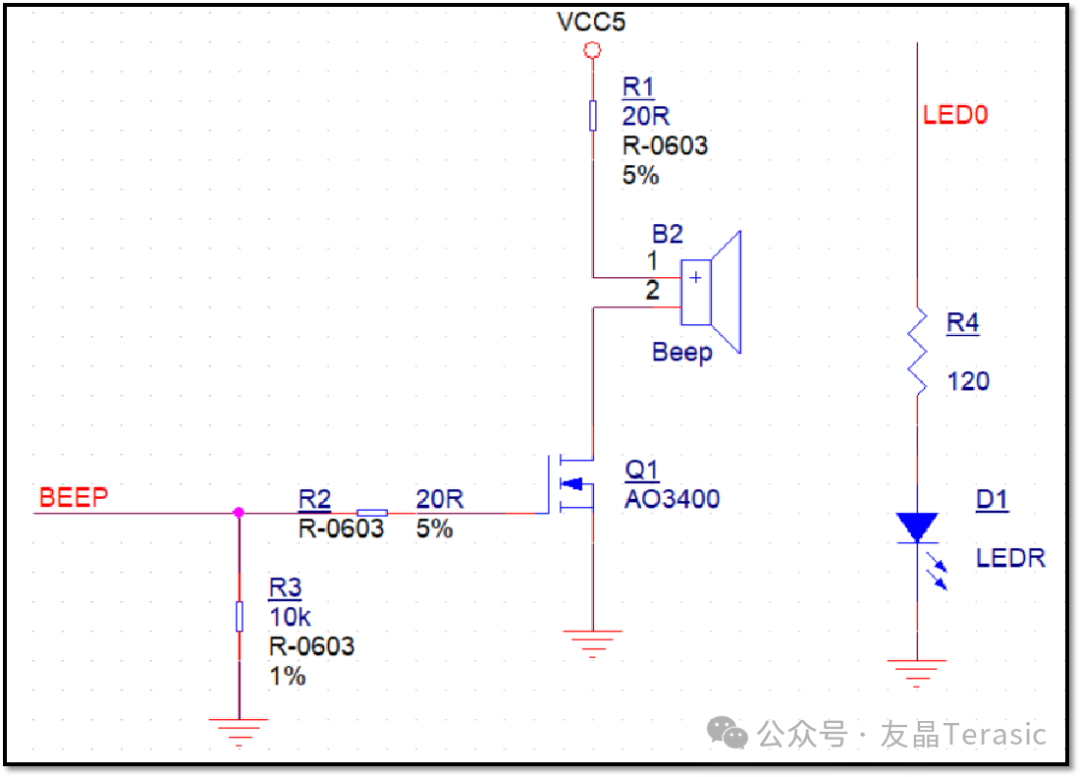

聲光提示電路

實現聲光提示功能的電路由一個蜂鳴器和一個紅色LED組成,這是一個簡單的蜂鳴器驅動模塊。

10

攝像節點程序設計

1. 攝像節點整體介紹

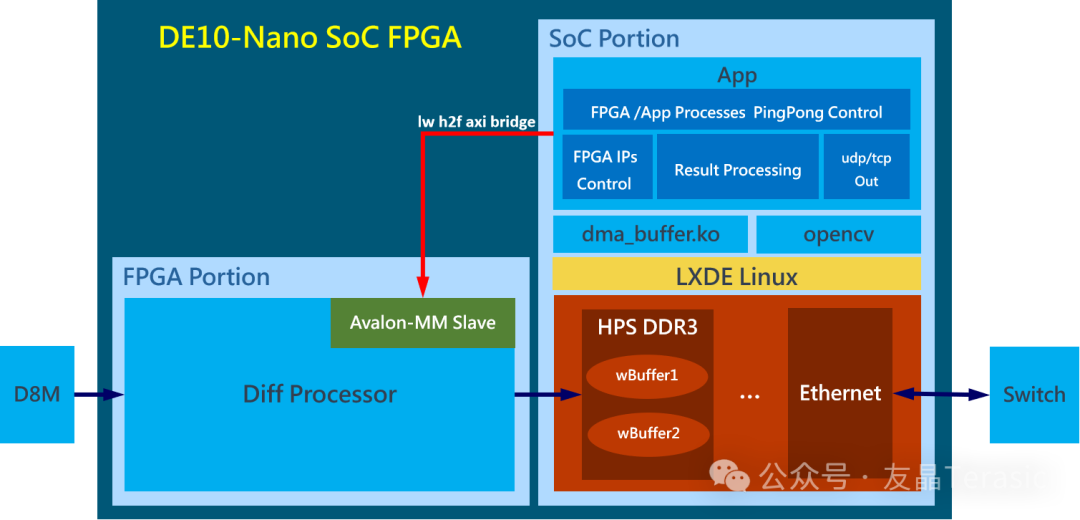

攝像節點程序包含FPGA和SoC兩部分,FPGA中實現了一個Diff Processor,Diff Processor獲取D8M攝像頭拍攝到的視頻流數據并進行處理,然后將處理的結果寫入HPS DDR3內存中。

SoC中的應用程序初始化Diff Processor中的IP并配置幀間差分法的閾值,通過乒乓控制決定將Diff Processor的結果寫入wBuffer1或wBuffer2,然后讀取wBuffer得到Diff Processor處理的結果再進行進一步的處理,最后將圖像結果通過UDP發送到終端節點,數據結果通過TCP發送到終端節點。

2. FPGA端的Diff Processor設計

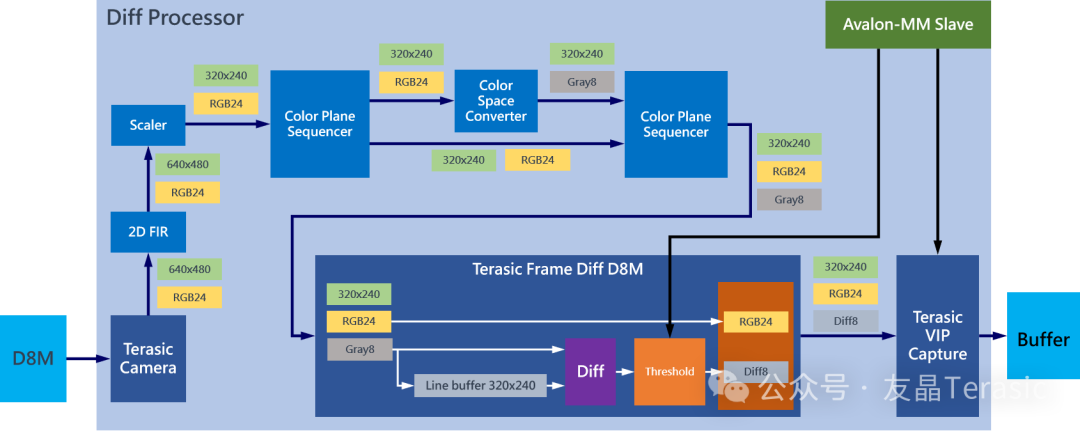

這是FPGA中Diff Processer的框圖,Diff Processer系統是使用Platform Designer工具搭建的,其中2D FIR(2D濾波)、Scaler(縮放)、Color Plane Sequencer(色彩平面定序器)、Color Space Converter(色彩空間轉換) IP為Quartus Prime軟件中已有的視頻處理IP;Terasic Camera、Terasic Frame Diff D8M、Terasic VIP Capture IP為友晶自定義IP。

Diff Processer的處理過程為:Terasic Camera將D8M攝像頭獲取的拜耳陣列轉換為RGB24圖像,大小為640×480,然后使用2D FIR進行濾波處理,再使用Scaler將圖像縮放為320×240,通過Color Plane Sequencer將圖像復制為兩份,一份保持不變,一份通過Color Space Converter將圖像轉換為灰度圖,再次通過Color Plane Sequencer將原圖像與灰度圖合并,得到320×240的RGB+Gray的4通道圖像。Terasic Frame Diff D8M處理圖像的過程為,Line Buffer緩存上一幀灰度圖,與當前幀的灰度圖做差分并判斷是否大于閾值,然后將幀間差分結果圖像與原圖像合并得到結果幀。最后用Terasic VIP Capture 將結果幀寫到Buffer。

Terasic Camera自定義IP用于實現將拜爾陣列轉換為RGB圖像,并將frame輸出為Avalon-ST(Avalon-Streaming,Avalon流)。

- Terasic Frame Diff D8M自定義IP采用Streaming協議處理1路輸入,使用Line buffer緩存,緩存幀與當前幀進行差分,還包含1路結果視頻流輸出;并且實現了控制寄存器,可以設置幀間差分法閾值變化。為了兼顧視頻流和數據集的采集,這里將原圖像與差分結果組合成4通道的圖像進行輸出。

Terasic VIP Capture自定義IP用于實現接收Streaming協議視頻流和動態切換指定目標buffer地址。

3. HPS端的C程序設計

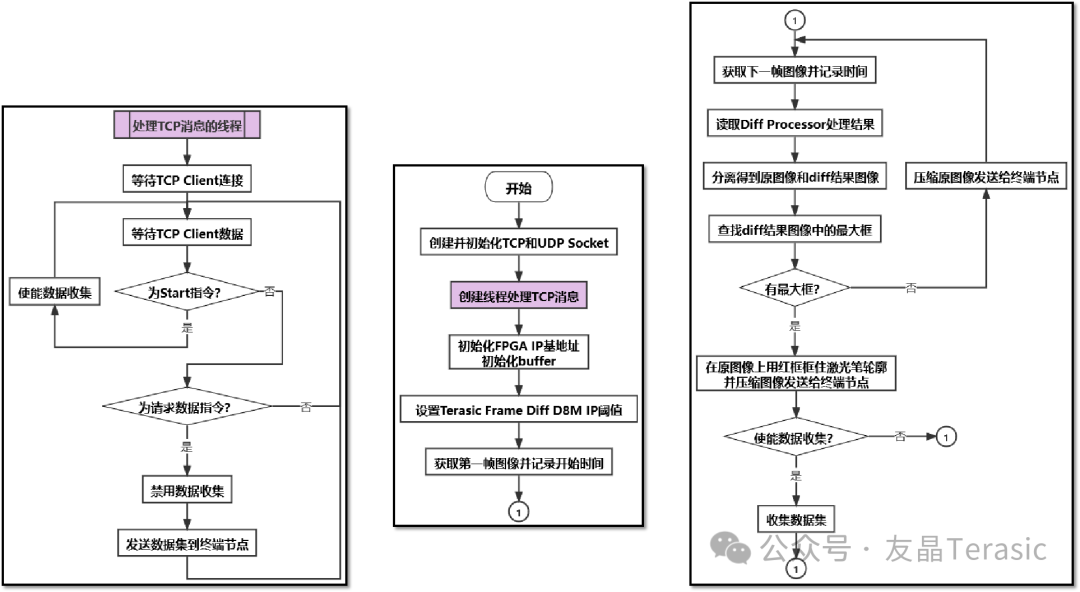

首先創建并初始化TCP和UDP Socket,TCP用來傳輸數據,UDP用來傳輸圖像,接著創建線程處理TCP消息,在這個線程中,攝像節點等待終端節點發送的start指令和請求數據指令,如果是start指令,就開始收集數據,如果是請求數據指令,則停止數據收集并發送數據集到終端節點,然后初始化FPGA IP基地址和buffer,并設置幀間差分法的閾值,接著獲取第一幀圖像并記錄時刻t,再獲取下一幀并記錄時刻t,然后diff processor會對兩幀圖像進行處理,讀取處理結果并分離得到原圖像和幀間差分結果圖像,在幀間差分結果圖像中查找最大框,如果有最大框就用紅框框住激光筆輪廓并壓縮圖像發送到終端節點,如果沒有最大框就壓縮原圖像發送到終端節點,最后根據終端節點發送的指令來判斷是否收集數據集。

11

終端節點程序設計

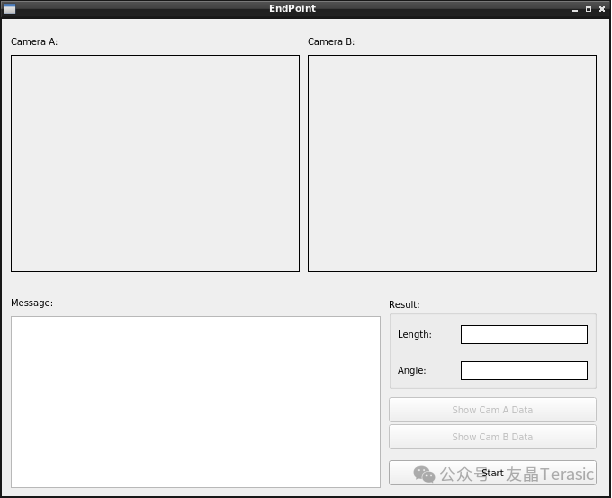

初始化用戶界要有攝像節點A和B的畫面顯示、消息顯示框以及測量結果的顯示:

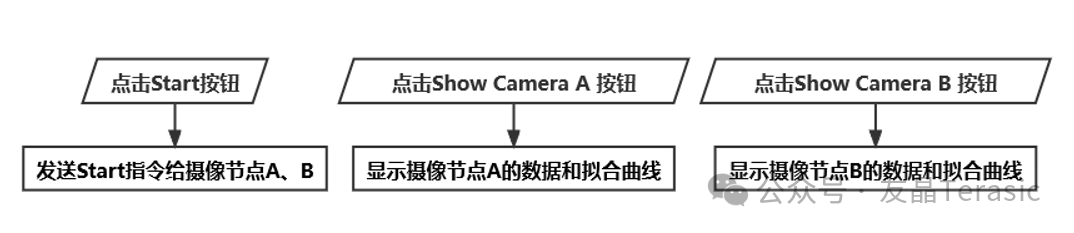

此外還有三個按鈕,Start按鈕用來發送指令給攝像節點A和B,Show Camera A按鈕用來顯示攝像節點A的數據和擬合曲線,Show Camera B按鈕用來顯示攝像節點B的數據和擬合曲線。

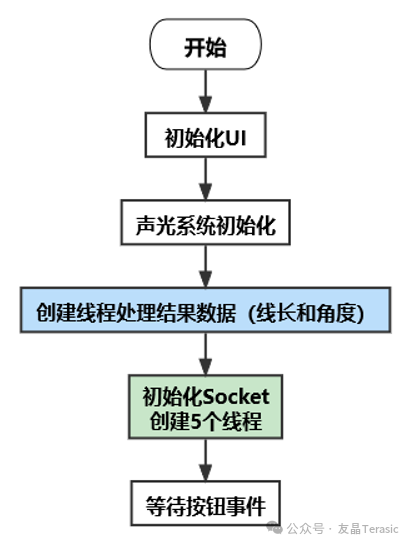

然后是聲光系統初始化,再接著創建一個線程用于處理結果數據,初始化Socke并創建5個線程,最后等待按鈕事件。

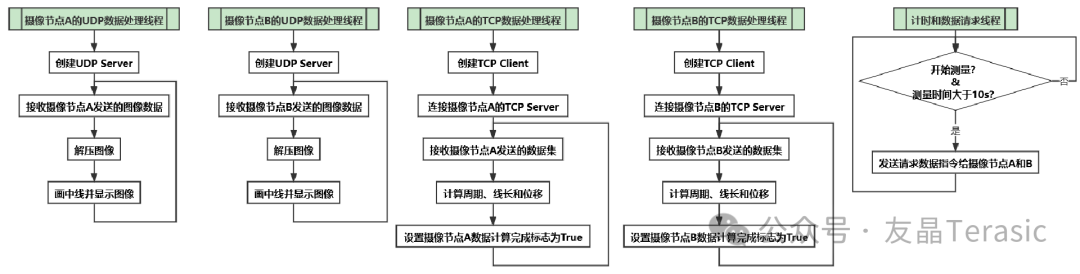

下面我們具體介紹創建的5個線程,分別是攝像節點A、B的UDP數據處理線程和TCP數據處理線程,還有一個計時和數據請求線程。

其中,UDP數據處理線程首先創建UDP Server,然后等待接收攝像節點A、B發送的圖像數據,然后解壓圖像并顯示。

TCP數據處理線程首先創建TCP Client,然后連接攝像節點A、B的TCP Server,之后等待接收攝像節點發送的數據集,計算得到周期、線長和位移,計算完成后設置標志為True。

計時和數據請求線程主要是判斷是否開始測量以及測量時間是否大于10s,如果測量時間達到10s,就發送請求數據指令給攝像節點。

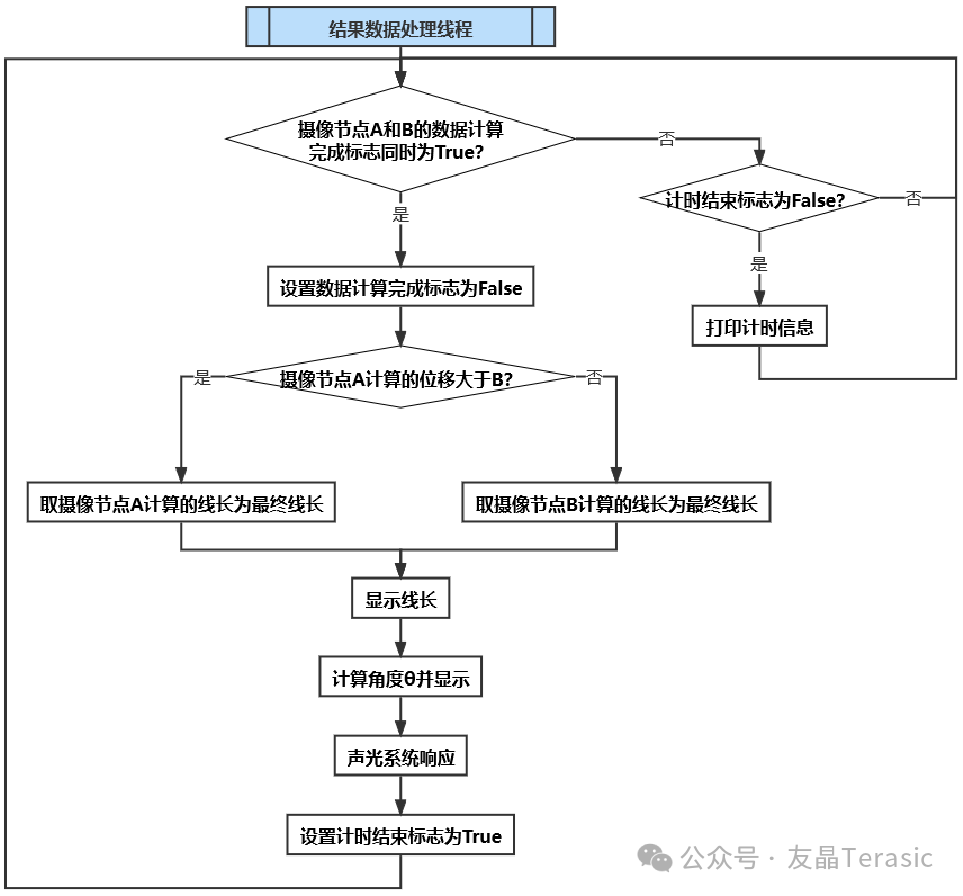

最后是結果數據處理線程,先判斷攝像節點A、B是否計算完成,如果沒有計算完,則先判斷是否還在計時,如果是則打印計時消息并繼續等待攝像節點計算完成。

當攝像節點A和B都計算完成后,首先將標志位清零,然后判斷攝像節點A的位移和B的位移哪一個更大,選擇位移較大的節點計算的線長作為最終線長并顯示,接著計算角度θ并顯示,然后聲光提示,最后停止計時。

12

擬合cos函數程序設計

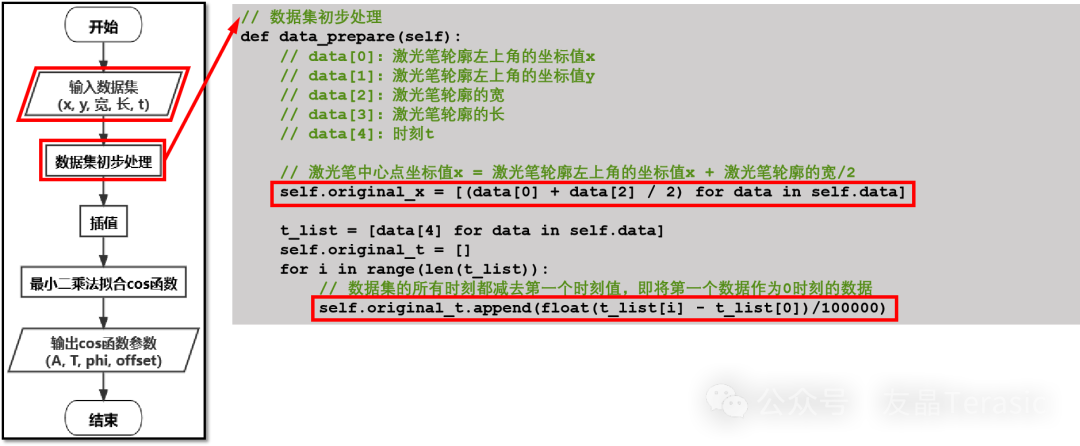

當終端節點收到攝像節點采集到的數據集(包含激光筆輪廓左上角的坐標x和y、輪廓的寬和長以及時刻t)時會對數據集進行初步的處理。

首先是將激光筆左上角的坐標值x+激光筆輪廓的寬/2,得到激光筆中心點的坐標值x。然后再將數據集的所有時刻都減去第一個時刻值,也就是將第一個數據作為0時刻的數據。

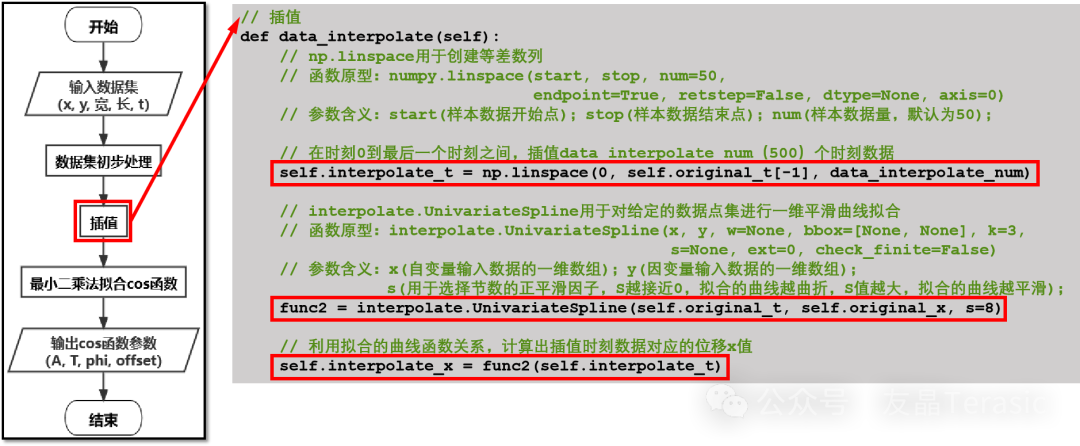

接著通過插值來增加數據量。

先是使用Linear space函數創建時刻t的等差數列,函數的第一個參數為樣本數據開始點,也就是時刻0,第二個參數為樣本數據的結束點,也就是最后一個時刻值,第三個參數為樣本數據量,這里我們插值500個時刻數據。

接下來使用Univariate Spline函數對已有的數據集進行平滑曲線擬合,得到函數關系式function2,然后利用擬合的函數關系,計算出插值時刻對應的位移x。

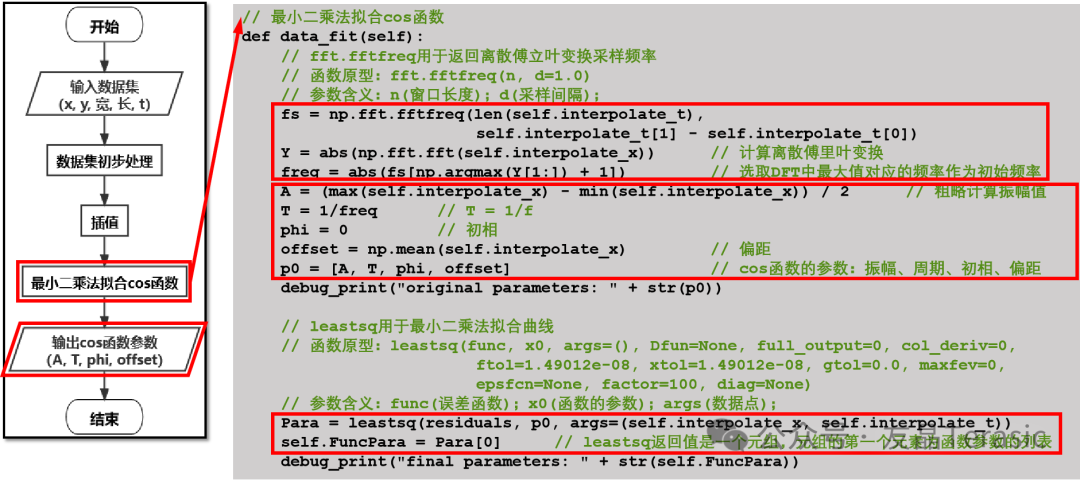

最后使用最小二乘法擬合cos函數。

第一步是使用fft frequency函數得到傅里葉變換的采樣頻率,然后使用fft函數計算離散傅里葉變化。由于離散傅里葉變化在一段有限長的離散信號中,找出它含有的各個頻率的正弦波分量,因此我們可以選取離散傅里葉變化中最大值對應的頻率作為cos函數的初始頻率,

接著用最大位移-最小位移,/2,得到初始振幅值,周期=1/頻率,初相設為0,計算所有位移的平均值作為偏距。

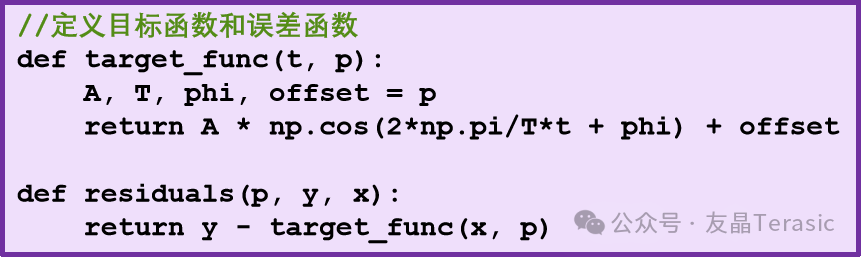

然后使用least square函數擬合cos函數,第一個參數為誤差函數,首先定義目標函數為Acos(2pi/T*t+phi)+偏距,那么誤差函數為:y-目標函數值。第二個參數為函數的參數p0。第三個參數為數據集,least square函數的返回值parameter是一個元組,元組的第一個元素為cos函數的參數列表,最后輸出cos函數的參數。

審核編輯:黃飛

-

HDMI

+關注

關注

32文章

1663瀏覽量

151655 -

電路設計

+關注

關注

6665文章

2427瀏覽量

203306 -

互聯網

+關注

關注

54文章

11105瀏覽量

103012 -

攝像頭

+關注

關注

59文章

4808瀏覽量

95425 -

攝像系統

+關注

關注

0文章

19瀏覽量

12082

原文標題:2021年全國大學生電子設計競賽D題——基于互聯網的攝像測量系統(二)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于互聯網的攝像測量系統(二)

基于互聯網的攝像測量系統(二)

評論