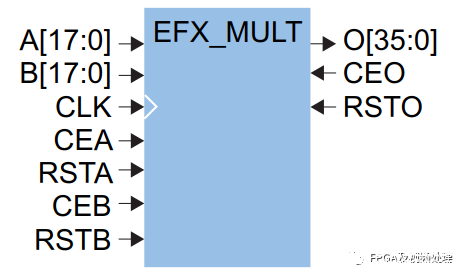

在使用Trion乘法器可能會遇到以下問題:

(1)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CEA' is not permanently disabled in the Register Bypass mode.

說明:如果輸入寄存器A_REG沒有使能,CEA接口要設(shè)置為0

(2)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'RSTA' is not permanently disabled in the Register Bypass mode.

說明:如果輸入寄存器A_REG沒有使能,RSTA接口要設(shè)置為0

(3)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CLK' is not permanently disabled in the Register Bypass mode.

說明:如果輸入和輸出寄存都沒有使用的話,時鐘也要設(shè)置為0。

所以這里提供下面的寫法供參考。

EFX_MULT.WIDTH(18),.A_REG(AREG),.B_REG(BREG),.O_REG(OREG),.CLK_POLARITY(1'b1), // 0 falling edge, 1 rising edge.CEA_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTA_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTA_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTA_VALUE(1'b0), // 0 reset, 1 set.CEB_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTB_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTB_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTB_VALUE(1'b0), // 0 reset, 1 set.CEO_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTO_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTO_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTO_VALUE(1'b0) // 0 reset, 1 set) mult (.CLK((AREG || BREG || OREG) ? clk : 0),.CEA(AREG),.RSTA(AREG ? rst : 1),.CEB(BREG),.RSTB(BREG ? rst : 1),.CEO(OREG),.RSTO(OREG ? rst : 1),.A(A_in),.B(B_in),.O(O_out));

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348281 -

原語使用

+關(guān)注

關(guān)注

0文章

2瀏覽量

1218

發(fā)布評論請先 登錄

相關(guān)推薦

使用AMD Versal AI引擎加速高性能DSP應(yīng)用

DSP平臺與RTB的關(guān)系

DSP功放HOSt和acc區(qū)別

雙核dsp和單核dsp的區(qū)別

雙DSP音效處理芯片有什么作用

DSP是什么意思

Efinity編譯生成文件使用指導(dǎo)

國產(chǎn)集成DSP內(nèi)核無線音頻傳輸?shù)臒o線接收芯片U1R32D

加法進(jìn)位鏈的手動約束

Versal FPGA中的浮點計算單元DSPFP32介紹

dsp是什么意思 dsp功放對音質(zhì)到底有沒有提升

dsp芯片和arm芯片區(qū)別 dsp的應(yīng)用領(lǐng)域

dsp是什么意思 dsp怎么調(diào)音質(zhì)最好

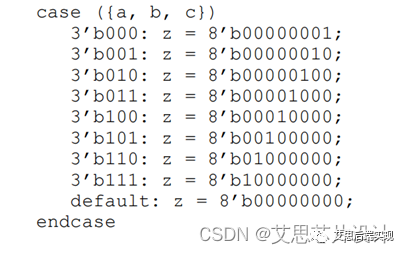

如何用RTL原語實現(xiàn)MUX門級映射呢?

Trion DSP 原語使用問題 - 1

Trion DSP 原語使用問題 - 1

評論