SOC(System on Chip,片上系統(tǒng))設(shè)計中,時鐘信號的控制對于整個系統(tǒng)的性能和功耗至關(guān)重要。本文將帶您了解SOC設(shè)計中的一種時鐘控制技術(shù)——Clock Gating,通過Verilog代碼實例的講解,讓您對其有更深入的認(rèn)識。

一、Clock Gating基本原理

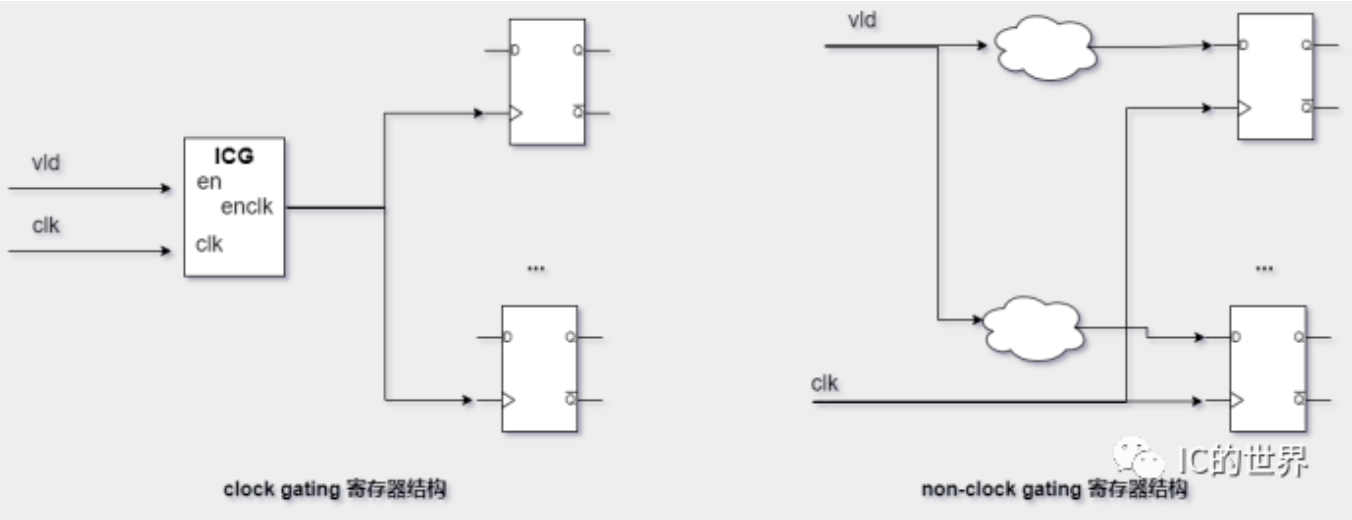

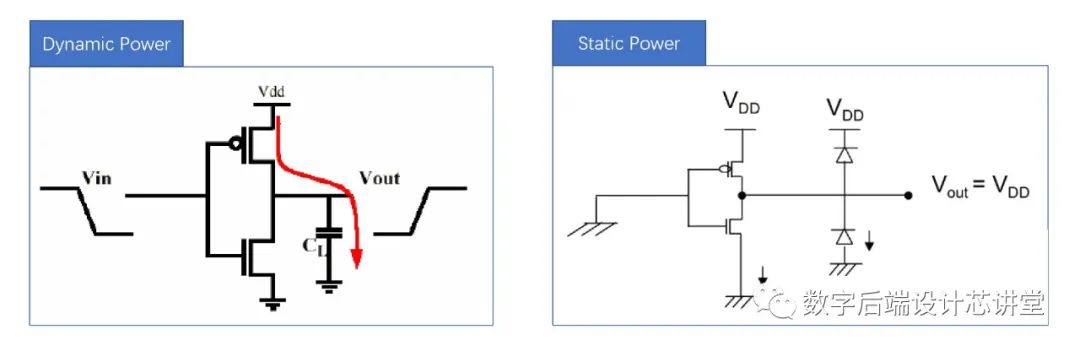

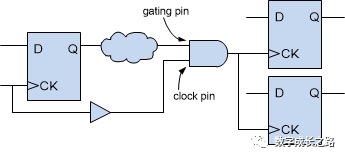

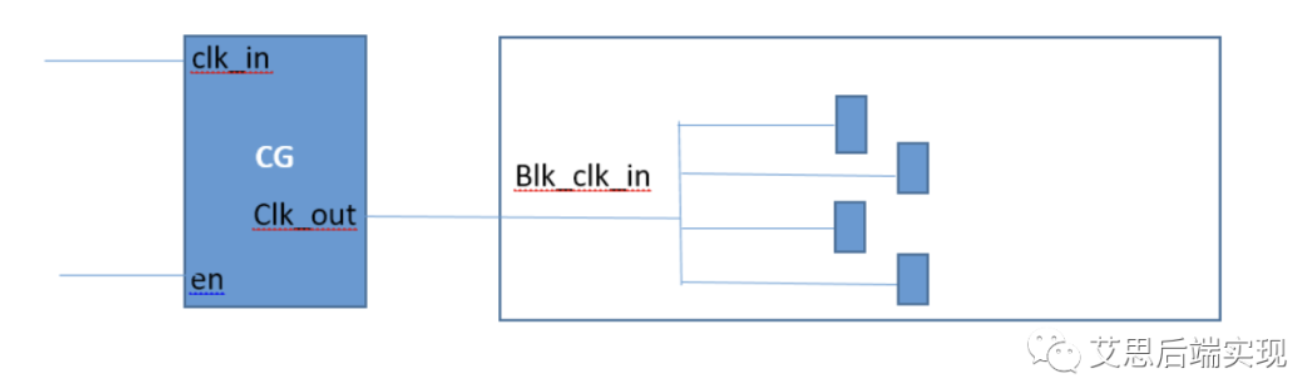

Clock Gating,即時鐘門控,是一種在數(shù)字集成電路設(shè)計中常用的低功耗技術(shù)。它的基本思想是,在時鐘信號傳輸?shù)?a href="http://www.nxhydt.com/tags/寄存器/" target="_blank">寄存器之前,通過控制邏輯來決定時鐘信號是否需要傳遞給寄存器。如果某個寄存器在當(dāng)前時鐘周期內(nèi)不需要進行操作,那么就可以通過Clock Gating技術(shù)關(guān)閉該寄存器對應(yīng)的時鐘信號,從而減少不必要的功耗。

二、Verilog實現(xiàn)Clock Gating

接下來,我們將通過一個簡單的Verilog代碼實例來講解Clock Gating的實現(xiàn)。

假設(shè)我們有一個簡單的2-to-1多路復(fù)用器(MUX),它有一個選擇信號(SEL)、兩個數(shù)據(jù)輸入(A和B)和一個輸出(Y)。我們希望在SEL無效時關(guān)閉多路復(fù)用器的時鐘,以節(jié)省功耗。

以下是一個簡單的Verilog代碼示例:

module clock_gating_example(

input wire clk,

input wire rst_n,

input wire sel,

input wire a,

input wire b,

output reg y

);

wire gated_clk;

// Clock Gating Cell

assign gated_clk = clk & ~sel;

// 2-to-1 MUX

always @(posedge gated_clk or negedge rst_n) begin

if (!rst_n) begin

y <= 1'b0;

end else begin

y <= sel ? b : a;

end

end

endmodule

在這個例子中,我們使用了一個簡單的Clock Gating單元,它由一個AND門和一個反相器組成。當(dāng)選擇信號(SEL)無效時,經(jīng)過Clock Gating單元處理后的時鐘信號(gated_clk)將關(guān)閉,從而停止多路復(fù)用器的時鐘。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5325瀏覽量

120052 -

SoC設(shè)計

+關(guān)注

關(guān)注

1文章

148瀏覽量

18764 -

片上系統(tǒng)

+關(guān)注

關(guān)注

0文章

185瀏覽量

26779 -

多路復(fù)用器

+關(guān)注

關(guān)注

9文章

871瀏覽量

65289 -

時鐘信號

+關(guān)注

關(guān)注

4文章

445瀏覽量

28512

原文標(biāo)題:Verilog實戰(zhàn)解析:SOC設(shè)計中Clock Gating的基本原理與應(yīng)用

文章出處:【微信號:快樂的芯片工程師,微信公眾號:快樂的芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

clock-gating的綜合實現(xiàn)

數(shù)電中的TTL電路的基本原理

雙脈沖測試基本原理及意義

串口通信基本原理是什么

線性電源的基本原理是什么

STM32基本原理簡介

ASIC的clock gating在FPGA里面實現(xiàn)是什么結(jié)果呢?

SOC設(shè)計中Clock Gating的基本原理與應(yīng)用講解

SOC設(shè)計中Clock Gating的基本原理與應(yīng)用講解

評論