近日,南方科技大學深港微電子學院潘權教授領銜的科研團隊在高速有線芯片設計領域取得顯著突破。相關成果在集成電路設計領域權威學術期刊《固態電路期刊》(IEEE Journal of Solid-State Circuits, JSSC)上發表,題目為“A 2×56 Gb/s 0.78-pJ/b PAM-4 Crosstalk Cancellation Receiver With Active Crosstalk Extraction Technique in 28-nm CMOS”。

隨著云計算與人工智能的發展,數據中心處理和交換海量數據集的需求日益增加,對帶寬的需求也隨之提升。然而,傳統有線收發器受限于面積和功耗,無法滿足高速數據傳輸的需求。

此前已有研究嘗試在先進CMOS技術中實現224 Gb/s四電平脈沖幅度調制(PAM-4)基于數字信號處理器(DSP)的發射器和接收器,但在31 dB奈奎斯特損耗的信道環境下,功耗高達820 mW/lane,嚴重制約了其在長距離、高數據速率場景中的應用。

為了解決上述問題,IEEE 802.3 Beyond 400 Gb/s以太網研究小組提出了單端多輸入多輸出(MIMO)方案。如圖1所示,該方案通過在一個差分或類差分通道上傳輸兩個單端信號,有效提升了I/O效率和數據吞吐量。本研究在此基礎上提出了一種單端MIMO PAM-4串擾消除和信號再利用(XTCR)中距(MR)背板RX,成功實現了2×56 Gb/s的數據傳輸。

論文第一作者為2020級博士生鐘立平,通訊作者為潘權教授,南方科技大學深港微電子學院為唯一單位,研究工作獲得了國家自然科學基金和國家重點研發計劃經費的資助。

-

芯片設計

+關注

關注

15文章

1005瀏覽量

54819 -

數據中心

+關注

關注

16文章

4700瀏覽量

71970 -

人工智能

+關注

關注

1791文章

46896瀏覽量

237666

發布評論請先 登錄

相關推薦

NVIDIA CEO黃仁勛對話香港科技大學畢業生

哈爾濱工業大學/南方科技大學:聚焦離子束制備高分辨率電化學-電致發光耦合雙極納米電極陣列傳感器

喜報|Amass連接器助力電子科技大學機器人隊榮耀奪冠

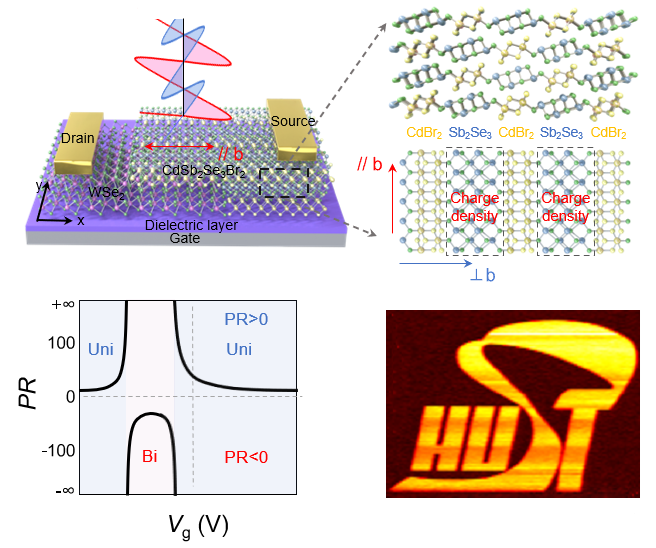

華中科技大學在偏振光電探測器領域獲新進展

【科研新助力】南方科技大學采購南京大展的導熱系數測定儀

西安電子科技大學馬曉華團隊:蹚出寬禁帶半導體技術創新之路

NVIDIA DPU編程入門開課儀式在澳門科技大學成功舉辦

中國科學技術大學科研團隊取得量子計算研究新進展

電子科大團隊在非平衡態統計物理研究領域取得顯著突破

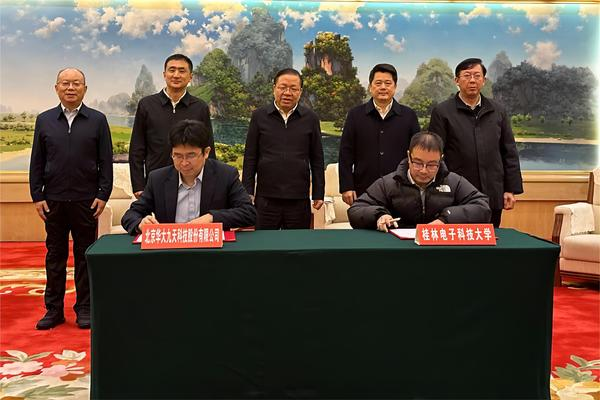

華大九天與桂林電子科技大學簽署校企合作框架協議

南方科技大學潘權團隊在JSSC發表高速有線芯片設計領域重要進展

南方科技大學潘權團隊在JSSC發表高速有線芯片設計領域重要進展

評論