引言

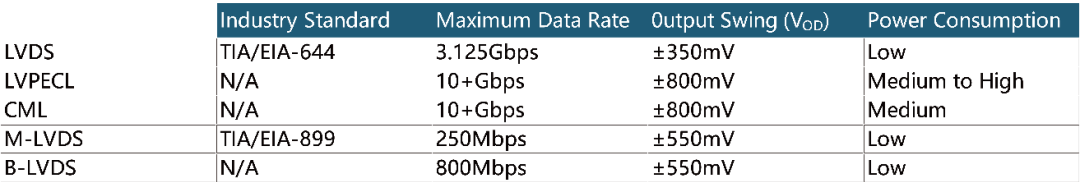

信號鏈是連接真實世界和數字世界的橋梁。隨著ADC采樣率和采樣精度的提升,接口芯片的信號傳輸速度也越來越快,高速信號傳輸的各種挑戰慢慢浮現出來了。相比傳統的CMOS傳輸技術,在信號鏈中引入LVDS或JESD204B,可以實現更高的信號傳輸速率,更低的功耗,具備更好的抗干擾性 (信噪比更佳),而且線束數量會大幅降低。

什么是LVDS和JES204B?

LVDS(Low-Voltage Differential Signaling ,低電壓差分信號)是美國國家半導體(National Semiconductor, NS,現TI)于1994年提出的一種信號傳輸模式的電平標準,它采用極低的電壓擺幅傳輸高速差分數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾等優點,已經被廣泛應用于串行高速數據通訊的各個場合,比較廣為人知的有筆記本電腦的液晶顯示,數據轉換器(ADC/DAC)的高速數字信號傳輸,汽車電子的視頻碼流傳輸等。

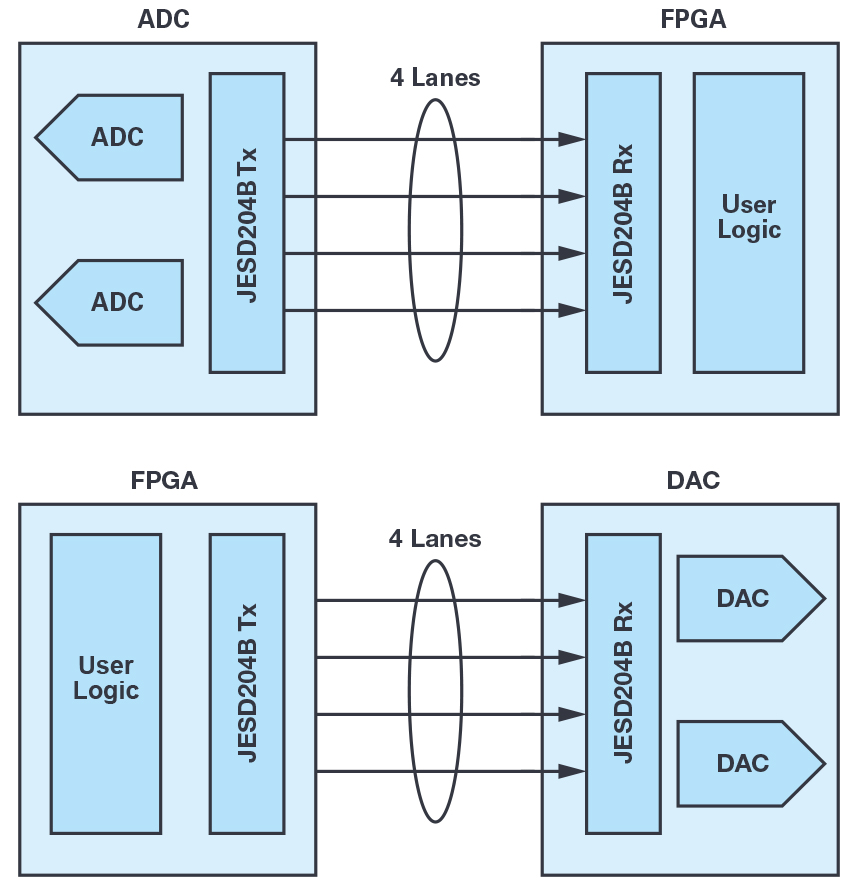

JESD204是標準化組織JEDEC,針對數據轉換器(ADC和DAC)和邏輯器件(FGPA)之間進行數據傳輸,而制定的高速串行接口。JESD204采用CML (Current-Mode Logic)技術來傳輸信號,該標準的 B 修訂版支持高達 12.5 Gbps串行數據速率,并可確保 JESD204 鏈路具有可重復的確定性延遲。隨著轉換器的速度和分辨率不斷提升,以及FPGA芯片對JESD204B標準的廣泛支持,JESD204在高速轉換器和集成RF收發器的應用中也變得更為常見。

高速信號傳輸的實際應用

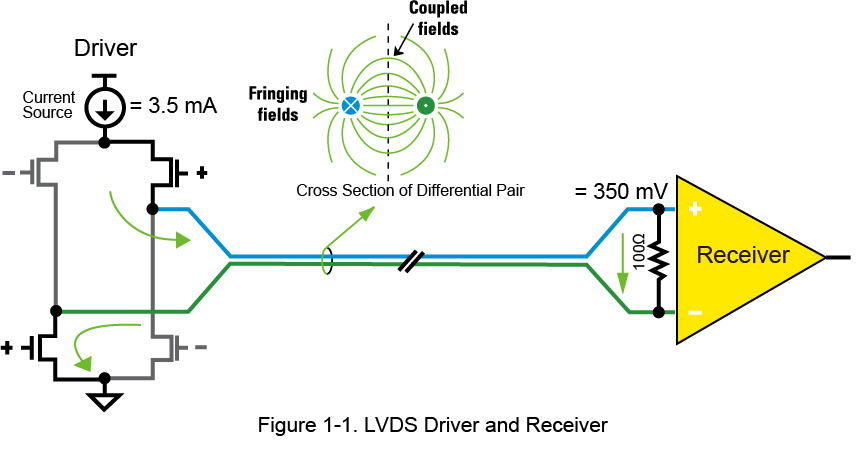

LVDS是一種電流驅動的高速信號,在發送端施加一個3.5mA的恒定電流源。控制開關管的通斷,就可以使得發送端流向接收端的電流,在正向和反向之間不斷變化,從而在接收端的100歐姆差分負載上實現+/-350mV的差分電壓變化,最高可實現3.125Gbps的高速數據傳輸。LVDS采用差分線的傳輸方式,會帶來幾個顯著的優勢:

●a. 允許發送端和接收端之間存在共模電壓差異(0-2.4V范圍內)

●b. 優秀的抗干擾能力,信噪比極佳

●c. 極低的電壓擺幅,功耗極低

圖2. LVDS的工作方式

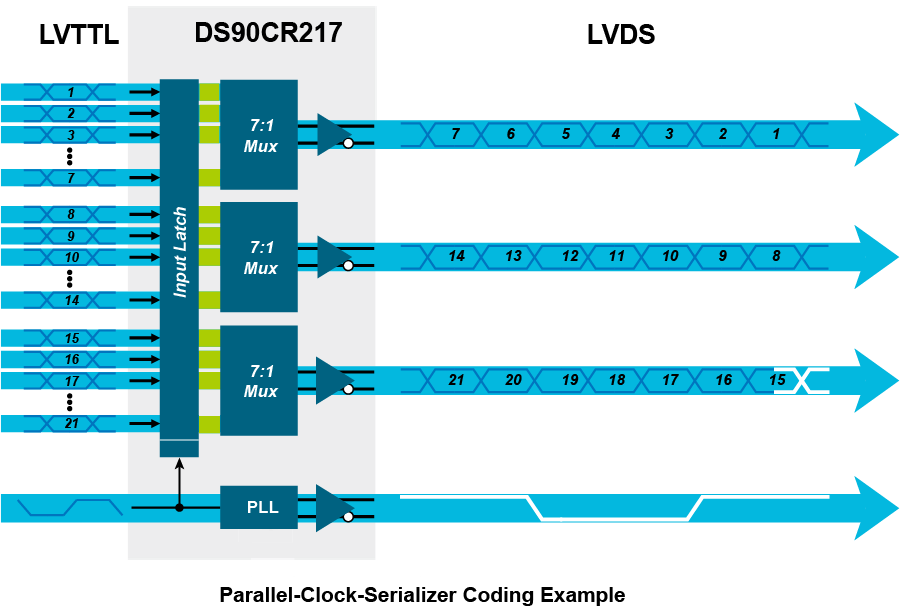

傳統的LVDS采用同步時鐘的方式,使用一對差分時鐘,為最多三對數據信號提供時鐘參考。每個時鐘周期內,每對數據傳輸7 bits信息。需要用到SerDes芯片,在發送時,將并行信號通過并/串轉換,變成高速串行信號;在接收到高速串行信號時,使用串/并轉換,還原并行信號。

圖3. LVDS 同步時鐘為數據提供參考

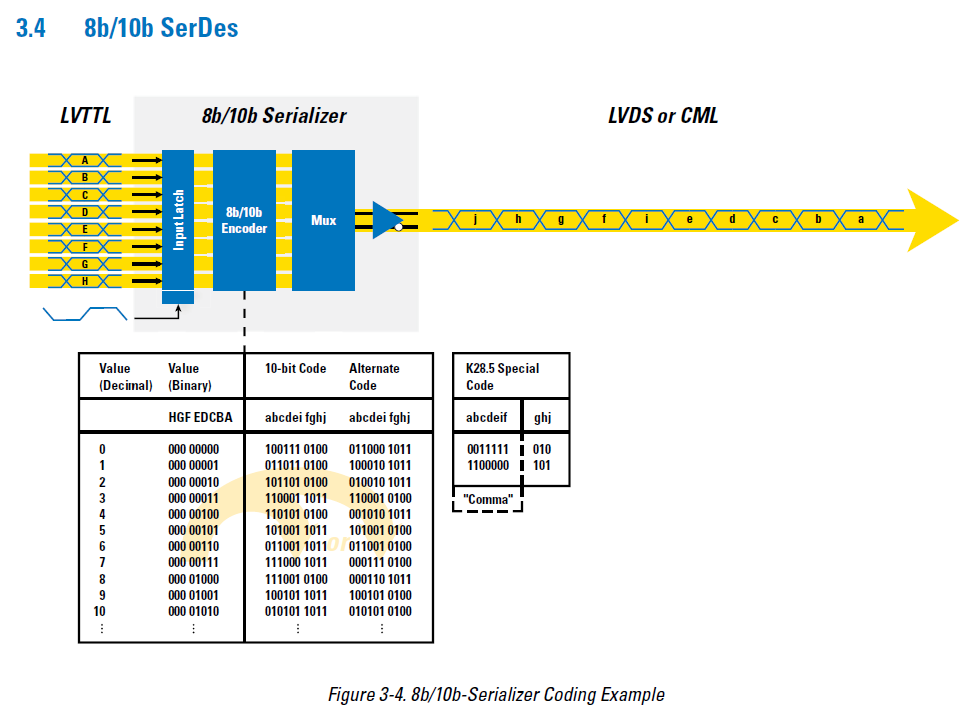

現在使用的LVDS也支持8b/10b SerDes來實現更高效的信號傳輸。這種傳輸方式不再需要用到時鐘信號,只需要傳輸Data信號就可以了,節省了一對差分線。通過8b/10b編碼,將8bit有效數據映射成10bit編碼數據,這個過程中雖然增加了25%的開銷,但可以確保數據里有足夠頻繁的信號跳變。

在收到信號后,通過鎖相環(PLL)從數據里恢復出時鐘。這種傳輸架構稱之為嵌入式時鐘(Embeded Clock)。8b/10b編碼還可以讓傳輸信號實現直流平衡(DC Balance),即1的個數和0的個數基本維持相等。直流平衡的傳輸鏈路可以串聯隔直電容,提升鏈路的噪聲和抖動性能。嵌入式時鐘和8b/10b被廣泛用于工業高速傳輸標準,比如PCIe,SATA, USB3等,也包括JESD204 (CML)。

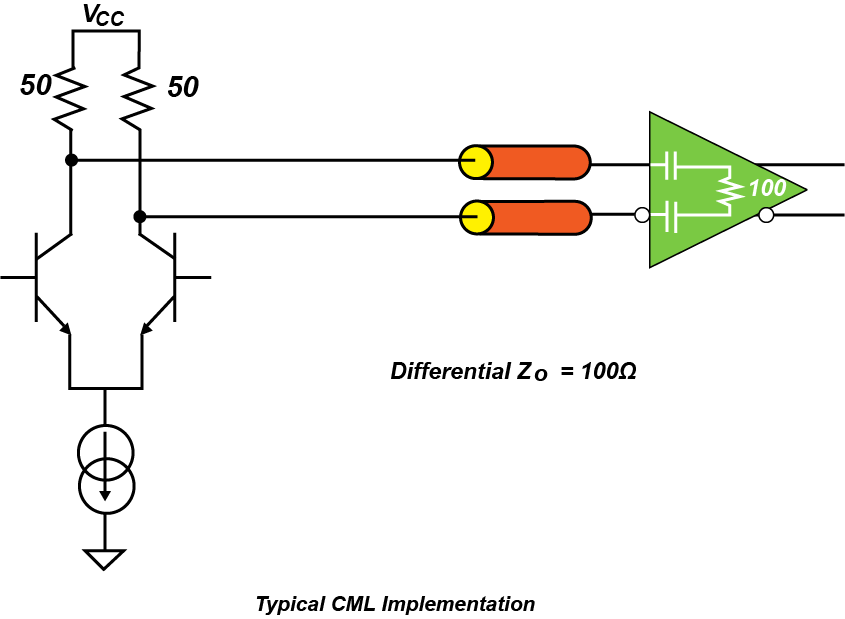

圖4. LVDS內嵌時鐘的工作方式(圖片來源TI)

不同于LVDS的是, CML(Current-Mode Logic)采用電壓驅動的方式,在源端施加一個恒定的電壓Vcc。通過控制開關管的通斷,接收端就可以得到變化的差分電壓。CML使用嵌入式時鐘和8b/10b編碼,工作電壓比LVDS更高,同時在發送和接收芯片里使用均衡技術,以確保高速、長距離傳輸時仍具有很優秀的誤碼率。使用CML技術的JESD204B可支持高達12.5Gbps的data rate,其最新的C版本甚至可以支持高達32Gbps data rate。

圖5. CML信號傳輸方式

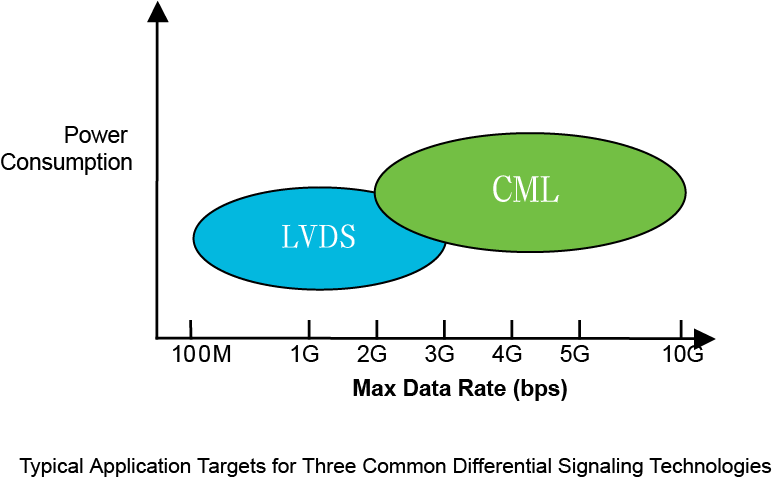

那么我們在設計高速接口芯片時,到底應該使用LVDS還是CML(JESD204)呢?簡單的原則是,CML速率更高,而LVDS則功耗更低。

圖6. LVDS和CML的選擇

當Data Rate低于2Gbps時,LVDS的應用更為廣泛,其功耗更低,抗干擾強,較寬的共模電壓范圍讓互連的要求變得很低。LVDS還有支持多點互連的M-LVDS和B-LVDS標準,可以多節點互連,應用場景非常豐富。當Data rate高于3.125Gbps就必須要使用CML了。當Data Rate在2G到3.125Gbps之間時,要綜合考慮功能性,性能,和功耗的平衡。比如說傳輸距離較長,但信號品質要求又很高的時候,考慮用CML;傳輸距離較短,要求長續航,低功耗的時候,考慮用LVDS。

審核編輯:劉清

-

信噪比

+關注

關注

3文章

253瀏覽量

28591 -

lvds

+關注

關注

2文章

1036瀏覽量

65699 -

數據轉換器

+關注

關注

1文章

357瀏覽量

27982 -

ADC采樣

+關注

關注

0文章

134瀏覽量

12831 -

差分電壓

+關注

關注

0文章

15瀏覽量

9550

原文標題:【做信號鏈,你需要了解的高速信號知識(一)】為什么要使用LVDS或JESD204B標準?

文章出處:【微信號:泰克科技,微信公眾號:泰克科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JESD204B的系統級優勢

串行LVDS和JESD204B的對比

JESD204B串行接口時鐘的優勢

JESD204B協議有什么特點?

寬帶數據轉換器應用的JESD204B與串行LVDS接口考量

JESD204B協議介紹

JESD204B的優勢

JESD204B協議概述

JESD204B標準及演進歷程

JESD204B標準的ADC與FPGA的接口

JESD204B學習手冊

JESD204B是FPGA中的新流行語嗎

什么是LVDS和JES204B?為什么要使用LVDS或JESD204B標準?

什么是LVDS和JES204B?為什么要使用LVDS或JESD204B標準?

評論