高性能處理器 (例如最新的 FPGA) 對(duì)電源電壓有非常嚴(yán)格的要求,很多人可能很難找到一款能夠滿足 FPGA 電壓精度要求的大電流 LDO。本文將介紹 ADI 大電流 LDO 產(chǎn)品陣容,其中包括業(yè)界領(lǐng)先的能夠輸出 5A 電流的大電流 LDO,它被用于最新高性能處理器的電源設(shè)計(jì)中。

如何滿足高性能處理器的電源要求?

近年來(lái),F(xiàn)PGA、ASIC、DSP 等高性能處理器實(shí)現(xiàn)了工藝小型化,其處理能力得到了顯著提高。因此對(duì)電源電壓的要求越來(lái)越低,并且需要極高的精度,例如電壓精度不超過(guò) ±1%。另一方面,隨著功耗不斷增加,預(yù)計(jì)未來(lái)需要高精度低電壓和大電流的場(chǎng)所數(shù)量將會(huì)增加。

接下來(lái)介紹滿足高性能處理器的電源要求的方法。其中之一是使用低壓差 (LDO) 穩(wěn)壓器:通過(guò)在 DC/DC 轉(zhuǎn)換器和高性能處理器之間放置一個(gè) LDO,可以相對(duì)容易地以低成本實(shí)現(xiàn)電壓穩(wěn)定和高精度。但是普通 LDO 的輸出電流有限,它通常不適合需要大電流的高性能處理器。事實(shí)上,ADI 還提供了用于為高性能處理器供電的大電流 LDO,它是穩(wěn)定 DC/DC 轉(zhuǎn)換器通過(guò)的電壓的理想選擇,其特點(diǎn)如下:

輸出電壓精度高

節(jié)省空間,成本低

電壓轉(zhuǎn)換能力強(qiáng),壓差低

即使在 LDO 因電流不足而放棄的情況下,也可以積極使用它們。此外,如果是用于為高性能處理器供電的 LDO,則在許多情況下可能需要以下功能:

使能功能

抑制發(fā)熱功能

快速瞬態(tài)響應(yīng)

輸出電壓精度高

ADI 大電流 LDO 產(chǎn)品陣容

產(chǎn)品陣容 (1) LT3070/LT3071:具有超低壓差和快速瞬態(tài)響應(yīng)的 5A 輸出 LDO

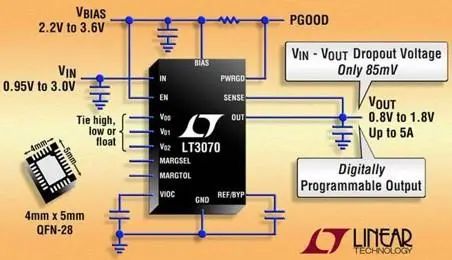

下圖 (圖1) 為 LT3070/LT3071 的典型應(yīng)用圖,它的輸出電流高達(dá) 5A,是業(yè)界最高輸出電流產(chǎn)品之一。它是一款具有超低壓降和快速瞬態(tài)響應(yīng)的 LDO。

圖1 LT3070/LT3071 典型應(yīng)用圖

輸出適配最新處理器

輸出電流:5A

輸出電壓:0.8V~1.8V

以 50mV 為增量進(jìn)行數(shù)字配置

可進(jìn)行多路并聯(lián) (10A 或更大電流輸出)

抑制發(fā)熱

超低壓差:85mV

內(nèi)置輸入電壓跟蹤功能 (VOIC)

通過(guò)控制前端電源,可將損耗降至最低

快速瞬態(tài)響應(yīng)

最小化輸出電容 (最小值:15μF)

針對(duì)處理器啟動(dòng)/宕機(jī)的優(yōu)化功能

熱關(guān)斷

使能功能

電源正常

UVLO 系列

反向電流保護(hù)

LT3071 具有模擬輸出裕度調(diào)節(jié)功能:±10% 范圍,輸出電壓可以連續(xù)調(diào)節(jié)。

產(chǎn)品陣容 (2) LT3072:雙通道,每個(gè) 2.5A 輸出可用,快速瞬態(tài)響應(yīng) LDO

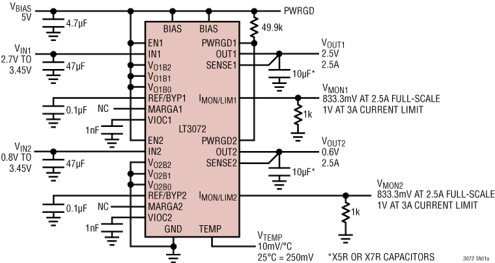

LT3072 是一款雙通道 LDO,每個(gè)通道的輸出電流為 2.5A。下圖 (圖2) 為 LT3072 典型應(yīng)用圖:

圖2 LT3072 典型應(yīng)用圖

輸出適配最新處理器

輸出電流:2.5A

輸出電壓:0.6V~2.5V

以 50mV 為增量進(jìn)行數(shù)字配置

輸出精度可滿足最新處理器的需求

低輸出噪聲:12μVrms (10Hz~100Hz)

快速瞬態(tài)響應(yīng)

輸出電容最小 (低至 10μF)

優(yōu)化的處理器啟動(dòng)/宕機(jī)功能

熱關(guān)斷

使能功能

UVLO 系列

電源正常標(biāo)志

反向電流保護(hù)

產(chǎn)品陣容 (3) LT3073:具有超高 PSRR 和快速瞬態(tài)響應(yīng)的 3A 輸出 LDO

下圖 (圖3) 為 LT3073 產(chǎn)品圖,它是具有極高 PSRR 的 LDO。

圖3 LT3073 產(chǎn)品圖

最大限度提高高速轉(zhuǎn)換器和 RFIC 的性能

超低 RMS 噪聲:1.2μVRMS (10Hz~100kHz)

超低 1/f 噪聲:7μVP-P (0.1Hz~10Hz)

超低點(diǎn)噪聲:3 nV/√Hz (10kHz)

高頻 PSRR:52dB (1MHz)

壓差:45mV

輸入電壓范圍:0.6V~5.5V

輸出電壓范圍:0.5V~4.2V (數(shù)字設(shè)定)

輸出電流:3A

可編程電流限制

電流監(jiān)控功能

針對(duì)處理器啟動(dòng)/宕機(jī)的優(yōu)化功能

熱關(guān)斷

啟用功能

電源正常

UVLO 系列

溫度監(jiān)控功能

LT307x 系列產(chǎn)品對(duì)比

接下來(lái)對(duì) LT307x 系列產(chǎn)品特性進(jìn)行對(duì)比,如下表 (表1) 所示,值得注意的是輸出電流和壓差。

| LT3073 | LT3070-1/LT3071 | LT3072 | |

| 輸出電流和壓差 | 3A,45mV | 5A,85mV | 2.5A (2ch),80mV |

| 輸出電壓裕度調(diào)節(jié) | 數(shù)字 |

LT3070-1:數(shù)字 LT3071:模擬 |

模擬 |

| PSRR | 52dB (1MHz 時(shí)) | 36dB (100kHz 時(shí)) | 43dB (100kHz 時(shí)) |

| RMS噪聲 | 1.2μV (10Hz-100kHz) | 25μV (10Hz-100kHz) | 12μV (10Hz-100kHz) |

|

VIOC 功能 用于控制前一級(jí)的 DC/DC |

Yes | Yes | Yes |

表1 LT307x 系列產(chǎn)品對(duì)比表

LDO 壓差的重要性

壓差是輸入電壓與從 LDO 獲得預(yù)期輸出電壓所需的輸出電壓之間的最小差值。例如,如果 LDO 的壓差為 200mV (0.2V),則需要 5.2V 或更高的輸入電壓才能輸出 5V 電壓。LDO 產(chǎn)生的熱量由輸入和輸出之間的電壓差×輸出電流決定。輸入輸出電壓差越大,產(chǎn)生的熱量就越多,因此設(shè)計(jì)要點(diǎn)之一是使電壓差盡可能小。但是差值能縮小多少取決于 LDO 壓差規(guī)格:LDO 的壓差越大,選擇范圍越小。

此外,輸出電流的大小也會(huì)影響發(fā)熱量。即使電壓差條件相同,如果輸出電流為 5 倍,發(fā)熱也將為 5 倍。因此,對(duì)于大電流 LDO 而言,降低輸入輸出電壓差更為重要。典型 LDO 的壓差約為 200mV~500mV,而 LT307x 系列的壓差電壓非常低,為 45mV~85mV。由于輸入輸出之間的電壓差可以大大降低,因此即使在大電流下也可以解決 LDO 的發(fā)熱問(wèn)題。

產(chǎn)品陣容 (4) LTM4709:3 通道,每個(gè)通道 3A 電流的模塊型 LDO

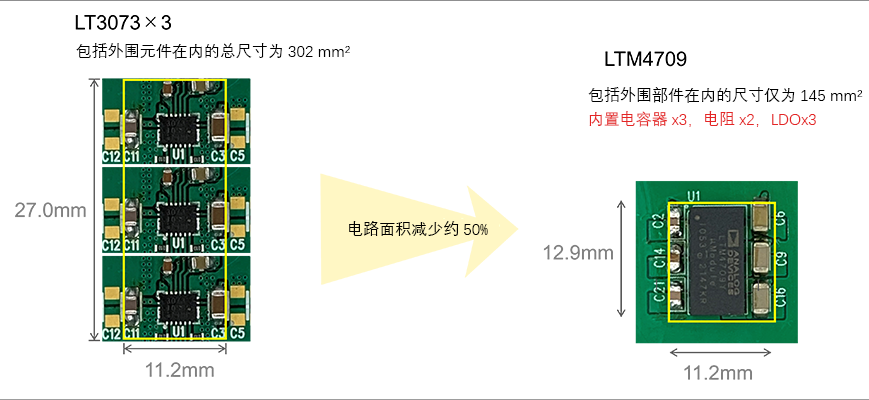

下圖 (圖4) 為 LTM4709 產(chǎn)品圖,它是一款模塊型大電流 LDO,該產(chǎn)品具有與 LT3073 相同的性能,輸出電流為 3A,壓差為 45mV,可在單個(gè)芯片上實(shí)現(xiàn)三個(gè)輸出通道。此外,還內(nèi)置了所有必要的外圍元件。

圖4 LTM4709 產(chǎn)品圖

LDO 所需的內(nèi)置外圍元件

電容器 ×3

電阻 ×2

性能與 LT3073 相同,每個(gè)通道的 3A 輸出

輸入電圧范囲:0.6V~5.5V

輸出電壓范圍:0.5V 至 4.2V (可編程設(shè)置)

低 RMS 噪聲:1.3μVRMS (10Hz~100kHz)

低點(diǎn)噪聲:3 nV/√Hz (10kHz)

高頻 PSRR:51dB (1MHz)

壓差:45mV

快速瞬態(tài)響應(yīng)

每個(gè)保護(hù)功能都遵循 LT3073

接下來(lái)對(duì)使用單通道 LT3073 和模塊化 LTM4709 來(lái)實(shí)現(xiàn)等效電路的情況進(jìn)行比較。下圖 (圖5) 為 3A×3ch 輸出時(shí)的總尺寸比較,在使用三個(gè) LT3073 的電路配置中,包括外圍元件在內(nèi)的總尺寸為 302mm2。另一方面,包括外圍部件在內(nèi)的 LTM4709 的尺寸僅為 145mm2。通過(guò)選擇 LTM4709,可將電路的面積減小約 50%。

圖5 3A×3ch 輸出時(shí)的總尺寸比較

LTM4709 的優(yōu)勢(shì)不僅限于節(jié)省空間,還體現(xiàn)在單個(gè)電源中覆蓋高性能處理器所需的多個(gè)電源,有助于節(jié)省設(shè)計(jì)成本、減少組件數(shù)量和降低電路板成本等方面。ADI 大電流 LDO 獨(dú)特的 5A 輸出和模塊類型陣容有助于為最新的高性能處理器進(jìn)行電源設(shè)計(jì),并且所有列出的產(chǎn)品均提供評(píng)估板。

應(yīng)用實(shí)例

高性能處理器

FPGA

ASIC

DS

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19159瀏覽量

229112 -

輸出電壓

+關(guān)注

關(guān)注

2文章

1092瀏覽量

38014 -

電源電壓

+關(guān)注

關(guān)注

2文章

983瀏覽量

23942 -

PSRR

+關(guān)注

關(guān)注

0文章

153瀏覽量

39297 -

dcdc轉(zhuǎn)換器

+關(guān)注

關(guān)注

8文章

211瀏覽量

38988

原文標(biāo)題:高性能處理器中的 ADI 大電流 LDO

文章出處:【微信號(hào):駿龍電子,微信公眾號(hào):駿龍電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

多內(nèi)核處理器應(yīng)用趨勢(shì)下的高性能視頻系統(tǒng)設(shè)計(jì)

基于高性能LDO線性穩(wěn)壓器的設(shè)計(jì)

基于高性能LDO線性穩(wěn)壓器的設(shè)計(jì)

適用于高性能運(yùn)算的處理器

伺服控制解決方案,滿足你的電機(jī)控制方案需求

ADI SHARC處理器有哪些應(yīng)用案例

為了滿足FPGA的電源要求

滿足最新的性能要求

為了滿足FPGA的電源要求

驅(qū)動(dòng)高性能ASIC和微處理器

ADI新款SHARC處理器性能提高33%

處理器核心電壓要求的電源管理

DN216-多相表面貼裝電源滿足AMD Athlon處理器要求,無(wú)散熱器

ADI大電流LDO產(chǎn)品陣容:滿足高性能處理器的電源要求

ADI大電流LDO產(chǎn)品陣容:滿足高性能處理器的電源要求

評(píng)論