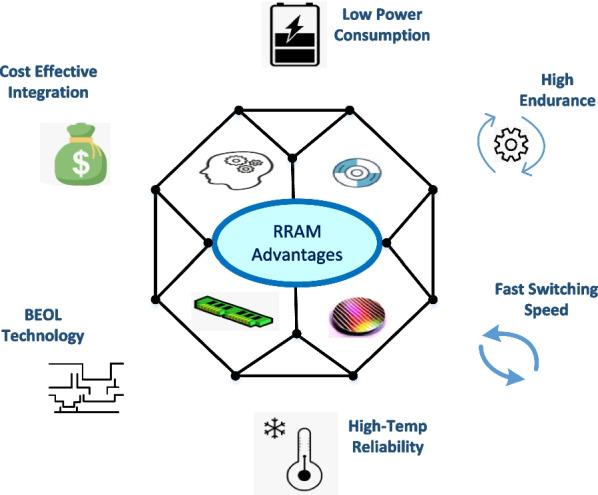

近年來,RRAM 因其結構簡單、保持時間長、運行速度快、超低功耗運行能力、能夠在不影響器件性能的情況下擴展到更低的尺寸以及可進行三維集成的可能性而日益受到重視。過去幾年的研究表明,RRAM 是后 CMOS 時代設計高效、智能和安全計算系統的最合適候選者之一。

半導體電子學領域在過去十年中迅速增長,對人類社會產生重大影響。這歸因于信息通信技術領域的空前增長,以及工程技術領域的各個領域對高效信息處理系統需求的增加。信息技術系統的快速發展徹底改變了智能手機、微型計算機和物聯網(IoT)設備等產品,這些產品需要高性能計算技術。現代產品由電氣和機械組件組成,成為了將硬件、數據存儲、傳感器、軟件、微處理器和多種連接方式多種方式組合在一起的復雜系統。傳統計算系統利用馮·諾依曼體系結構執行計算任務,但由于CPU和內存之間的差距不斷增大,物理上分離的內存和計算單元產生了大量延遲和高能耗,即“馮·諾依曼瓶頸”。自20世紀60年代以來,通過縮小電子器件尺寸和降低集成電路(ICs)的制造成本來增強設備的計算能力。然而,馮·諾依曼體系結構的固有缺陷限制了計算能力的提升。因此,研究人員將注意力轉向了阻性隨機存取存儲器(RRAM)等新型數據處理技術,以解決內存不足的問題。RRAM被視為現有CMOS設備的有希望的替代品,具有諸多優勢,如可擴展性、高數據保留性、低功耗和相對較高的速度。RRAM采用電阻切換存儲器技術,可實現多位信息存儲,并通過控制絲形體的形成和切換來提高均勻性和穩定性。由于其現代化的需求,RRAM技術正朝著全面商業化邁進,其在未來幾年內的發展前景廣闊。

阻變存儲器的優點

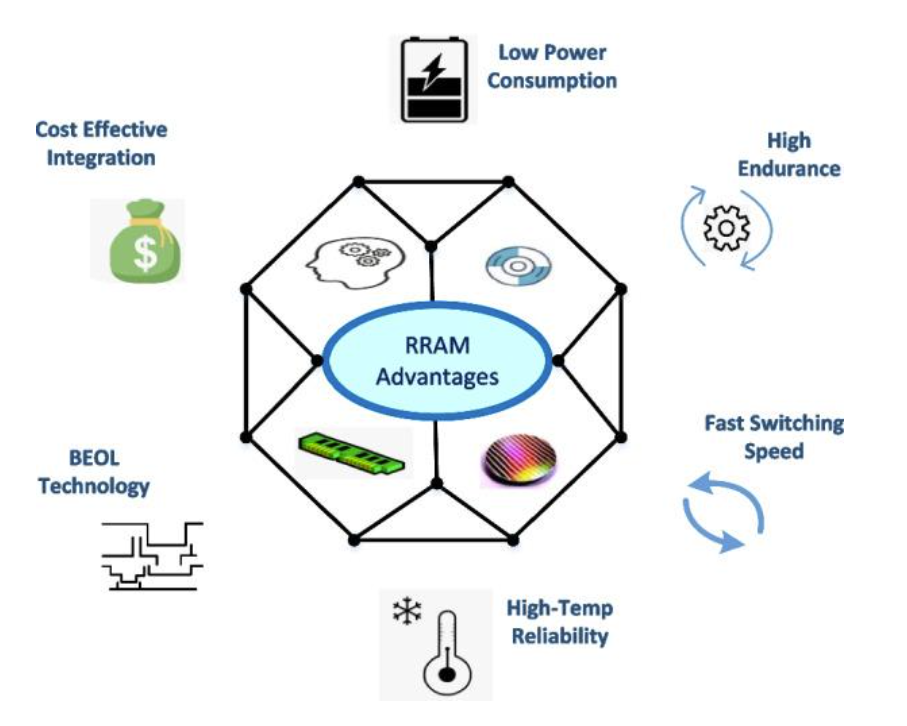

RRAM的歷史發展

RRAM設備的研究最初始于20世紀60年代初,將電阻性切換歸功于Hickmott。當時,電阻性切換現象在多種氧化物材料中得到報告。然而,隨后幾年對電阻性切換現象的研究并沒有取得突破。直到2000年,休斯頓大學的研究人員觀察到了磁電阻薄膜中的電阻性切換現象,重新點燃了對RRAM研究的熱情。2002年,Zhuang等人報道了基于Pr0.7Ca0.3MnO3的64位RRAM陣列。在2004年至2007年期間,英飛凌和三星的研究團隊取得了顯著的研究成果,首次展示了3D RRAM陣列。在2004年,三星展示了一個基于二元過渡金屬氧化物的簡單RRAM,完全集成了0.18微米CMOS技術。2008年,惠普的Strukov等人發表了《自然》雜志上的論文,擴展了RRAM的用途,被認為是RRAM發展的轉折點。2010年,unity半導體成功展示了64MB的RRAM原型測試芯片。接下來的幾年里,SanDisk/東芝展示了24納米技術的32Gb RRAM存儲器設備,而Micron/索尼展示了27納米技術的16Gb RRAM原型。2016年,中國科學院微電子研究所的Qing等人報告了超低功耗的三維垂直十字形RRAM陣列。2020年,TSMC宣布在40納米和22納米節點上生產RRAM。2021年9月,Weebit Nano與美國Skywater達成協議,將RRAM技術投入量產。Weebit Nano生產的ReRAM被稱為成本效益高、在高溫范圍內具有增強的耐久性和保留性、對輻射和電磁場具有容忍性,并且不會對前端模擬組件造成干擾。RRAM發展歷史上最重要的事件詳細列在圖2所示的時間軸圖中。

1962年至2021年RRAM的發展史

2022 年 2 月,《電子周刊》發表的文章提到,IMEC 與 Intrinsic Semiconductor Technologies 合作,成功擴展了其基于氧化硅的 RRAM,并展示了理想的特性,從而為邏輯器件中非易失性存儲器的成本效益和增強性能鋪平了道路。用于邊緣人工智能和物聯網應用的先進處理節點。最近,2022 年 8 月,斯坦福大學工程師推出了一款名為“NeuRRAM”的新型 RRAM 芯片,該芯片在內存中具有 AI 處理能力,從而無需單獨的計算和內存單元。這篇發表在 Nature 上的文章聲稱該芯片只有指尖大小,比當前最先進的芯片具有更多的處理能力和更少的電池消耗。

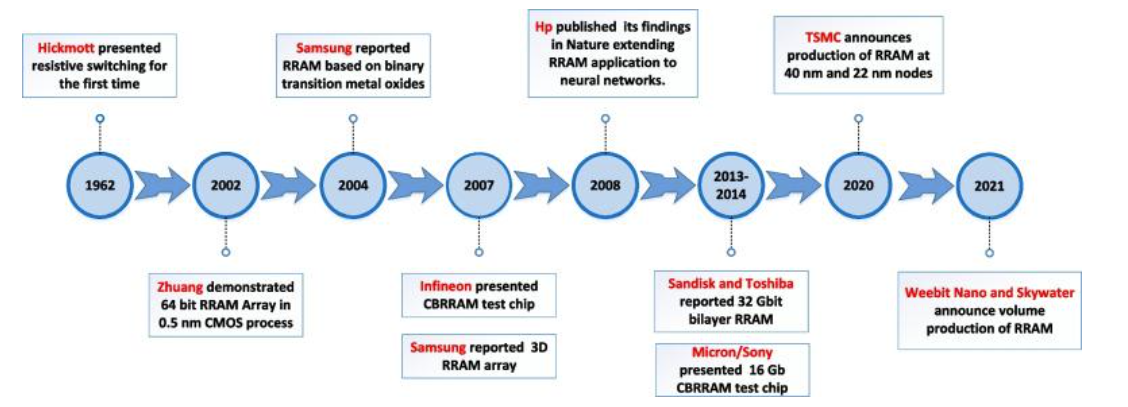

RRAM設計和物理機制

RRAM的器件結構是簡單的金屬-絕緣體-金屬(MIM)結構,類似電容器,其中的切換層夾在兩個金屬電極之間。RRAM細胞的示意圖如圖3所示。MIM結構的電阻可以通過施加適當的電信號而改變,并且設備會保持當前的電阻狀態,直到施加適當的信號以改變其電阻,代表了器件的非易失性質[37, 38]。由于RRAM器件的簡單結構,它可以輕松集成在帶有4F2(F是最小特征尺寸)的無源十字陣列中,并且可以在垂直堆疊的三維(3D)架構內將尺寸進一步減小至4F2/n(n是十字陣列的堆疊層數)。

RRAM 金屬-絕緣體-金屬結構示意圖

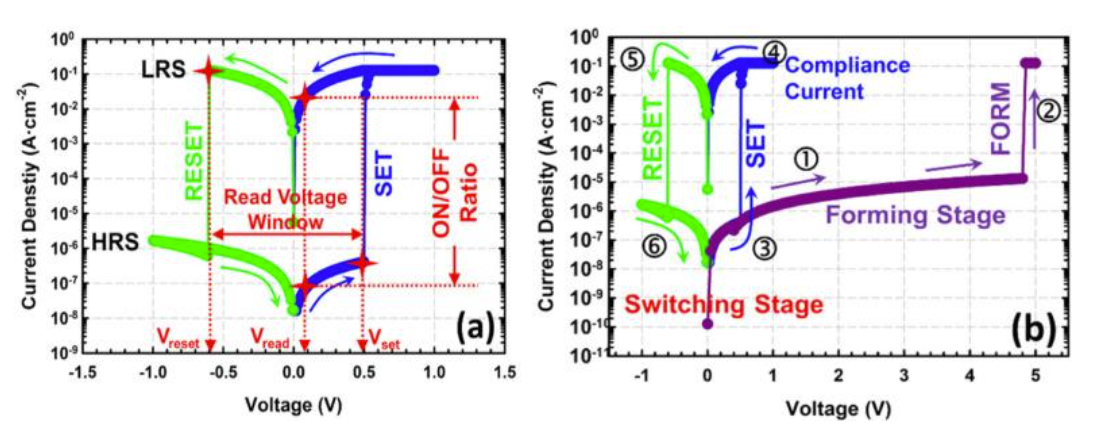

在RRAM中,通過在電極之間施加外部電壓脈沖來改變器件的電阻。RRAM背后的固有物理現象是電阻性轉換(RS),這意味著在外部電刺激下,設備可以自由地編程為高電阻狀態(HRS,或關斷狀態)或低電阻狀態(LRS,或通斷狀態)。傳統的存儲器件以二進制形式存儲數據,“0”代表未存儲的數據,“1”代表已存儲的數據。RRAM設備利用氧化和還原等氧化還原反應來進行有效的數據存儲,在這種反應中,氧化還原反應在絕緣體內形成導電絲(CF)在兩個金屬電極之間。由于外部電脈沖的作用,導電絲在RRAM的兩個金屬電極之間形成,設備被認為處于低電阻狀態(LRS),通常稱為邏輯狀態“1”。當導電絲破裂時,設備被認為處于高電阻狀態(HRS),通常稱為邏輯狀態“0”。圖4顯示了RRAM的操作機制的示意流程圖。

RRAM 的電流-電壓圖。b包含成型階段的典型 I-V 特性

RRAM 的三維 (3D) 集成

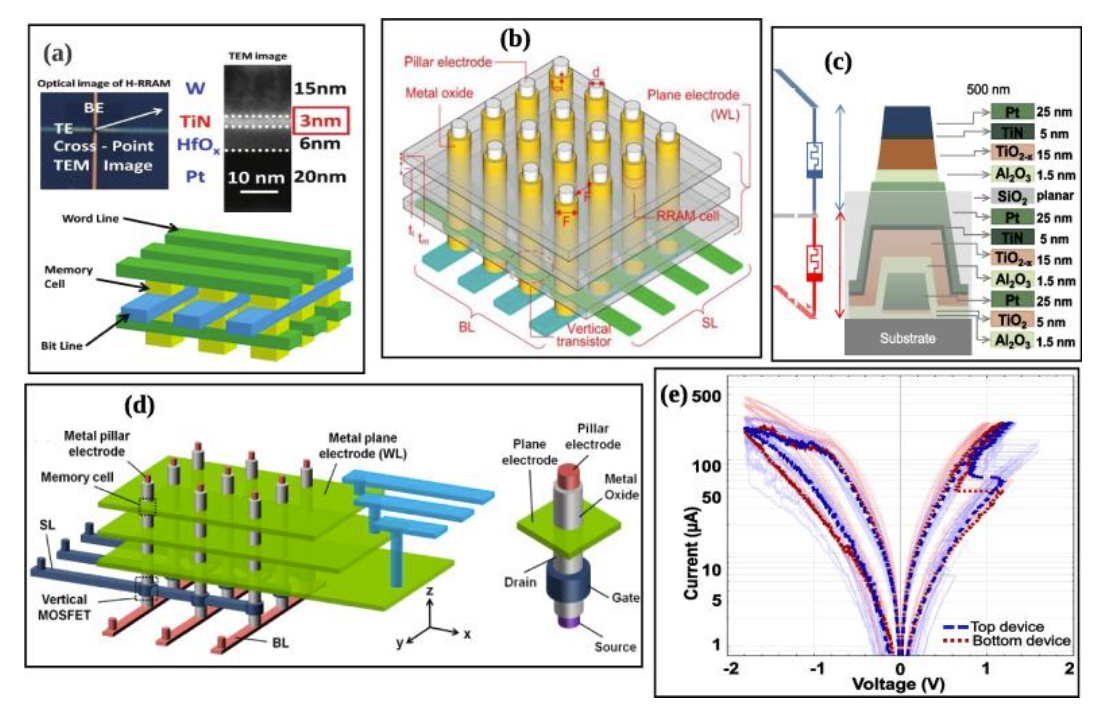

3D計算結構排列顯著提高了存儲器的能耗和帶寬訪問。近年來,已經在單個器件級別對許多垂直RRAM架構進行了實驗研究,它們似乎是很有前途的。然而,要完全實現3D存儲系統,需要解決許多基本技術問題,其中一些包括低電阻銅互連與低介電層之間的問題,由于晶體管互連導致的熱預算不兼容。因此,需要評估3D RRAM系統在陣列級別的性能。已經提出了幾種建模方法來研究基于寫入/讀取方案設計、幾何縮放趨勢以及器件參數等的3D RRAM結構。

圖a顯示了3D水平RRAM陣列。3D垂直RRAM陣列被視為一組垂直排列的2D平面,通常由選擇線(SL)選擇,如圖b所示。解碼通常由SL、位線(BL)和字線(WL)完成。每個垂直電極的邊緣與一個WL相連。柱體與陣列底部的BL連接。用于操作與柱體電極串聯的垂直晶體管的SL。然而,對于特定蝕刻橫徑比(AR)的3D排列,最大高度限制可在已知特征尺寸(F)時計算;當柱體電極的直徑(d)加上兩倍的RRAM絕緣氧化物厚度(tox)時,可以確定F;此外,F被視為相鄰柱體電極中心之間距離的一半。因此,每個層由一個厚度為(tm)的平面電極和一個厚度為(ti)的分離層組成。利用電阻率和這些幾何因素,可以計算平面和柱狀互連的電阻。利用位成本可擴展(BICS)技術,將3D垂直RRAM架構用于將存儲單元放置在平面電極和垂直柱體之間作為3D NAND閃存的替代方案。

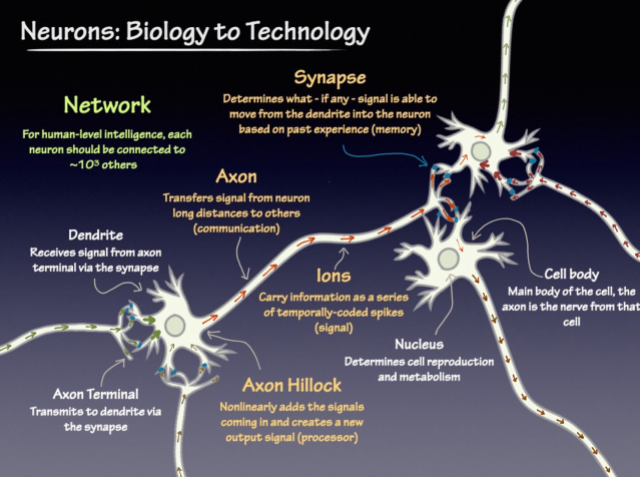

基于RRAM的神經形態計算的原型

傳統上,RRAM可以實現存儲和存儲器設備的目標。在RRAM中發生模擬或突變的切換。這種類型的切換在需要準確的導電變化的神經形態學應用中非常重要。為了解決與人工智能相關的問題,將RRAM與CMOS技術集成可以被證明非常有效。神經形態計算架構需要低功耗和高密度的結構,每個單元至少具有5位/單元的存儲。基于RRAM的神經網絡的原型,采用Ag摻雜SiO

審核編輯 黃宇

-

芯片

+關注

關注

450文章

49650瀏覽量

417263 -

存儲器

+關注

關注

38文章

7366瀏覽量

163105 -

RRAM

+關注

關注

0文章

26瀏覽量

21320

發布評論請先 登錄

相關推薦

神經形態芯片作為AI加速器正式神經形態基準鋪平道路

光頡(Viking)合金電流采樣電阻,毫歐電阻的參數范圍及其特點,材料及應用

被稱為“第五代 AI”的神經形態計算進展到哪一步了?精選資料分享

軟磁材料及其半成品

納米結構材料及其技術在太陽能電池中的應用和發展現狀

Gartner預測:標記神經形態計算和DNA存儲時代很快到來

為人工智能計算提供神經形態芯片的案例

RRAM機制、材料及其在神經形態計算中的應用

RRAM機制、材料及其在神經形態計算中的應用

評論