串行調(diào)試(Serial Wire Debug)接口,SWD是ARM目前支持的兩種調(diào)試端口之一,其用于實現(xiàn)微控制器與調(diào)試器之間的通信。SWD僅需4pin的2.54排針加上4根線就能完成程序的燒寫與調(diào)試,而且ST-LINK的價格也很便宜。

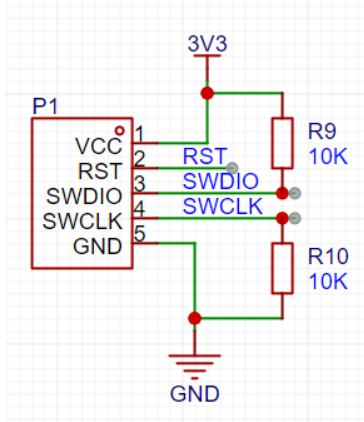

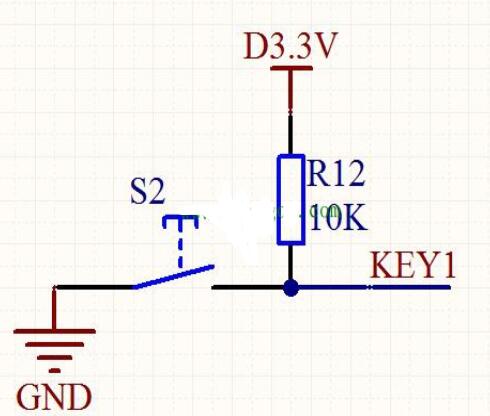

如上圖所示,一般我們都會這樣設(shè)計SWD接口,但是為什么SWDIO需要10K電阻上拉?SWCLK為什么需要10K電阻下拉?

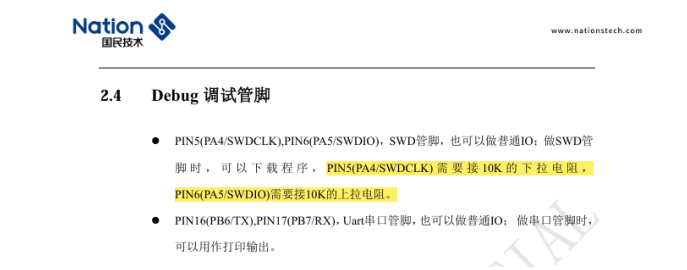

我們先來參照一下國民技術(shù)的《N32WB03x 系列芯片硬件設(shè)計指南》:

這里明確指出SWDIO和SWCLK需要上拉和下拉。

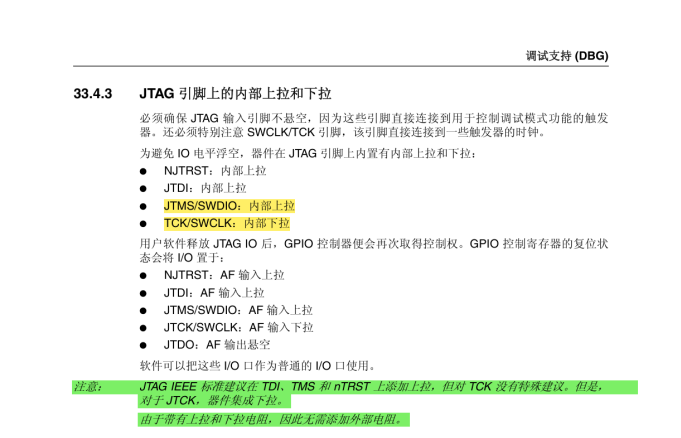

再來看看《STM32F4xx中文參考手冊》

在這里,SWDIO和SWCLK內(nèi)部已經(jīng)有上拉和下拉了。對于SWDIO,在芯片內(nèi)部已經(jīng)有上拉,在電路板上也必須再一次上拉;而對于SWCLK,在芯片內(nèi)部已經(jīng)有下拉,沒有特殊說明則不需要再下拉。

對于STM32的SWCLK和SWDIO引腳在設(shè)計上內(nèi)部通常帶有弱上拉和下拉電阻,這意味著在某些情況下,不額外添加外部上下拉電阻也可以正常工作。而其他一些MCU則需要進(jìn)一步參照其數(shù)據(jù)手冊以確定,如國民技術(shù)的N32WB031KEQ6-2。

而我們也要明確一下上拉或下拉電阻的作用是什么?

首先,上下拉電阻可以在引腳未被驅(qū)動時(浮空),使其保證明確的狀態(tài)(上拉電阻使其保持高電平,下拉電阻使其保持低電平)。同時,上下拉電阻也能抑制噪聲,避免因噪聲而導(dǎo)致誤判。因此為了確保更好的信號完整性、降低噪聲干擾和提高通信可靠性,尤其是在長距離傳輸、嘈雜環(huán)境下,建議在設(shè)計時添加合適的上下拉電阻(10K或100K)。在實際應(yīng)用中,應(yīng)該多參照數(shù)據(jù)手冊以及使用環(huán)境決定是否添在SWDIO和SWCLK加上下拉電阻,但是為了以防萬一,研發(fā)和設(shè)計過程中板子上往往會預(yù)留下上下拉電阻的位置。

-

上拉電阻

+關(guān)注

關(guān)注

5文章

351瀏覽量

30406 -

下拉電阻

+關(guān)注

關(guān)注

4文章

143瀏覽量

20404 -

接口

+關(guān)注

關(guān)注

33文章

8150瀏覽量

149661

發(fā)布評論請先 登錄

相關(guān)推薦

電阻上下拉功能實現(xiàn)原理詳解

上下拉電阻有什么用

解釋一下上下拉電阻

上下拉電阻有什么用呢

深入淺出上拉電阻下拉電阻

上拉電阻、下拉電阻的一些理解

通俗理解:下載口的上下拉電阻

通俗理解:下載口的上下拉電阻

評論